Super BigBite DAQ & Trigger

Jens-Ole Hansen Hall A Collaboration Meeting 16 December 2009

### **SBS DAQ Requirements**

- Data rate driven by GEMs & Coordinate Detector

- $\approx 90,000$  channels, 4-8% occupancy, 2 bytes/channel  $- \approx 15$  kB event size @ 5 kHz = 75 MB/s

- Add other detectors, allow for higher rates, ... ⇒ must handle ≈100 MB/s

- Far exceeds current Hall A capabilities

- Need 12 GeV DAQ upgrade to meet the requirements

- Plan exists for Hall A

- <u>http://hallaweb.jlab.org/equipment/dag/dag\_12gev.pdf</u>

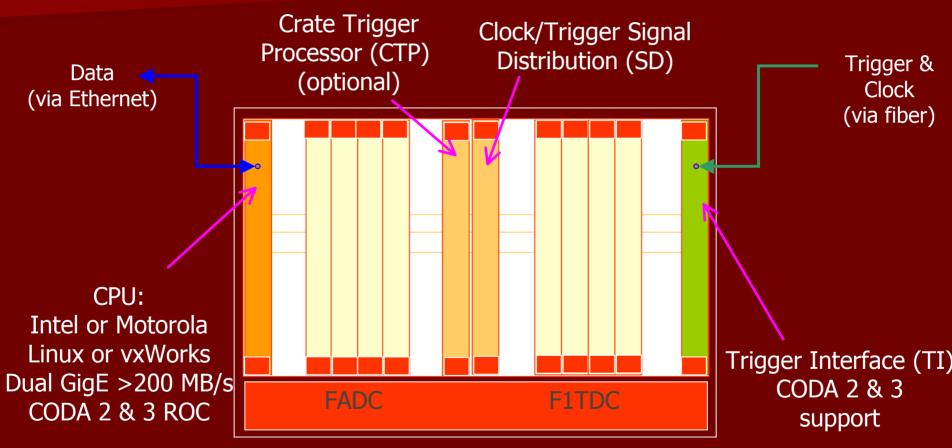

# 12 GeV Upgrade DAQ Electronics

- Fully pipelined

- 200 kHz L1 trigger rate capability

- VME64x front-end crates with support for

- High-speed readout modes (2eVME, 2eSST) up to 200 MB/s

- Event "blocking" (buffering, caching) up to 200 events

- Custom serial (VXS) backplane bus:

- Bi-directional trigger path

- Optional data path

- (Trunked) Gigabit Ethernet or fiber uplinks to event builder

- Synchronous trigger distribution, 250 MHz ref. Clock

- SBS will use some of this technology + custom modules

# **Future Front Ends**

(graphics from Dave Abbott)

VME64x/VXS Crate

# SBS Trigger Considerations

#### GMn and GEn(2)

- BigBite with gas Cherenkov and shower: ≤ 3 kHz singles. Use as is (for both arms). No need for hardware coincidence.

- GEp(5): elastic H(e,e'p)

- $\approx 60$  kHz singles in electron arm (BigCal)

- $\approx 1.5$  MHz singles in proton arm (SBS)

- $\Rightarrow \ge 5$  kHz raw coincidence rate. Too high.

- $\Rightarrow$  take advantage of spatial correlations in elastic scattering to build intelligent coincidence logic

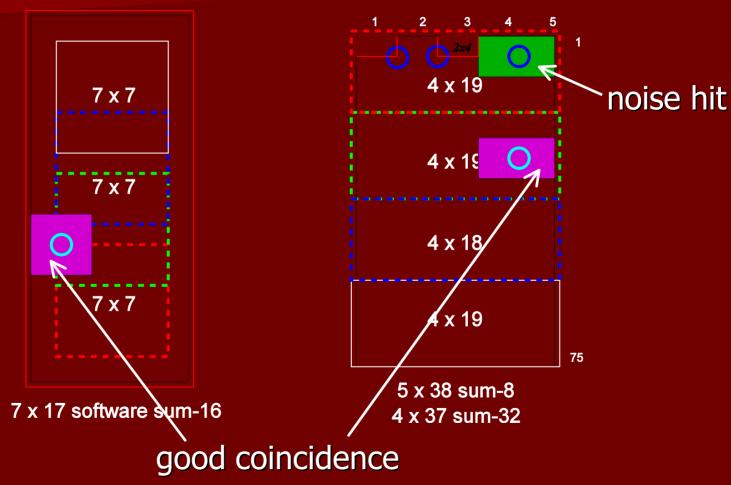

# GEp(5) Spatial-Correlations Trigger

#### Level 1

- -≈100 ns

- "Mark" samples in APV-25 GEM readouts

- Gate Fastbus & VME

- Generated by electron arm ( $\approx$ 60 kHz rate)

- Level 2

- ≈3 µs

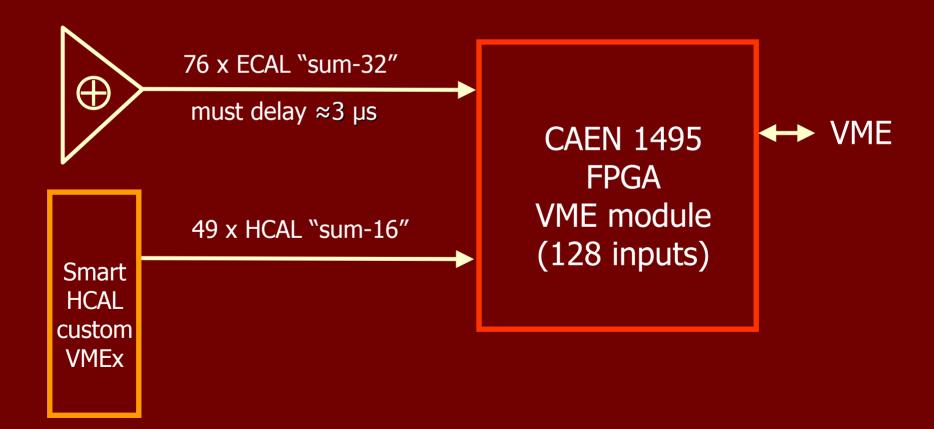

- Use FPGAs to detect spatial correlations between ECAL and HCAL calorimeters

- Reduces rate by factor of 5

- Fast Clear FB & VME after L2 timeout  $\Rightarrow$  < 20% DT

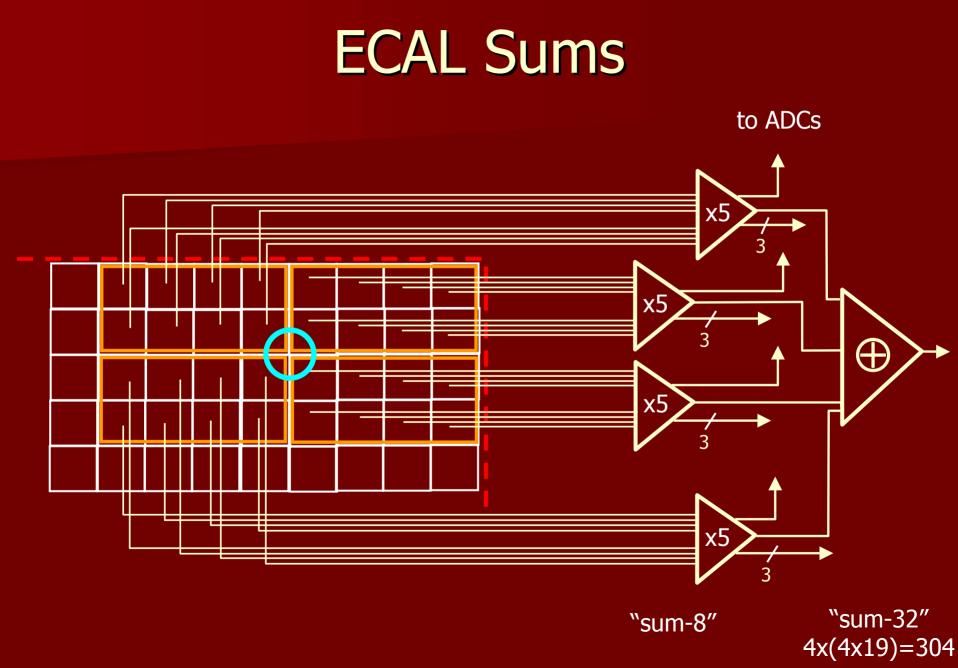

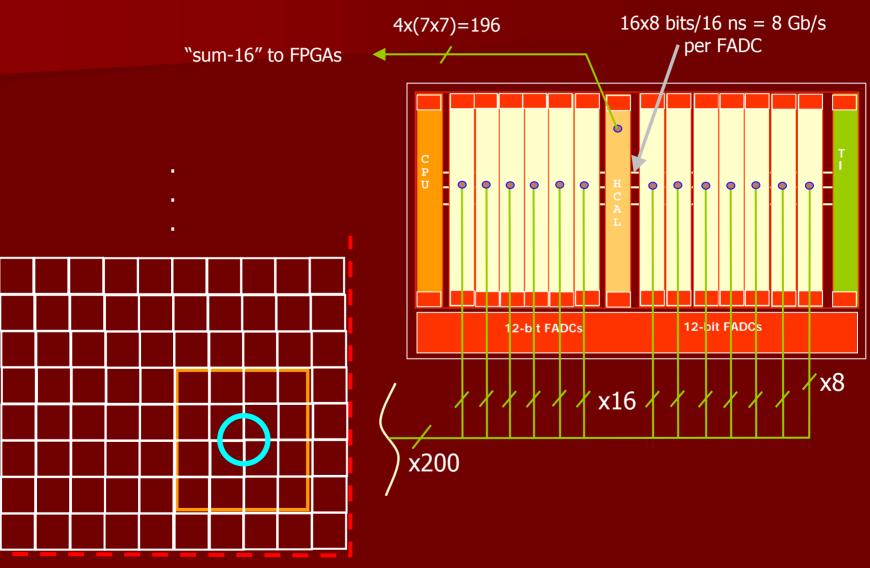

# GEp(5) Calorimeter Sums

10 x 20 HCAL blocks

20 x 75 ECAL blocks

### **HCAL Sums**

### **FPGA** Coincidence Logic

For each calorimeter section (4x):

### Conclusions

#### SBS Data Acquisition rather challenging

- Up to 100 MB/s data rate

- Pipelined electronics

- Custom modules

- GEp(5) Trigger similarly challenging

- Digital summing logic for HCAL

- FPGA coincidence logic

- Need experience, R&D