#### Testing of LeCroy 1877S TDCs

Eric Jensen (W&M) Hall A Group Meeting November 29, 2011

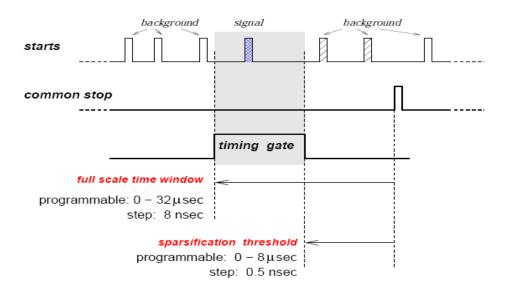

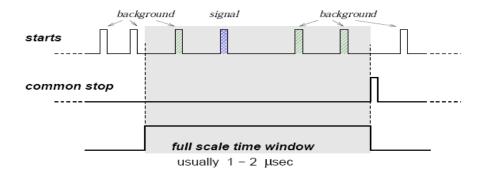

## Sparsification

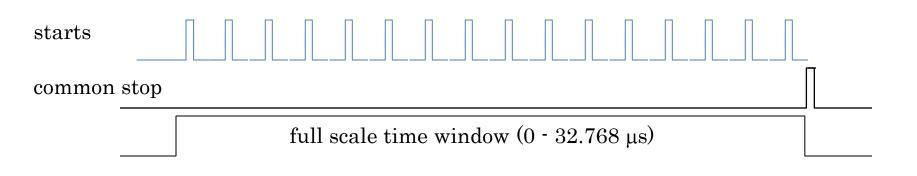

1877S TDC running in common stop mode **without sparsification**

Constantly accepting start signals

When STOP arrives it looks back the length of the full scale time window to find all signals inside of the window

#### 1877S TDC running in common stop mode with sparsification

Still a full scale time window

Sparsification threshold which gives the TDC a time after which no new start signals should be recorded

### Why Sparsification?

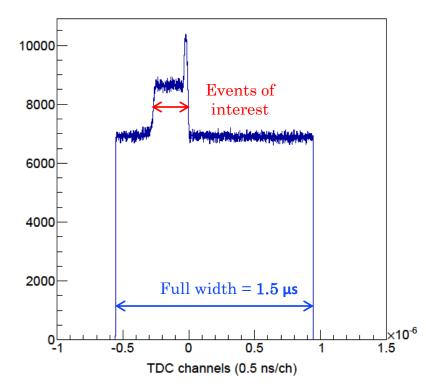

LHRS VDC TDC spectrum during APEX

•Reduces deadtime

•Reduces quantity of undesired data

BigBite TDC spectrum is even worse!

Region of interest is only 10% of total spectrum

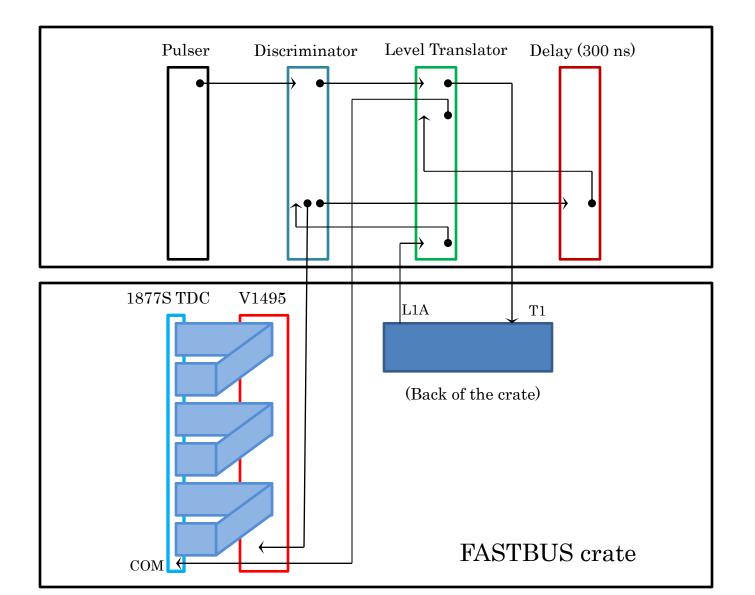

## Test Setup

#### Readout Lists and Configurations

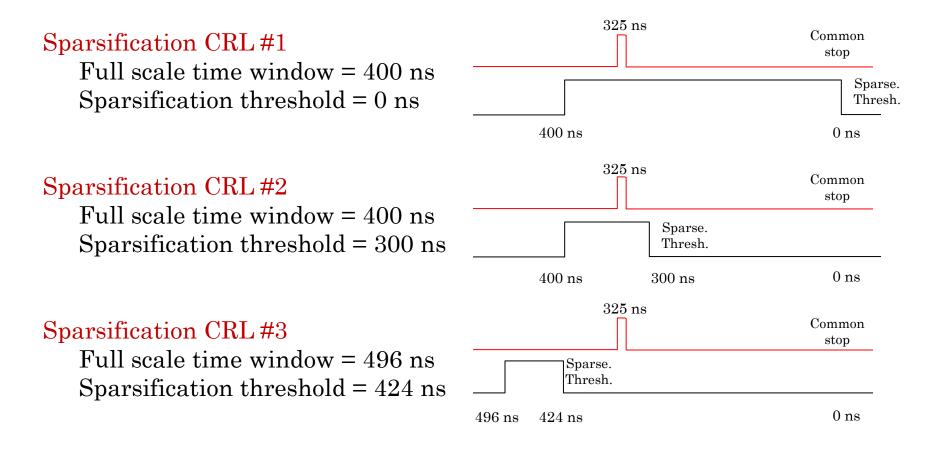

Each TDC is tested with 3 different CRLs (CODA Readout Lists)

Common stop from pulser is delayed by 325 ns

#### Results

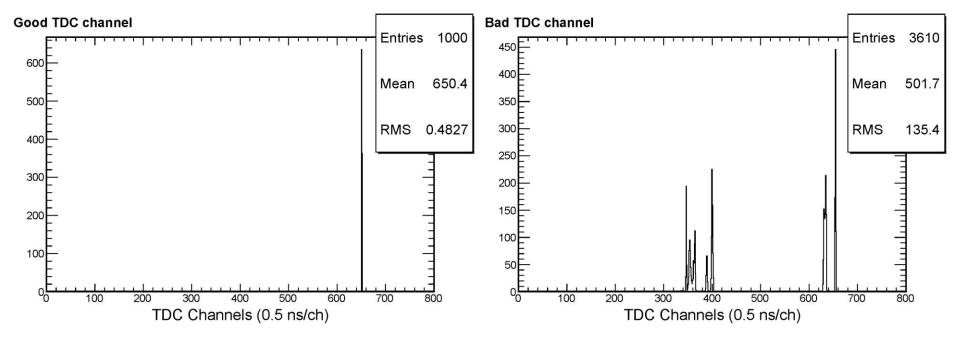

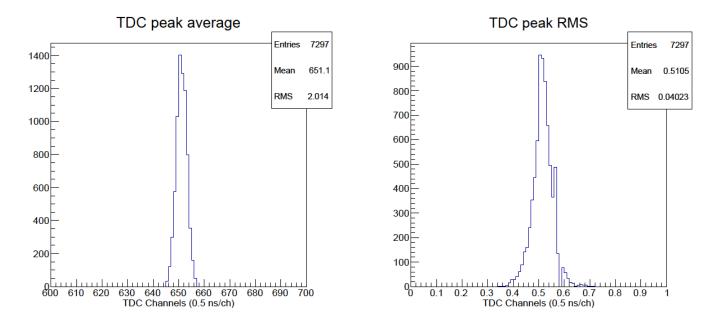

- The first 2 sparsification tests should provide each TDC channel with a sharp peak around 650 (325 ns) containing exactly 1000 events

- A TDC channel is considered to be bad if it has:

- Extra or missing events

- An RMS value > 0.8 channels

- A peak location outside of the range 640-660 channels

- The TDC channels should see 0 hits for the 3<sup>rd</sup> test

- A total of 42 TDCs have been fully tested, out of which 4 have bad channels

#### Results

All TDCs that have been tested have been labeled with new barcode labels.

Still have  $\sim 100$  TDCs that need testing.

Daniel Kirby Alexandre Camsonne Ben Raydo Bogdan Wojtsekhowski

#### Thank you!

## 1877S

- Provides 96 channels of time-to-digital conversion

- 0.5 ns least count

- Can be programmed to store 1 16 hits per channel within a 0 32.768 µs full scale window.

- Selected edges can be detected with as little as 10 ns between them

#### Capable of running in sparsification mode

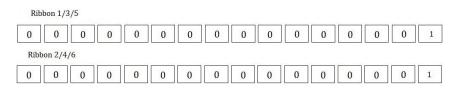

# V1495 FPGA Output

The FPGA (Field Programmable Gate Array) module accepts a pattern into an internal register

The pattern is then fired according to an incident pulse signal (in our case coming from the pulser)

Using A395C daughtercards to output ECL signals

Numerical Value: 65537

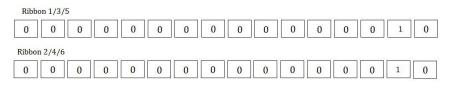

#### After 1000 events

Numerical Value: 131 074