# 8-Channel, 12-Bit, Configurable ADC/DAC with On-Chip Reference, I<sup>2</sup>C Interface

Data Sheet AD5593R

#### **FEATURES**

8-channel, configurable ADC/DAC/GPIO

Configurable as any combination of

8 12-bit DAC channels

8 12-bit ADC channels

8 general-purpose I/O pins

Integrated temperature sensor

16-lead TSSOP and LFCSP and 16-ball WLCSP packages

I<sup>2</sup>C interface

#### **APPLICATIONS**

Control and monitoring

General-purpose analog and digital I/O

#### **GENERAL DESCRIPTION**

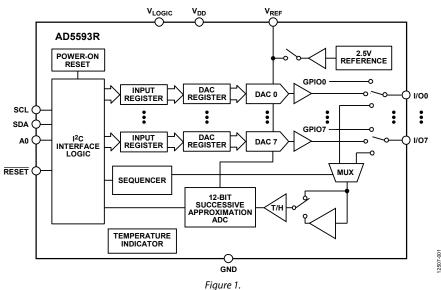

The AD5593R has eight input/output (I/O) pins, which can be independently configured as digital-to-analog converter (DAC) outputs, analog-to-digital converter (ADC) inputs, digital outputs, or digital inputs. When an I/O pin is configured as an analog output, it is driven by a 12-bit DAC. The output range of the DAC is 0 V to  $V_{REF}$  or 0 V to  $2 \times V_{REF}$ . When an I/O pin is configured as an analog input, it is connected to a 12-bit ADC via an analog multiplexer. The input range of the ADC is 0 V to  $V_{REF}$  or 0 V to  $V_{REF}$ . The I/O pins can also be configured to be general-purpose, digital input or output (GPIO) pins. The state of the GPIO pins can be set or read back by accessing the GPIO write data register and GPIO read configuration registers, respectively, via an  $I^2C$  write or read operation.

The AD5593R has an integrated 2.5 V, 20 ppm/°C reference that is turned off by default and an integrated temperature indicator that gives an indication of the die temperature. The temperature value is read back as part of an ADC read sequence.

The AD5593R is available in 16-lead TSSOP and LFCSP, as well as a 16-ball WLCSP, and operates over a temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C.

**Table 1. Related Products**

| Product   | Description                                                               |

|-----------|---------------------------------------------------------------------------|

| AD5592R   | AD5593R equivalent with SPI interface                                     |

| AD5592R-1 | $\label{eq:add_special} AD5593RequivalentwithSPIinterfaceandV_{LOGIC}pin$ |

#### **FUNCTIONAL BLOCK DIAGRAM**

Rev. B

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

# **AD5593R\* Product Page Quick Links**

Last Content Update: 11/01/2016

# Comparable Parts

View a parametric search of comparable parts

## Evaluation Kits <a> □</a>

· AD5593R Evaluation Board

# Documentation <a>□</a>

#### **Data Sheet**

• AD5593R: 8-Channel, 12-Bit, Configurable ADC/DAC with On-Chip Reference, I2C Interface Data Sheet

#### **User Guides**

UG-756: Evaluating the AD5593R: 8-Channel, 12-Bit, Configurable ADC/DAC with On-Chip Reference

## Tools and Simulations

• AD5593R IBIS Model

# Reference Designs

• CN0229

# Design Resources <a>□</a>

- AD5593r Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

## Discussions <a>□</a>

View all AD5593r EngineerZone Discussions

# Sample and Buy -

Visit the product page to see pricing options

# Technical Support -

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

# **TABLE OF CONTENTS**

| Features                                                                       | Serial Interface                                             |

|--------------------------------------------------------------------------------|--------------------------------------------------------------|

| Applications                                                                   | Write Operation21                                            |

| General Description                                                            | Read Operation21                                             |

| Functional Block Diagram                                                       | Pointer Byte23                                               |

| Revision History                                                               | Control Registers                                            |

| Specifications                                                                 | General-Purpose Control Register24                           |

| Timing Characteristics 6                                                       | Configuring the AD5593R25                                    |

| Absolute Maximum Ratings                                                       | DAC Write Operation                                          |

| Thermal Resistance                                                             | DAC Readback26                                               |

| ESD Caution                                                                    | ADC Operation27                                              |

| Pin Configuration and Function Descriptions 8                                  | GPIO Operation29                                             |

| Typical Performance Characteristics                                            | Power-Down/Reference Control                                 |

| Terminology                                                                    | Reset Function                                               |

| Theory of Operation                                                            | Applications Information                                     |

| DAC Section                                                                    | Microprocessor Interfacing                                   |

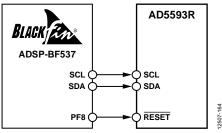

| ADC Section18                                                                  | AD5593R to ADSP-BF537 Interface31                            |

| GPIO Section                                                                   | Layout Guidelines31                                          |

| Internal Reference                                                             | Outline Dimensions                                           |

| Reset Function                                                                 | Ordering Guide                                               |

| Temperature Indicator                                                          |                                                              |

| REVISION HISTORY                                                               |                                                              |

| 1/16—Rev. A to Rev. B                                                          | 10/14—Rev. 0 to Rev. A                                       |

| Added 16-Lead LFCSPUniversal                                                   | Added 16-Ball WLCSPUniversal                                 |

| Added $V_{\text{LOGIC}}$ Parameter and $I_{\text{LOGIC}}$ Parameter, Table 2 5 | Changes to Gain Error Parameter, Table 13                    |

| Added Figure 4 and Table 7; Renumbered Sequentially 9                          | Changes to Table 57                                          |

| Added Calculating ADC Input Current Section and Figure 33 20                   | Added Figure 4 and Table 7; Renumbered Sequentially9         |

| Changes to Temperature Indicator Section                                       | Change to ADC Section                                        |

| Changes to Figure 34                                                           | Changes to Reset Function Section and Temperature            |

| Changes to Figure 35 and Figure 36                                             | Indicator Section                                            |

| Changes to Figure 37                                                           | Changes to Reset Function Section, Table 24, and Table 25 27 |

| Change to DAC Readback Section                                                 | Added Figure 41, Outline Dimensions                          |

| Changes to ADC Operation Section                                               | Updated Outline Dimensions                                   |

| Changes to Outline Dimensions                                                  | Changes to Ordering Guide                                    |

| Changes to Ordering Guide                                                      |                                                              |

# **SPECIFICATIONS**

$V_{\text{DD}}$  = 2.7 V to 5.5 V,  $V_{\text{REF}}$  = 2.5 V (internal),  $T_{\text{A}}$  =  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , unless otherwise noted.

Table 2.

| Parameter                                           | Min | Тур    | Max                        | Unit    | Test Conditions/Comments                                                        |

|-----------------------------------------------------|-----|--------|----------------------------|---------|---------------------------------------------------------------------------------|

| ADC PERFORMANCE                                     |     |        |                            |         | f <sub>IN</sub> = 10 kHz sine wave                                              |

| Resolution                                          |     | 12     |                            | Bits    |                                                                                 |

| Input Range <sup>1</sup>                            | 0   |        | $V_{REF}$                  | V       | ADC range select bit = 0                                                        |

|                                                     | 0   |        | $2 \times V_{REF}$         | V       | ADC range select bit = 1                                                        |

| Integral Nonlinearity (INL)                         | -2  |        | +2                         | LSB     |                                                                                 |

| Differential Nonlinearity (DNL)                     | -1  |        | +1                         | LSB     |                                                                                 |

| Offset Error                                        |     |        | ±5                         | mV      |                                                                                 |

| Gain Error                                          |     |        | 0.3                        | % FSR   |                                                                                 |

| Track Time (t <sub>TRACK</sub> ) <sup>2</sup>       | 500 |        |                            | ns      |                                                                                 |

| Conversion Time (t <sub>CONV</sub> ) <sup>2</sup>   |     |        | 2                          | μs      |                                                                                 |

| Signal to Noise Ratio (SNR) <sup>3</sup>            |     | 69     |                            | dB      | $V_{DD} = 2.7 \text{ V, input range} = 0 \text{ V to } V_{REF}$                 |

| orginal to reasonate (or my                         |     | 67     |                            | dB      | $V_{DD} = 5.5 \text{ V, input range} = 0 \text{ V to } V_{REF}$                 |

|                                                     |     | 61     |                            | dB      | $V_{DD} = 5.5 \text{ V}$ , input range = 0 V to 2 × $V_{REF}$                   |

| Signal-to-Noise + Distortion (SINAD)                |     | 69     |                            | dB      | $V_{DD} = 2.7 \text{ V, input range} = 0 \text{ V to } 2 \times \text{V_{REF}}$ |

| Ratio                                               |     | 0)     |                            | ub.     | Vbb = 2.7 V, input range = 0 V to Vker                                          |

|                                                     |     | 67     |                            | dB      | $V_{DD} = 3.3 \text{ V, input range} = 0 \text{ V to } V_{REF}$                 |

|                                                     |     | 60     |                            | dB      | $V_{DD} = 5.5 \text{ V}$ , input range = 0 V to 2 × $V_{REF}$                   |

| Total Harmonic Distortion (THD)                     |     | -91    |                            | dB      | $V_{DD} = 2.7 \text{ V, input range} = 0 \text{ V to } V_{REF}$                 |

| rotarriame distortion (1715)                        |     | -89    |                            | dB      | $V_{DD} = 3.3 \text{ V, input range} = 0 \text{ V to } V_{REF}$                 |

|                                                     |     | -72    |                            | dB      | $V_{DD} = 5.5 \text{ V}$ , input range = 0 V to 2 × $V_{REF}$                   |

| Spurious Free Dynamic Range (SFDR)                  |     | 91     |                            | dB      | $V_{DD} = 2.7 \text{ V, input range} = 0 \text{ V to } V_{REF}$                 |

| spanous rice by namic hange (si bil)                |     | 91     |                            | dB      | $V_{DD} = 3.3 \text{ V, input range} = 0 \text{ V to V}_{REF}$                  |

|                                                     |     | 72     |                            | dB      | $V_{DD} = 5.5 \text{ V}$ , input range = 0 V to 2 × $V_{REF}$                   |

| Aperture Delay <sup>2</sup>                         |     | 15     |                            | ns      | $V_{DD} = 3.5 \text{ V, in partial igc} = 0.7 \text{ to } 2.7 \text{ V}_{REF}$  |

| Aperture belay                                      |     | 12     |                            | ns      | $V_{DD} = 5 \text{ V}$                                                          |

| Aperture Jitter <sup>2</sup>                        |     | 50     |                            | ps      | V <sub>DD</sub> = 3 V                                                           |

| Channel-to-Channel Isolation                        |     | -95    |                            | dB      | f <sub>IN</sub> = 5 kHz                                                         |

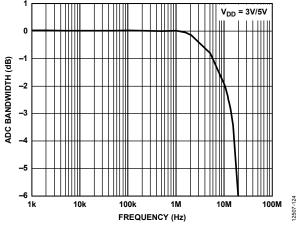

| Full Power Bandwidth                                |     | 8.2    |                            | MHz     | At 3 dB                                                                         |

| Tuil Tower Ballawiath                               |     | 1.6    |                            | MHz     | At 0.1 dB                                                                       |

| DAC PERFORMANCE <sup>4</sup>                        |     | 1.0    |                            | 1411.12 | ACO.1 GB                                                                        |

| Resolution                                          |     | 12     |                            | Bits    |                                                                                 |

|                                                     |     | 12     | $V_{REF}$                  | V       | DAC range select bit = 0                                                        |

| Output Range                                        | 0   |        | $v_{REF}$<br>2 × $V_{REF}$ | V       | _                                                                               |

| INL                                                 | 0   |        |                            |         | DAC range select bit = 1                                                        |

|                                                     | -1  |        | +1                         | LSB     |                                                                                 |

| DNL                                                 | -1  |        | +1                         | LSB     |                                                                                 |

| Offset Error                                        | -3  | 0      | +3                         | mV      |                                                                                 |

| Offset Error Drift <sup>2</sup>                     |     | 8      |                            | μV/°C   | 0.10.1000000000000000000000000000000000                                         |

| Gain Error                                          |     |        | ±0.2                       | % FSR   | Output range = 0 V to V <sub>REF</sub>                                          |

|                                                     |     |        | ±0.1                       | % FSR   | Output range = $0 \text{ V}$ to $2 \times V_{REF}$                              |

| Zero Code Error                                     |     | 0.65   | 2                          | mV      |                                                                                 |

| Total Unadjusted Error (TUE)                        |     | ±0.03  | ±0.25                      | % FSR   | Output range = $0 \text{ V to V}_{REF}$                                         |

|                                                     |     | ±0.015 | ±0.1                       | % FSR   | Output range = $0 \text{ V to } 2 \times V_{REF}$                               |

| Capacitive Load Stability                           |     |        | 2                          | nF<br>_ | $R_{LOAD} = \infty$                                                             |

|                                                     |     |        | 10                         | nF      | $R_{LOAD} = 1 \text{ k}\Omega$                                                  |

| Resistive Load                                      | 1   |        |                            | kΩ      |                                                                                 |

| Short-Circuit Current                               |     | 25     |                            | mA      |                                                                                 |

| DC Crosstalk <sup>2</sup>                           | -4  |        | +4                         | μV      | Single channel, full-scale output change                                        |

| DC Output Impedance                                 |     | 0.2    |                            | Ω       |                                                                                 |

| DC Power Supply Rejection Ratio (PSRR) <sup>2</sup> |     | 0.15   |                            | mV/V    | DAC code = midscale, $V_{DD}$ = 3 V ± 10% or 5 V ± 10%                          |

| Load Impedance at Rails⁵                            |     | 25     |                            | Ω       |                                                                                 |

| Parameter                                | Min                   | Тур  | Max                 | Unit     | Test Conditions/Comments                                                                               |

|------------------------------------------|-----------------------|------|---------------------|----------|--------------------------------------------------------------------------------------------------------|

| Load Regulation                          |                       | 200  |                     | μV/mA    | $V_{DD} = 5 \text{ V} \pm 10\%$ , DAC code = midscale, $-10 \text{ mA} \le I_{OUT} \le +10 \text{ mA}$ |

|                                          |                       | 200  |                     | μV/mA    | $V_{DD} = 3 \text{ V} \pm 10\%$ , DAC code = midscale, $-10 \text{ mA} \le l_{OUT} \le +10 \text{ mA}$ |

| Power-Up Time                            |                       | 7    |                     | μs       | Exiting power-down mode, $V_{DD} = 5 \text{ V}$                                                        |

| AC SPECIFICATIONS                        |                       |      |                     |          |                                                                                                        |

| Slew Rate                                |                       | 1.25 |                     | V/µs     |                                                                                                        |

| Settling Time                            |                       | 6    |                     | μs       |                                                                                                        |

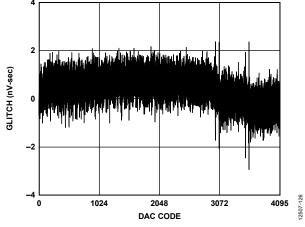

| DAC Glitch Impulse                       |                       | 2    |                     | nV-sec   |                                                                                                        |

| DAC to DAC Crosstalk                     |                       | 1    |                     | nV-sec   |                                                                                                        |

| Digital Crosstalk                        |                       | 0.1  |                     | nV-sec   |                                                                                                        |

| Analog Crosstalk                         |                       | 1    |                     | nV-sec   |                                                                                                        |

| Digital Feedthrough                      |                       | 0.1  |                     | nV-sec   |                                                                                                        |

| Multiplying Bandwidth                    |                       | 240  |                     | kHz      | DAC code = full scale, output range = $0 \text{ V}$ to $2 \times V_{REF}$                              |

| Output Voltage Noise Spectral Density    |                       | 200  |                     | nV/√Hz   | DAC code = midscale, output range = $0 \text{ V to } 2 \times V_{REF}$ ,                               |

| SNR                                      |                       | 81   |                     |          | measured at 10 kHz                                                                                     |

|                                          |                       |      |                     | dB       |                                                                                                        |

| SFDR                                     |                       | 77   |                     | dB       |                                                                                                        |

| SINAD                                    |                       | 74   |                     | dB       |                                                                                                        |

| Total Harmonic Distortion                |                       | -76  |                     | dB       |                                                                                                        |

| REFERENCE INPUT                          |                       |      | .,                  | 1,,      |                                                                                                        |

| V <sub>REF</sub> Input Voltage           | 1                     |      | $V_{DD}$            | ٧.       |                                                                                                        |

| DC Leakage Current                       | -1                    |      | +1                  | μΑ       | No I/Ox pins configured as DACs                                                                        |

| V <sub>REF</sub> Input Impedance         |                       | 12   |                     | kΩ       | DAC output range = $0 \text{ V to } 2 \times V_{REF}$                                                  |

|                                          |                       | 24   |                     | kΩ       | DAC output range = $0 \text{ V to V}_{REF}$                                                            |

| REFERENCE OUTPUT                         |                       |      |                     |          |                                                                                                        |

| V <sub>REF</sub> Output Voltage          | 2.495                 | 2.5  | 2.505               | V        |                                                                                                        |

| V <sub>REF</sub> Temperature Coefficient |                       | 20   |                     | ppm/°C   |                                                                                                        |

| Capacitive Load Stability                |                       | 5    |                     | μF       | $R_{LOAD} = 2 k\Omega$                                                                                 |

| Output Impedance                         |                       | 0.15 |                     | Ω        | $V_{DD} = 2.7 \text{ V}$                                                                               |

|                                          |                       | 0.7  |                     | Ω        | $V_{DD} = 5 \text{ V}$                                                                                 |

| Output Voltage Noise                     |                       | 10   |                     | μV p-p   | 0.1 Hz to 10 Hz                                                                                        |

| Density                                  |                       | 240  |                     | nV/√Hz   | At ambient, $f = 1 \text{ kHz}$ , $C_L = 10 \text{ nF}$                                                |

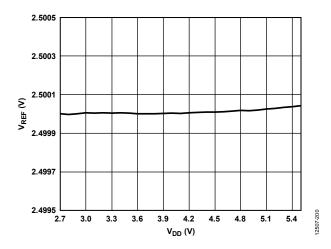

| Line Regulation                          |                       | 20   |                     | μV/V     | At ambient, sweeping V <sub>DD</sub> from 2.7 V to 5.5 V                                               |

|                                          |                       | 10   |                     | μV/V     | At ambient, sweeping V <sub>DD</sub> from 2.7 V to 3.3 V                                               |

| Load Regulation                          |                       |      |                     |          |                                                                                                        |

| Sourcing                                 |                       | 210  |                     | μV/mA    | At ambient, −5 mA ≤ load current ≤ +5 mA                                                               |

| Sinking                                  |                       | 120  |                     | μV/mA    | At ambient, −5 mA ≤ load current ≤ +5 mA                                                               |

| Output Current Load Capability           |                       | ±5   |                     | mA       | V <sub>DD</sub> ≥ 3 V                                                                                  |

| GPIO OUTPUT                              |                       |      |                     |          |                                                                                                        |

| Isource and Isink                        |                       | 1.6  |                     | mA       |                                                                                                        |

| Output Voltage                           |                       |      |                     |          |                                                                                                        |

| High, V <sub>он</sub>                    | V <sub>DD</sub> - 0.2 |      |                     | V        | I <sub>SOURCE</sub> = 1 mA                                                                             |

| Low, V <sub>OL</sub>                     |                       |      | 0.4                 | V        | I <sub>SOURCE</sub> = 1 mA                                                                             |

| GPIO INPUT                               |                       |      |                     | <u> </u> |                                                                                                        |

| Input Voltage                            |                       |      |                     |          |                                                                                                        |

| High, V <sub>IH</sub>                    | $V_{DD} \times 0.7$   |      |                     | V        |                                                                                                        |

| Low, V <sub>IL</sub>                     |                       |      | $V_{DD} \times 0.3$ | V        |                                                                                                        |

| Input Capacitance                        |                       | 20   | • 00 A 0.3          | pF       |                                                                                                        |

| Hysteresis                               |                       | 0.2  |                     | V        |                                                                                                        |

| Input Current                            |                       |      |                     |          |                                                                                                        |

| input Current                            | 1                     | ±1   |                     | μA       |                                                                                                        |

| Parameter                            | Min                    | Тур   | Max                    | Unit | Test Conditions/Comments                                                        |

|--------------------------------------|------------------------|-------|------------------------|------|---------------------------------------------------------------------------------|

| LOGIC INPUTS                         |                        |       |                        |      |                                                                                 |

| Input Voltage                        |                        |       |                        |      |                                                                                 |

| High, V <sub>INH</sub>               | $0.7 \times V_{LOGIC}$ |       |                        | V    |                                                                                 |

| Low, V <sub>INL</sub>                |                        |       | $0.3 \times V_{LOGIC}$ | ٧    |                                                                                 |

| Input Current, I <sub>IN</sub>       | -1                     | +0.01 | +1                     | μΑ   |                                                                                 |

| Input Capacitance, C <sub>IN</sub>   |                        |       | 10                     | pF   |                                                                                 |

| LOGIC OUTPUT (SDA)                   |                        |       |                        | ·    |                                                                                 |

| Output High Voltage, V <sub>OH</sub> | $V_{LOGIC} - 0.2$      |       |                        | ٧    | $I_{SOURCE} = 200 \mu\text{A};  V_{DD} = 2.7 \text{V} \text{ to } 5.5 \text{V}$ |

| Output Low Voltage, Vol              |                        |       | 0.4                    | ٧    | I <sub>SINK</sub> = 200 μA                                                      |

| Floating-State Output Capacitance    |                        | 10    |                        | pF   |                                                                                 |

| TEMPERATURE SENSOR <sup>2</sup>      |                        |       |                        |      |                                                                                 |

| Resolution                           |                        | 12    |                        | Bits |                                                                                 |

| Operating Range                      | -40                    |       | +105                   | °C   |                                                                                 |

| Accuracy                             |                        | ±3    |                        | °C   |                                                                                 |

| Track Time                           |                        |       | 5                      | μs   | ADC buffer enabled                                                              |

|                                      |                        |       | 20                     | μs   | ADC buffer disabled                                                             |

| POWER REQUIREMENTS                   |                        |       |                        | Pi S | The Council and the                                                             |

| VDD                                  | 2.7                    |       | 5.5                    | V    |                                                                                 |

| I <sub>DD</sub>                      | 2.7                    |       | 2.7                    | •    | Digital inputs = 0 V or V <sub>DD</sub>                                         |

| Power-Down Mode                      |                        |       | 3.5                    | μA   | Digital inputs = 0 v or v <sub>bb</sub>                                         |

| Normal Mode                          |                        |       | 5.5                    | μΛ   |                                                                                 |

| $V_{DD} = 5 \text{ V}$               |                        | 1.6   |                        | mA   | I/O0 to I/O7 are DACs, internal reference, gain = 2                             |

| <b>V</b> DD = <b>3 V</b>             |                        | 1.0   |                        | mA   | 1/00 to $1/07$ are DACs, external reference, gain = 2                           |

|                                      |                        | 2.4   |                        | mA   | I/O0 to I/O7 are DACs and sampled by the ADC,                                   |

|                                      |                        | 2.4   |                        | IIIA | internal reference, gain = 2                                                    |

|                                      |                        | 1.1   |                        | mA   | I/O0 to I/O7 are DACs and sampled by the ADC,                                   |

|                                      |                        |       |                        |      | external reference, gain = 2                                                    |

|                                      |                        | 1     |                        | mA   | I/O0 to I/O7 are ADCs, internal reference, gain = 2                             |

|                                      |                        | 0.75  |                        | mA   | I/O0 to I/O7 are ADCs, external reference, gain = 2                             |

|                                      |                        | 0.5   |                        | mA   | I/O0 to I/O7 are general-purpose outputs                                        |

|                                      |                        | 0.5   |                        | mA   | I/O0 to I/O7 are general-purpose inputs                                         |

| $V_{DD} = 3 \text{ V}$               |                        | 1.1   |                        | mA   | I/O0 to I/O7 are DACs, internal reference, gain = 1                             |

|                                      |                        | 1     |                        | mA   | I/O0 to I/O7 are DACs, external reference, gain = 1                             |

|                                      |                        | 1.1   |                        | mA   | I/O0 to I/O7 are DACs and sampled by the ADC,                                   |

|                                      |                        |       |                        |      | internal reference, gain = 1                                                    |

|                                      |                        | 0.78  |                        | mA   | I/O0 to I/O7 are DACs and sampled by the ADC, external reference, gain = 1      |

|                                      |                        | 0.75  |                        | mA   | 1/00 to 1/07 are ADCs, internal reference, gain = 1                             |

|                                      |                        | 0.5   |                        | mA   | I/O0 to I/O7 are ADCs, external reference, gain = 1                             |

|                                      |                        | 0.45  |                        | mA   | I/O0 to I/O7 are general-purpose outputs                                        |

|                                      |                        | 0.45  |                        | mA   | I/O0 to I/O7 are general-purpose inputs                                         |

| VLOGIC                               | 1.8                    |       | $V_{DD}$               | V    | 2 - 2 - 1 - 1 - 1 - 1 - 1                                                       |

| ILOGIC                               | 1.2                    |       | 3.5                    | μA   |                                                                                 |

$<sup>^{\</sup>rm 1}$  When using the internal ADC buffer, there is a dead band of 0 V to 5 mV.  $^{\rm 2}$  Guaranteed by design and characterization; not production tested.

<sup>3</sup> All specifications expressed in decibels are referred to full-scale input, FSR, and tested with an input signal at 0.5 dB below full scale, unless otherwise specified.

DC specifications tested with the outputs unloaded, unless otherwise noted. Linearity calculated using a reduced code range of 8 to 4085. An upper dead band of

<sup>10</sup> mV exists when  $N_{REF} = V_{DD}$ .

<sup>5</sup> When drawing a load current at either rail, the output voltage headroom with respect to that rail is limited by the 25  $\Omega$  typical channel resistance of the output devices. For example, when sinking 1 mA, the minimum output voltage = 25  $\Omega \times$  1 mA = 25 mV (see Figure 26 and Figure 27).

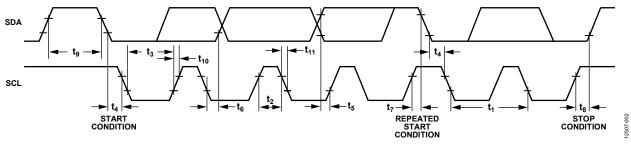

### **TIMING CHARACTERISTICS**

All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ ;  $V_{DD} = 2.7$  V to 5.5 V, 1.8 V  $\leq$  V<sub>LOGIC</sub>  $\leq$  V<sub>DD</sub>; 2.5 V  $\leq$  V<sub>REF</sub>  $\leq$  V<sub>DD</sub>; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 3.

| Parameter <sup>1</sup> | Min                 | Тур | Max | Unit | Conditions/Comments                                                   |

|------------------------|---------------------|-----|-----|------|-----------------------------------------------------------------------|

| t <sub>1</sub>         | 2.5                 |     |     | μs   | SCL cycle time                                                        |

| $t_2$                  | 0.6                 |     |     | μs   | t <sub>нібн</sub> , SCL high time                                     |

| t <sub>3</sub>         | 1.3                 |     |     | μs   | t <sub>LOW</sub> , SCL low time                                       |

| t <sub>4</sub>         | 0.6                 |     |     | μs   | thd,sta, start/repeated start condition hold time                     |

| <b>t</b> <sub>5</sub>  | 100                 |     |     | ns   | t <sub>SU,DAT</sub> , data setup time                                 |

| $t_6^2$                |                     |     | 0.9 | μs   | t <sub>HD,DAT</sub> , data hold time                                  |

| t <sub>7</sub>         | 0.6                 |     |     | μs   | t <sub>SU,STA</sub> , setup time for repeated start                   |

| t <sub>8</sub>         | 0.6                 |     |     | μs   | t <sub>SU,STO</sub> , stop condition setup time                       |

| t <sub>9</sub>         | 1.3                 |     |     | μs   | t <sub>BUF</sub> , bus free time between a stop and a start condition |

| t <sub>10</sub>        |                     |     | 300 | ns   | t <sub>R</sub> , rise time of SCL and SDA when receiving              |

|                        | 0                   |     |     | ns   | $t_{R_r}$ rise time of SCL and SDA when receiving (CMOS compatible)   |

| t <sub>11</sub>        |                     |     | 250 | ns   | t <sub>F</sub> , fall time of SDA when transmitting                   |

|                        | 0                   |     |     | ns   | t <sub>F</sub> , fall time of SDA when receiving (CMOS compatible)    |

|                        |                     |     | 300 | ns   | t <sub>F</sub> , fall time of SCL and SDA when receiving              |

|                        | $20 + 0.1C_{B}^{3}$ |     |     | ns   | t <sub>F</sub> , fall time of SCL and SDA when transmitting           |

| $C_B^3$                |                     |     | 400 | pF   | Capacitive load for each bus line                                     |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization; not production tested.

#### **Timing Diagram**

Figure 2. 2-Wire Serial Interface Timing Diagram

<sup>&</sup>lt;sup>2</sup> A master device must provide a hold time of at least 300 ns for the SDA signal (referred to the V<sub>H</sub> min of the SCL signal) to bridge the undefined region of the falling edge of SCL.

$<sup>^3</sup>$  C<sub>B</sub> is the total capacitance of one bus line in pF.  $t_R$  and  $t_F$  are measured between 0.3  $V_{DD}$  and 0.7  $V_{DD}$ .

## **ABSOLUTE MAXIMUM RATINGS**

$T_A$  = 25°C, unless otherwise noted. Transient currents of up to 100 mA do not cause SCR latch-up.

Table 4.

| Parameter                                 | Rating                                          |

|-------------------------------------------|-------------------------------------------------|

| V <sub>DD</sub> to GND                    | −0.3 V to +7 V                                  |

| V <sub>LOGIC</sub> to GND                 | -0.3 V to +7 V                                  |

| Analog Input Voltage to GND               | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$      |

| Digital Input Voltage to GND              | $-0.3 \text{ V to V}_{LOGIC} + 0.3 \text{ V}$   |

| Digital Output Voltage to GND             | $-0.3 \text{ V}$ to $V_{LOGIC} + 0.3 \text{ V}$ |

| $V_{REF}$ to GND                          | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$      |

| Operating Temperature Range               | -40°C to +105°C                                 |

| Storage Temperature Range                 | −65°C to +150°C                                 |

| Junction Temperature (T <sub>J</sub> max) | +150°C                                          |

| Lead Temperature                          | JEDEC industry-standard                         |

| Soldering                                 | J-STD-020                                       |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 5. Thermal Resistance**

| Package Type  | θја | Unit |

|---------------|-----|------|

| 16-Lead TSSOP | 112 | °C/W |

| 16-Lead LFCSP | 137 | °C/W |

| 16-ball WLCSP | 60  | °C/W |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

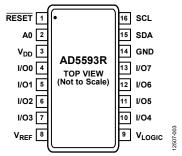

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

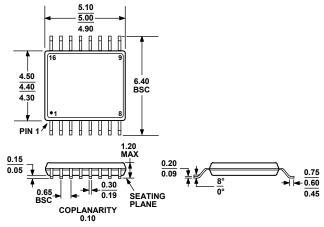

Figure 3. 16-Lead TSSOP Pin Configuration

**Table 6. 16-Lead TSSOP Pin Function Descriptions**

| Pin No.             | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                   | RESET              | Asynchronous Reset Pin. Tie this pin high for normal operation. When this pin is brought low, the AD5593R is reset to its default configuration.                                                                                                                                                                                                                                                                                   |

| 2                   | A0                 | Address Input. Sets the LSB of the 7-bit slave address.                                                                                                                                                                                                                                                                                                                                                                            |

| 3                   | $V_{DD}$           | Power Supply Input. The AD5593R can operate from 2.7 V to 5.5 V. Decouple the supply with a 0.1 µF capacitor to GND.                                                                                                                                                                                                                                                                                                               |

| 4 to 7,<br>10 to 13 | I/O0 to I/O7       | Input/Output 0 Through Input/Output 7. These pins can be independently configured as DACs, ADCs, or general-purpose digital inputs or outputs. The function of each pin is determined by programming the appropriate bits in the configuration registers.                                                                                                                                                                          |

| 8                   | V <sub>REF</sub>   | Reference Input/Output. When the internal reference is enabled, the 2.5 V reference voltage is available on the $V_{REF}$ pin. A 0.1 $\mu$ F capacitor connected from the $V_{REF}$ pin to GND is recommended to achieve the specified performance from the AD5593R. When the internal reference is disabled, an external reference must be applied to this pin. The voltage range for the external reference is 1 V to $V_{DD}$ . |

| 9                   | V <sub>LOGIC</sub> | Interface Power Supply. The voltage on this pin ranges from 1.8 V to 5.5 V.                                                                                                                                                                                                                                                                                                                                                        |

| 14                  | GND                | Ground Reference Point for All Circuitry.                                                                                                                                                                                                                                                                                                                                                                                          |

| 15                  | SDA                | Serial Data Input. This pin is used in conjunction with the SCL line to clock data in to or out of the input shift register. SDA is a bidirectional, open-drain line that must be pulled to the $V_{LOGIC}$ supply with an external pull-up resistor.                                                                                                                                                                              |

| 16                  | SCL                | Serial Clock Line. This pin is used in conjunction with the SDA line to clock data in to or out of the 16-bit input register.                                                                                                                                                                                                                                                                                                      |

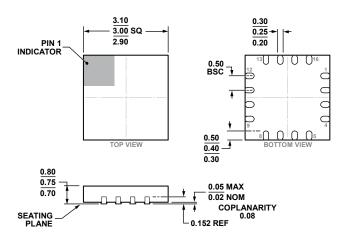

Figure 4. 16-Lead LFCSP Pin Configuration

Table 7. 16-Ball LFCSP Pin Function Descriptions

| Pin No.         | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | $V_{\text{DD}}$    | Power Supply Input. The AD5593R operates from 2.7 V to 5.5 V. Decouple the supply with a 0.1 µF capacitor to GND.                                                                                                                                                                                                                                                                                                                      |

| 2 to 5, 8 to 11 | I/O0 to I/O7       | Input/Output 0 through Input/Output 7. These pins can be independently configured as DACs, ADCs, or general-purpose digital inputs or outputs. The function of each pin is determined by programming the appropriate bits in the configuration registers.                                                                                                                                                                              |

| 6               | V <sub>REF</sub>   | Reference Input/Output. When the internal reference is enabled, the 2.5 V reference voltage is available on the pin. A 0.1 $\mu$ F capacitor connected from the V <sub>REF</sub> pin to GND is recommended to achieve the specified performance from the AD5593R. When the internal reference is disabled, an external reference must be applied to this pin. The voltage range for the external reference is 1 V to V <sub>DD</sub> . |

| 7               | V <sub>LOGIC</sub> | Interface Power Supply. The voltage ranges from 1.8 V to 5.5 V.                                                                                                                                                                                                                                                                                                                                                                        |

| 12              | GND                | Ground Reference Point for All Circuitry.                                                                                                                                                                                                                                                                                                                                                                                              |

| 13              | SDA                | Serial Data Input. This pin is used in conjunction with the SCL line to clock data into or out of the input shift register. SDA is a bidirectional, open-drain line that must be pulled to the V <sub>LOGIC</sub> supply with an external pull-up resistor.                                                                                                                                                                            |

| 14              | SCL                | Serial Clock Line. This is pin used in conjunction with the SDA line to clock data into or out of the 16-bit input register.                                                                                                                                                                                                                                                                                                           |

| 15              | RESET              | Asynchronous Reset Pin. Tie this pin high for normal operation. When this pin is brought low, the AD5593R is reset to its default configuration.                                                                                                                                                                                                                                                                                       |

| 16              | A0                 | Address Input. This pin sets the LSB of the 7-bit slave address.                                                                                                                                                                                                                                                                                                                                                                       |

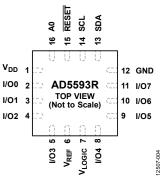

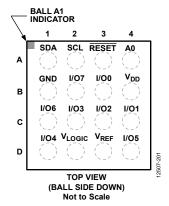

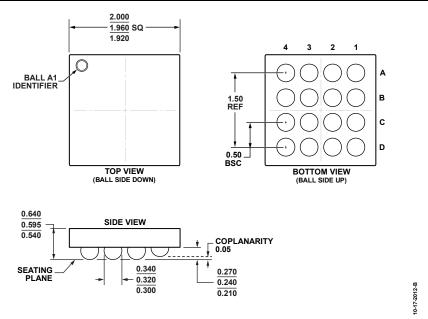

Figure 5. 16-Ball WLCSP Pin Configuration

Table 8. 16-Ball WLCSP Pin Function Descriptions

| Pin No.                              | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A3                                   | RESET              | Asynchronous Reset Pin. Tie this pin high for normal operation. When this pin is brought low, the AD5593R is reset to its default configuration.                                                                                                                                                                                                                                                                                       |

| A4                                   | A0                 | Address Input. Sets the LSB of the 7-bit slave address.                                                                                                                                                                                                                                                                                                                                                                                |

| B4                                   | $V_{DD}$           | Power Supply Input. The AD5593R can operate from 2.7 V to 5.5 V. Decouple the supply with a 0.1 μF capacitor to GND.                                                                                                                                                                                                                                                                                                                   |

| B3, C4, C3,<br>C2, D1, D4,<br>C1, B2 | I/O0 to I/O7       | Input/Output 0 through Input/Output 7. These pins can be independently configured as DACs, ADCs, or general-purpose digital inputs or outputs. The function of each pin is determined by programming the appropriate bits in the configuration registers.                                                                                                                                                                              |

| D3                                   | V <sub>REF</sub>   | Reference Input/Output. When the internal reference is enabled, the 2.5 V reference voltage is available on the pin. A 0.1 $\mu$ F capacitor connected from the V <sub>REF</sub> pin to GND is recommended to achieve the specified performance from the AD5593R. When the internal reference is disabled, an external reference must be applied to this pin. The voltage range for the external reference is 1 V to V <sub>DD</sub> . |

| D2                                   | V <sub>LOGIC</sub> | Interface Power Supply. The voltage ranges from 1.8 V to 5.5 V.                                                                                                                                                                                                                                                                                                                                                                        |

| B1                                   | GND                | Ground Reference Point for All Circuitry.                                                                                                                                                                                                                                                                                                                                                                                              |

| A1                                   | SDA                | Serial Data Input. This pin is used in conjunction with the SCL line to clock data into or out of the input shift register. SDA is a bidirectional, open-drain line that must be pulled to the V <sub>LOGIC</sub> supply with an external pull-up resistor.                                                                                                                                                                            |

| A2                                   | SCL                | Serial Clock Line. This is used in conjunction with the SDA line to clock data into or out of the 16-bit input register.                                                                                                                                                                                                                                                                                                               |

## TYPICAL PERFORMANCE CHARACTERISTICS

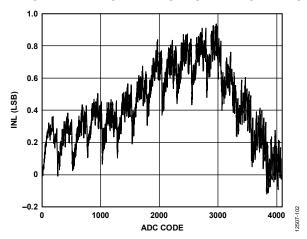

Figure 6. ADC INL;  $V_{DD} = 5.5 V$

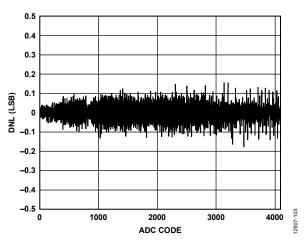

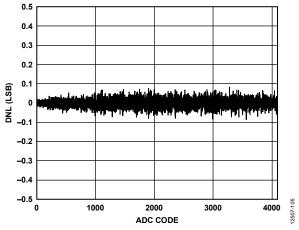

Figure 7. ADC DNL;  $V_{DD} = 5.5 V$

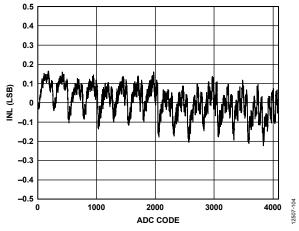

Figure 8. ADC INL;  $V_{DD} = 2.7 V$

Figure 9. ADC DNL;  $V_{DD} = 2.7 V$

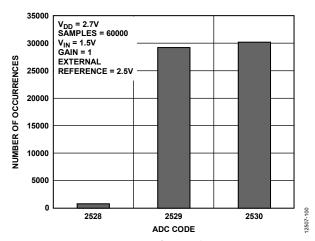

Figure 10. Histogram of ADC Codes;  $V_{DD} = 2.7 V$

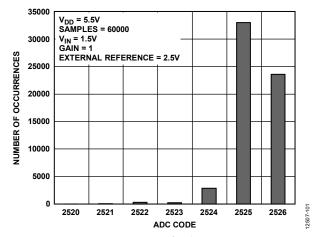

Figure 11. Histogram of Codes;  $V_{DD} = 5.5 V$

Figure 12. ADC Bandwidth

0.5

-0.5

-1.0

1024

2048

3072

4095

DAC CODE

Figure 14. DAC DNL

1.0

Figure 15. DAC Adjacent Code Glitch

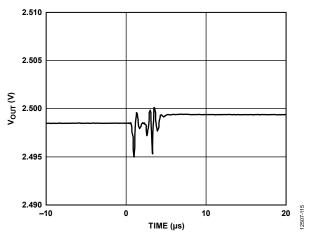

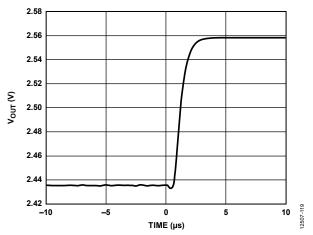

Figure 16. DAC Digital to Analog Glitch (Rising)

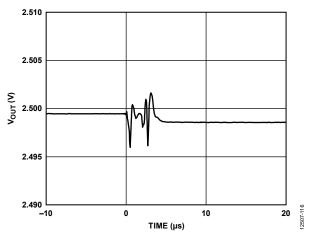

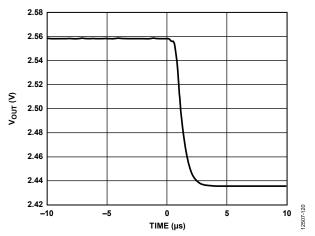

Figure 17. DAC Digital to Analog Glitch (Falling)

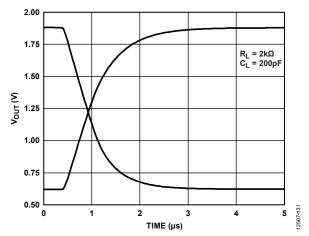

Figure 18. DAC Settling Time (100 Code Change, Rising Edge)

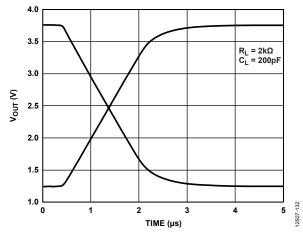

Figure 19. DAC Settling Time (100 Code Change, Falling Edge)

Figure 20. DAC Settling Time, Output Range = 0 V to  $V_{REF}$

Figure 21. DAC Settling Time, Output Range = 0 V to  $2 \times V_{REF}$

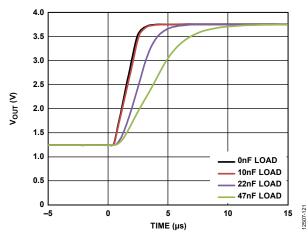

Figure 22. DAC Settling Time vs. Capacitive Load

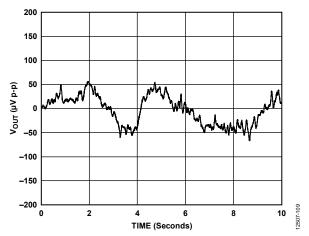

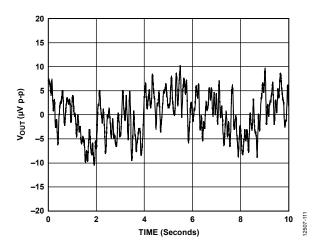

Figure 23. DAC 1/f Noise with External Reference

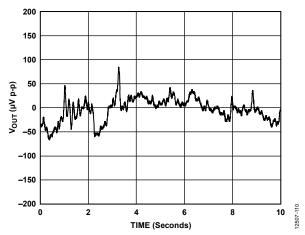

Figure 24. DAC 1/f Noise with Internal Reference

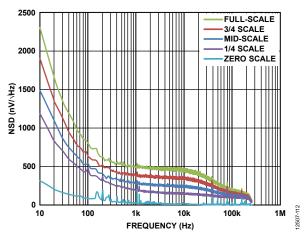

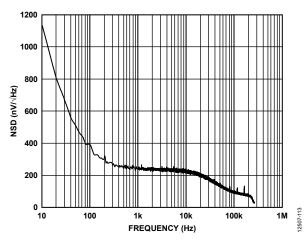

Figure 25. DAC Output Noise Spectral Density

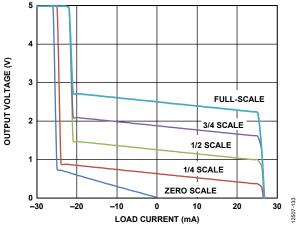

Figure 26. DAC Output Sink and Source Capability, Output Range = 0 V to  $V_{REF}$

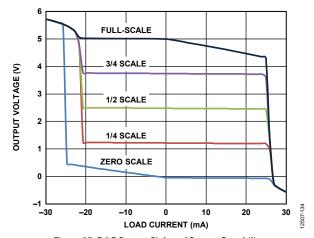

Figure 27. DAC Output Sink and Source Capability, Output Range = 0 V to  $2 \times V_{REF}$

Figure 28. Internal Reference 1/f Noise

Figure 29. Reference Noise Spectral Density

Figure 30. Reference Line Regulation

## **TERMINOLOGY**

#### ADC Integral Nonlinearity (INL)

For the ADC, INL is the maximum deviation from a straight line passing through the endpoints of the ADC transfer function. The end points of the transfer function are zero scale, a point that is 1 LSB below the first code transition, and full scale, a point that is 1 LSB above the last code transition.

#### ADC Differential Nonlinearity (DNL)

For the ADC, DNL is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

#### Offset Error

Offset error is the deviation of the first code transition (00 ... 000) to (00 ... 001) from the ideal, that is, AGND + 1 LSB.

#### **Gain Error**

Gain error is the deviation of the last code transition (111 ... 110) to (111 ... 111) from the ideal (that is,  $V_{REF} - 1$  LSB) after the offset error has been adjusted out.

#### Channel-to-Channel Isolation

Channel-to-channel isolation is a measure of the level of crosstalk between channels. It is measured by applying a full-scale 5 kHz sine wave signal to all nonselected ADC input channels and determining how much that signal is attenuated in the selected channel. This specification is the worst case across all ADC channels for the AD5593R.

#### ADC Power Supply Rejection Ratio (PSRR)

For the ADC, variations in power supply affect the full-scale transition, but not the converter linearity. Power supply rejection is the maximum change in the full-scale transition point due to a change in power supply voltage from the nominal value.

#### **Track-and-Hold Acquisition Time**

The track-and-hold amplifier goes into track mode when the ADC sequence register has been written to. The track and hold amplifier goes into hold mode when the conversion starts (see Figure 37). Track-and-hold acquisition time is the minimum time required for the track-and-hold amplifier to remain in track mode for its output to reach and settle to within ±1 LSB of the applied input signal, given a step change to the input signal.

#### Signal-to-(Noise + Distortion) Ratio (SINAD)

SINAD is the measured ratio of signal to (noise + distortion) at the output of the analog-to-digital converter. The signal is the rms amplitude of the fundamental. Noise is the sum of all nonfundamental signals up to half the sampling frequency (fs/2), excluding dc. The ratio is dependent on the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical SINAD for an ideal N-bit converter with a sine wave input is given by

Signal-to-(Noise + Distortion) (dB) = 6.02N + 1.76

Thus, for a 12-bit converter, this is 74 dB.

#### **ADC Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of harmonics to the fundamental. For the AD5593R, it is defined as

$$THD (dB) = 20 \times \log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}$$

where  $V_1$  is the rms amplitude of the fundamental and  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$ , and  $V_6$  are the rms amplitudes of the second through the sixth harmonics.

#### Peak Harmonic or Spurious Noise

Peak harmonic or spurious noise is defined as the ratio of the rms value of the next largest component in the ADC output spectrum (up to  $f_{\rm S}/2$  and excluding dc) to the rms value of the fundamental. Normally, the value of this specification is determined by the largest harmonic in the spectrum, but for ADCs where the harmonics are buried in the noise floor, it is a noise peak.

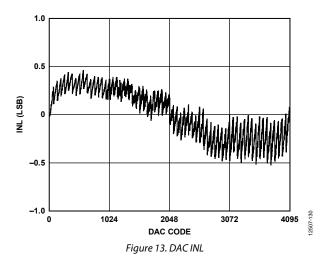

#### DAC Relative Accuracy or Integral Nonlinearity (INL)

For the DAC, relative accuracy or integral nonlinearity is a measurement of the maximum deviation, in LSBs, from a straight line passing through the endpoints of the DAC transfer function. A typical INL vs. code plot is shown in Figure 13.

#### DAC Differential Nonlinearity (DNL)

For the DAC, differential nonlinearity is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm 1$  LSB maximum ensures monotonicity. This DAC is guaranteed monotonic by design. A typical DNL vs. code plot can be seen in Figure 14.

#### Zero Code Error

Zero code error is a measurement of the output error when zero code (0x000) is loaded to the DAC register. Ideally, the output is 0 V. The zero code error is always positive in the AD5593R because the output of the DAC cannot go below 0 V due to a combination of the offset errors in the DAC and the output amplifier. Zero code error is expressed in mV.

#### **Gain Error**

Gain error is a measure of the span error of the DAC. It is the deviation in slope of the DAC transfer characteristic from the ideal expressed as % of FSR.

#### **Offset Error**

Offset error is a measure of the difference between  $V_{\text{OUT}}$  (actual) and  $V_{\text{OUT}}$  (ideal) expressed in mV in the linear region of the transfer function. Offset error can be negative or positive.

#### Offset Error Drift

Offset error drift is a measurement of the change in offset error with a change in temperature. It is expressed in  $\mu V/^{\circ}C$ .

#### DAC DC Power Supply Rejection Ratio (PSRR)

For the DAC, PSRR indicates how the output of the DAC is affected by changes in the supply voltage. PSRR is the ratio of the change in  $V_{\text{OUT}}$  to a change in  $V_{\text{DD}}$  for full-scale output of the DAC. It is measured in mV/V.  $V_{\text{REF}}$  is held at 2 V, and  $V_{\text{DD}}$  is varied by  $\pm 10\%$ .

#### **Output Voltage Settling Time**

Output voltage settling time is the amount of time it takes for the output of a DAC to settle to a specified level for a ¼ to ¾ full-scale input change and is measured from the rising edge of SDA that generates the stop condition.

#### Digital-to-Analog Glitch Impulse

Digital-to-analog glitch impulse is the impulse injected into the analog output when the input code in the DAC register changes state. It is normally specified as the area of the glitch in nV-sec, and is measured when the digital input code is changed by 1 LSB at the major carry transition (0x7FF to 0x800) (see Figure 16 and Figure 17).

#### Digital Feedthrough

Digital feedthrough is a measure of the impulse injected into the analog output of the DAC from the digital inputs of the DAC, but is measured when the DAC output is not updated. It is specified in nV-sec, and measured with a full-scale code change on the data bus, that is, from all 0s to all 1s and vice versa.

#### Reference Feedthrough

Reference feedthrough is the ratio of the amplitude of the signal at the DAC output to the reference input when the DAC output is not being updated. It is expressed in dB.

#### Noise Spectral Density (NSD)

NSD is a measurement of the internally generated random noise. Random noise is characterized as a spectral density ( $nV/\sqrt{Hz}$ ). It is measured by loading the DAC to midscale and measuring noise at the output. It is measured in  $nV/\sqrt{Hz}$ . A plot of noise spectral density is shown in Figure 25.

#### **DC Crosstalk**

DC crosstalk is the dc change in the output level of one DAC in response to a change in the output of another DAC. It is measured with a full-scale output change on one DAC (or soft power-down and power-up) while monitoring another DAC kept at midscale. It is expressed in  $\mu V$ .

DC crosstalk due to load current change is a measure of the impact that a change in load current on one DAC has to another DAC kept at midscale. It is expressed in  $\mu V/mA$ .

#### **Digital Crosstalk**

Digital crosstalk is the glitch impulse transferred to the output of one DAC at midscale in response to a full-scale code change (all 0s to all 1s and vice versa) in the input register of another DAC. It is measured in standalone mode and is expressed in nV-sec.

#### **Analog Crosstalk**

Analog crosstalk is the glitch impulse transferred to the output of one DAC due to a change in the output of another DAC. It is first measured by loading one of the input registers with a full-scale code change (all 0s to all 1s and vice versa). Then it is measured by executing a software LDAC and monitoring the output of the DAC whose digital code was not changed. The area of the glitch is expressed in nV-sec.

#### **DAC-to-DAC Crosstalk**

DAC-to-DAC crosstalk is the glitch impulse transferred to the output of one DAC due to a digital code change and subsequent analog output change of another DAC. It is measured by loading the attack channel with a full-scale code change (all 0s to all 1s and vice versa), using the write to and update commands while monitoring the output of the victim channel that is at midscale. The energy of the glitch is expressed in nV-sec.

#### **Multiplying Bandwidth**

The amplifiers within the DAC have a finite bandwidth. The multiplying bandwidth is a measure of this finite bandwidth. A sine wave on the reference (with full-scale code loaded to the DAC) appears on the output. The multiplying bandwidth is the frequency at which the output amplitude falls to 3 dB below the input.

#### **DAC Total Harmonic Distortion (THD)**

For the DAC, THD is the difference between an ideal sine wave and its attenuated version using the DAC. The sine wave is used as the reference for the DAC, and the THD is a measurement of the harmonics present on the DAC output. It is measured in dB.

#### **Voltage Reference Temperature Coefficient (TC)**

Voltage reference TC is a measure of the change in the reference output voltage with a change in temperature. The voltage reference TC is calculated using the box method, which defines the TC as the maximum change in the reference output over a given temperature range expressed in ppm/°C, as follows:

$$TC = \left[\frac{V_{REF(MAX)} - V_{REF(MIN)}}{V_{REF(NOM)} \times Temp \ Range}\right] \times 10^{6}$$

where:

$V_{\it REF(MAX)}$  is the maximum reference output measured over the total temperature range.

$V_{REF(MIN)}$  is the minimum reference output measured over the total temperature range.

$V_{REF(NOM)}$  is the nominal reference output voltage, 2.5 V. *Temp Range* is the specified temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C.

## THEORY OF OPERATION

The AD5593R is an 8-channel, configurable analog and digital I/O port. The AD5593R has eight pins that can be independently configured as a 12-bit DAC output channel, a 12-bit ADC input channel, a digital input pin, or a digital output pin.

The function of each pin is determined by programming the ADC, DAC, or GPIO configuration registers as appropriate.

#### **DAC SECTION**

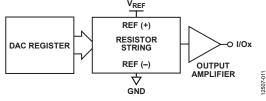

The AD5593R contains eight 12-bit DACs. Each DAC consists of a string of resistors followed by an output buffer amplifier. Figure 31 shows a block diagram of the DAC architecture.

Figure 31. DAC Channel Architecture Block Diagram

The DAC channels share a single DAC range bit (see Bit D4 in Table 13) that sets the output range to 0 V to  $V_{REF}$  or 0 V to 2 ×  $V_{REF}$ . Because the range bit is shared by all channels, it is not possible to set different output ranges on a per channel basis. The input coding to the DAC is straight binary. Therefore, the ideal output voltage is given by

$$V_{OUT} = G \times V_{REF} \times \left(\frac{D}{2^N}\right)$$

where:

G = 1 for an output range of 0 V to  $V_{REF}$  or G = 2 for an output range of 0 V to  $2 \times V_{REF}$ .

$V_{REF}$  is the voltage on the  $V_{REF}$  pin.

D is the decimal equivalent of the binary code (0 to 4095) that is loaded to the DAC register.

N = 12.

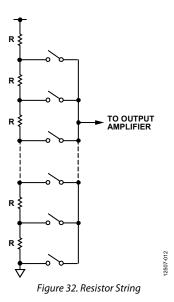

#### **Resistor String**

The simplified segmented resistor string DAC structure is shown in Figure 32. The code loaded to the DAC register determines the switch on the string that is connected to the output buffer.

Because each resistance in the string has the same value, R, the string DAC is guaranteed monotonic.

#### **DAC Output Buffer**

The output buffer is designed as an input/output rail-to-rail buffer. The output buffer can drive 2 nF capacitance with a 1 k $\Omega$  resistor in parallel. The slew rate is 1.25 V/ $\mu$ s with a  $^{1}\!4$  to  $^{3}\!4$  scale settling time of 6  $\mu$ s. By default, the DAC outputs update directly after data has been written to the input register. The LDAC register delays the updates until additional channels have been written to if required. See the LDAC Mode Operation section for more information.

#### **ADC SECTION**

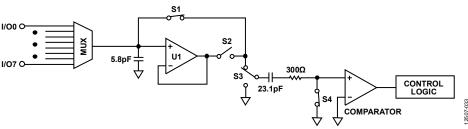

The ADC section is a fast, 12-bit, single-supply ADC with a conversion time of 2  $\mu s$ . The ADC is preceded by a multiplexer that switches selected I/O pins to the ADC. A sequencer is included to switch the multiplexer to the next selected channel automatically. Channels are selected for conversion by writing to the ADC sequence register. When the write to the ADC sequence register has completed, the first channel in the conversion sequence is put into track mode. Each channel can track the input signal for a minimum of 500 ns. The conversion is initiated on the rising edge of the clock for the acknowledge (ACK) that occurs after the slave address (see Figure 37).

Each conversion takes 2  $\mu s$ . The ADC has a range bit (ADC range select in the general-purpose control register, see Bit D5 in Table 13) that sets the input range as 0 V to  $V_{REF}$  or 0 V to 2  $\times$   $V_{REF}$ . All input channels share the same range. The output coding of the ADC is straight binary. It is possible to set each I/Ox pin as both a DAC and an ADC. In this case, the primary function is that of the DAC. If the pin is selected for inclusion in an ADC conversion sequence, the voltage on the pin is converted and made available via the serial interface. This allows the DAC voltage to be monitored.

#### **Calculating ADC Input Current**

The current flowing into the I/Ox pins configured as ADC inputs varies with sampling rate (fs), the voltage difference between successive channels ( $V_{\text{DIFF}}$ ), and whether buffered or unbuffered mode is used. Figure 33 shows a simplified version of the ADC input structure. When a new channel is selected for conversion, 5.8 pF must be charged to or discharged from the voltage that on the previously selected channel. The time required for the charge or discharge depends on the voltage difference between the two channels. This dependence affects the input impedance of the multiplexer and, therefore, the input current flowing into the I/Ox pins.

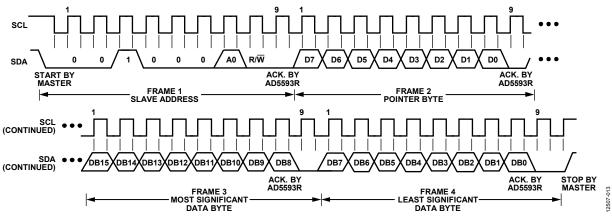

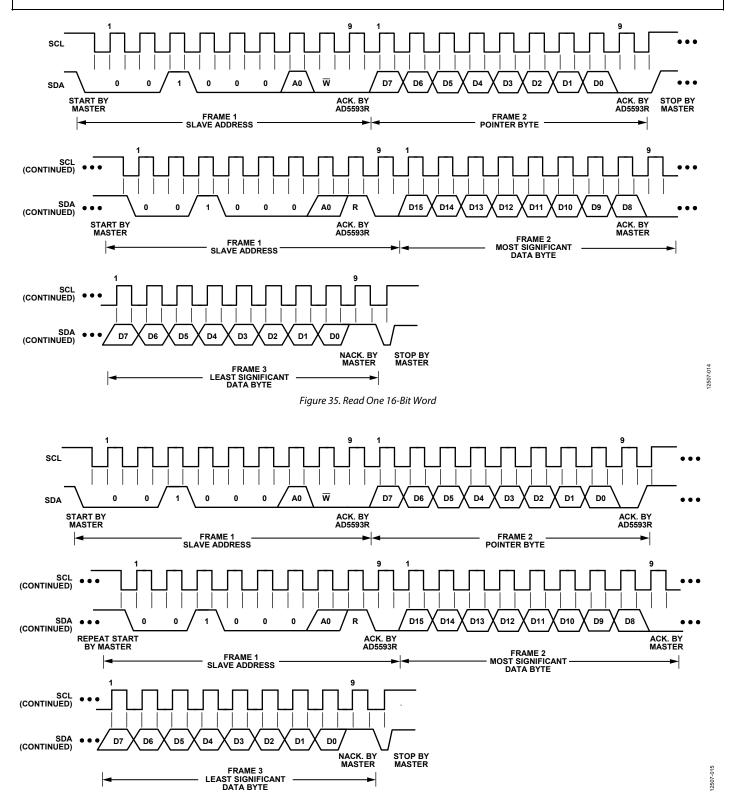

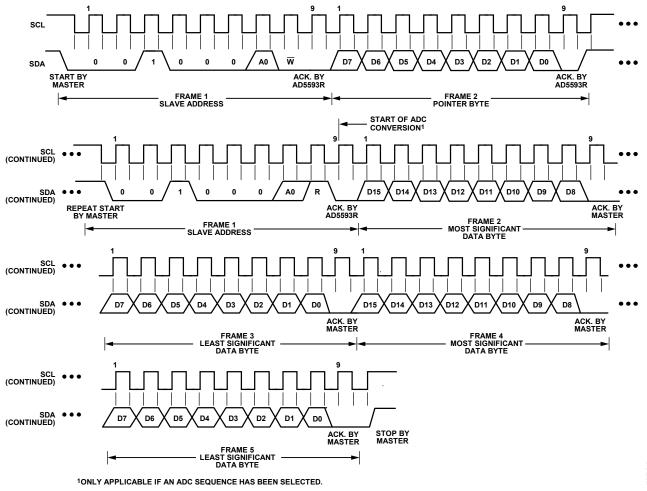

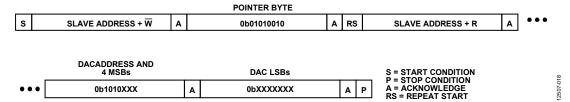

In buffered mode, Switch S1 is open and Switch S2 is closed. In buffered mode, the U1 buffer directly drives the 23.1 pF capacitor and the charging time of the capacitors is negligible. In unbuffered mode, Switch S1 is closed and Switch S2 is closed. In unbuffered mode, the 23.1 pF capacitor must be charged from the I/Ox pins; this charging contributes to the input current. For applications where the ADC input current is too high, an external input buffer may be required. The choice of buffer is a function of the particular application.