## Motorola Semiconductor Application Note

# AN1820

## Software I<sup>2</sup>C Communications

By Brad Bierschenk MMD Applications Engineering Austin, Texas

### Introduction

The I<sup>2</sup>C (inter-integrated circuit) protocol is a 2-wire serial communications interface, implemented on numerous microcontrollers and peripheral devices. Many MCUs (microcontroller units) do not have an I<sup>2</sup>C module, yet they are required to communicate to 2-wire, or I<sup>2</sup>C, devices.

This application note describes a method of communicating on an I<sup>2</sup>C bus by controlling digital input/output (I/O) pins. This "bit-banged" method can be implemented on any Motorola MCU.

## I<sup>2</sup>C Overview

$I^2C$  is a 2-wire communications link, requiring a clock line (SCK) and a data line (SDA) to communicate. The frequency of the  $I^2C$  clock can go up to 100 Kbits per second for standard mode, and up to 400 Kbits per second for fast mode.

An I<sup>2</sup>C bus has both master devices and slave devices attached to it. A master is defined as a device which initiates a transfer, generates clock signals, and terminates a transfer. A slave device is simply a device

AN1820

© Motorola, Inc., 1999

For More Information On This Product, Go to: www.freescale.com

### **Application Note**

addressed by a master.  $I^2C$  provides for multiple masters on the same bus. The  $I^2C$  also provides some error checking by acknowledgment bits during byte transfers.

The application presented in this document illustrates a limited version of the I<sup>2</sup>C specification. It is not intended to implement all the features of an I<sup>2</sup>C bus. It only provides the basic functionality required to transmit as a master device to slave devices through a 2-wire interface. The advantage of this method is it uses standard digital input/output pins available on any Motorola MCU.

The application presented here provides the following functionality:

- 7-bit addressing

- Single master transmitter

- Multiple data bytes within a serial transfer

- Serial clock frequency of approximately 28 kHz (arbitrary)

- Acknowledgment polling for error checking

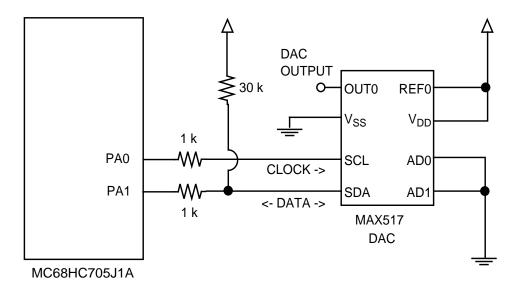

By controlling two digital I/O pins, one can simulate an I<sup>2</sup>C transfer. When the I/O pins are CMOS and not open-drain, some safegaurds have to be implemented. A series resistor should be used between the CMOS output pin and the receiver's input pin. This will provide some current limiting should the two devices attempt to output conflicting logic levels.

The other consideration is supporting a logic high for any open-drain receiver pins. A pullup resistor can be used at the receiver's open-drain pin to passively pullup to the supply voltage, when the pin is not being actively driven low. This pullup resistor should be carefully chosen, so that when the master pin drives low, a valid  $V_{\rm IL}$  level is presented to the I<sup>2</sup>C receiver's pin.

The diagram shown in **Figure 1** illustrates a way to connect digital I/O pins to an external I<sup>2</sup>C receiver device. In this case, a MC68HC705J1A microcontroller is connected to a Maxim MAX517 DAC (Digital-to-Analog Converter). The MAX517 has a 2-wire interface that is I<sup>2</sup>C compatible. The MC68HC705J1A has CMOS bidirectional input/output

AN1820

pins. When connected as shown, successful I<sup>2</sup>C communications can be made to the external IC.

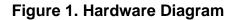

An I<sup>2</sup>C transfer is composed of specific stages, defined by the states of the two wires. **Figure 2** shows the timing between the clock and data lines. To signal the beginning of a transmission, a START condition is presented to the bus. This START condition is indicated by a falling edge on SDA, while SCK is held high.

Once the START condition has been driven, the master device places a 7-bit address on the bus, with its most significant bit first. This address corresponds to the address of the  $I^2C$  device the transfer is intended for. The eighth bit following the 7-bit address can be high or low, depending on whether it is a "read" or "write" operation.

Figure 2. Example of I<sup>2</sup>C Transfer Timing

As with all bytes transferred on the I<sup>2</sup>C bus, a ninth clock cycle is used as an acknowledgment. The SDA line is read during this ninth clock cycle and signifies whether or not the byte is acknowledged. The receiver will drive the SDA line low during the ninth clock cycle if it acknowledges the byte transmission.

Any number of data bytes can follow the address byte, each composed of eight data bits and a ninth acknowledge bit. To end a transfer, a STOP condition is imposed on the I<sup>2</sup>C bus. The STOP condition is indicated by a rising edge on SDA, while the SCK line is held high.

# **NOTE:** To avoid unwanted START or STOP conditions, the software must transition the SDA pin only while the SCK line is held low.

A listing of assembly code that shows a specific implementation of  $I^2C$  in software follows this text. This application does require some software overhead, but is somewhat interruptible as the  $I^2C$  bus is completely synchronous. An implementation that requires less software overhead could be created using a more automated timing source, such as a free-running counter or real-time interrupt.

The code shows how a MC68HC705J1A microcontroller can be connected to an  $I^2C$  peripheral, in this case a Maxim MAX517 DAC. The software continuously sends a write command to the DAC, ramping the digital value for the DAC from \$00 to \$FF and back down again. This creates a triangular wave at the output of the DAC.

The point is not to show a completely useful DAC application, but to illustrate the use of digital input/output pins as an  $I^2C$  master device.

AN1820

MOTOROLA

### **Code Listings**

| * -=-=-=-<br>* TRIANGI                             |                                 |                                                                                              | -=-=-=-=-=-=-=-=-=-=-=-=-=-                                                                                                |

|----------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| * -=-=-                                            | -=-=-=                          |                                                                                              | -=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=                                                                                   |

| * Target                                           | : 705J                          | t of I2C bit-banging<br>1A<br>l Bierschenk, MMD App                                          |                                                                                                                            |

|                                                    |                                 | Maxim I <sup>2</sup> C DAC IC, MA                                                            | -=-=-=-=-=-=-=-=-=-=-=-=-=-=                                                                                               |

|                                                    |                                 | e interface" (anothe:                                                                        |                                                                                                                            |

| Digita]<br>\$FF, ar                                | l to A<br>nd bac                | ntinuously sends 8-b<br>nalog IC, incrementi<br>k down again. This c<br>aveform at the outpu | ng from \$00 to<br>reates a                                                                                                |

| complet                                            | cely a                          | uency is approximate<br>rbitrary.                                                            | ly 28 kHz. This is                                                                                                         |

| Assemb                                             |                                 |                                                                                              |                                                                                                                            |

| AMSPACE<br>OMSPACE<br>ORTA<br>ORTB<br>DDRA<br>DDRB | EQU<br>EQU<br>EQU<br>EQU<br>EQU | \$C0<br>\$300<br>\$00<br>\$01<br>\$04                                                        | <pre>;RAM start address<br/>;EPROM start address<br/>;Port A<br/>;Port B<br/>;Data direction A<br/>;Data direction B</pre> |

| Need a                                             | clock                           | lines on Port A pin<br>(SCL) and data (SDA                                                   |                                                                                                                            |

| SCL E<br>SDA E                                     | QU                              | 0                                                                                            | ;Serial clock<br>;Serial data                                                                                              |

| ACADDR                                             | EQU                             | \$2C                                                                                         | ;Slave address of DAC                                                                                                      |

| RAM Va                                             | riable                          | :<br>:S                                                                                      |                                                                                                                            |

|                                                    |                                 | ORG RAMSPACE                                                                                 |                                                                                                                            |

| BitCounte<br>Value<br>Direction                    | RMB                             | 1                                                                                            | ;Used to count bits in a Tx<br>;Used to store data value<br>;Indicates increment or<br>;decrement                          |

| Start o                                            | of pro                          | gram code                                                                                    |                                                                                                                            |

| 01<br>01<br>Start:                                 | RG                              | ROMSPACE                                                                                     | ;Start of EPROM                                                                                                            |

| ; :<br>C:<br>C:                                    | LR<br>LR                        | alize variables<br>Value<br>BitCounter<br>Direction                                          | ;Clear all RAM variables                                                                                                   |

| ; :<br>Ll<br>S'                                    | Setup                           | parallel ports<br>#\$03<br>PORTA<br>DDRA                                                     | ;PA0 and PA1 as outputs<br>;driven high to start                                                                           |

AN1820

## **Application Note**

| TxLoop                                                         |                                                                                                                                                                            |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                |                                                                                                                                                                            | Direction<br>GoUp                                                                                                                                                                                                 | ;Increment or decrement?                                                                                                                                                                                                                                                                                                |

| GoDown                                                         | :                                                                                                                                                                          |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                         |

|                                                                | LDA<br>BNE                                                                                                                                                                 | Value<br>GD2                                                                                                                                                                                                      | ;Decrement<br>;Change direction if needed                                                                                                                                                                                                                                                                               |

|                                                                | CLR                                                                                                                                                                        | Direction                                                                                                                                                                                                         | , change arreetion if neede                                                                                                                                                                                                                                                                                             |

| GD2:                                                           | BRA                                                                                                                                                                        | SendIt                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                         |

| 302.                                                           |                                                                                                                                                                            | Value                                                                                                                                                                                                             | ;Decrement the data value                                                                                                                                                                                                                                                                                               |

|                                                                | BRA                                                                                                                                                                        | SendIt                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                         |

| GoUp:                                                          | LDA                                                                                                                                                                        | Value                                                                                                                                                                                                             | ;Increment                                                                                                                                                                                                                                                                                                              |

|                                                                | CMP<br>BNE                                                                                                                                                                 | #\$FF                                                                                                                                                                                                             | ;Change direction if needed                                                                                                                                                                                                                                                                                             |

|                                                                | BNE<br>INC                                                                                                                                                                 | GU2<br>Direction                                                                                                                                                                                                  | ;Increment the data value                                                                                                                                                                                                                                                                                               |

|                                                                | BRA                                                                                                                                                                        | SendIt                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                         |

| GU2:                                                           | INC                                                                                                                                                                        | Value                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                         |

|                                                                |                                                                                                                                                                            |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                         |

| *<br>* Send                                                    | the T <sup>2</sup>                                                                                                                                                         | C transmission, inclu                                                                                                                                                                                             | ding START, address.                                                                                                                                                                                                                                                                                                    |

|                                                                | 0110 1                                                                                                                                                                     |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                         |

| * data                                                         | , and S                                                                                                                                                                    | TOP                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                         |

| * data<br>*                                                    | , and S                                                                                                                                                                    | TOP<br>                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                         |

| * data<br>*                                                    | , and S<br><br>:<br>;STAR1                                                                                                                                                 | condition                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                         |

| * data<br>*                                                    | , and S<br><br>:<br>;STAR1                                                                                                                                                 |                                                                                                                                                                                                                   | Give START condition;                                                                                                                                                                                                                                                                                                   |

| * data<br>*                                                    | , and S<br><br>:<br>;START<br>JSR                                                                                                                                          | ' condition<br>I2CStartBit                                                                                                                                                                                        | ;Give START condition<br>7-bit address + 0 as LSbit                                                                                                                                                                                                                                                                     |

| * data<br>*                                                    | , and S<br>;<br>;STARI<br>JSR<br>;ADDRE<br>LDA                                                                                                                             | ' condition<br>I2CStartBit                                                                                                                                                                                        | 7-bit address + 0 as LSbit<br>;Slave device address                                                                                                                                                                                                                                                                     |

| * data<br>*<br>SendIt                                          | , and S<br>; STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA                                                                                                                        | ' condition<br>I2CStartBit<br>SS byte, consists of<br>#DACADDR                                                                                                                                                    | 7-bit address + 0 as LSbit<br>;Slave device address<br>;Need this to align address                                                                                                                                                                                                                                      |

| * data<br>*                                                    | , and S<br>; STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR                                                                                                                 | ' condition<br>I2CStartBit<br>SS byte, consists of<br>#DACADDR<br>I2CTxByte                                                                                                                                       | 7-bit address + 0 as LSbit<br>;Slave device address                                                                                                                                                                                                                                                                     |

| * data<br>*                                                    | , and S<br>; STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA                                                                                                       | ' condition<br>I2CStartBit<br>SS byte, consists of<br>#DACADDR<br>I2CTxByte<br>bytes                                                                                                                              | 7-bit address + 0 as LSbit<br>;Slave device address<br>;Need this to align address<br>;Send the eight bits                                                                                                                                                                                                              |

| * data<br>*                                                    | , and S<br>; STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA<br>LDA                                                                                                | ' condition<br>I2CStartBit<br>SS byte, consists of<br>#DACADDR<br>I2CTxByte<br>bytes<br>#\$00                                                                                                                     | 7-bit address + 0 as LSbit<br>;Slave device address<br>;Need this to align address                                                                                                                                                                                                                                      |

| * data<br>*                                                    | , and S<br>; STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA<br>LDA<br>JSR                                                                                         | condition<br>I2CStartBit<br>SS byte, consists of<br>#DACADDR<br>I2CTxByte<br>bytes<br>#\$00<br>I2CTxByte                                                                                                          | 7-bit address + 0 as LSbit<br>;Slave device address<br>;Need this to align address<br>;Send the eight bits<br>;\$00 is command byte for D<br>;Send the 8 bits                                                                                                                                                           |

| * data<br>*                                                    | , and S<br>; STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA<br>LDA<br>JSR<br>LDA                                                                                  | ' condition<br>I2CStartBit<br>SSS byte, consists of<br>#DACADDR<br>I2CTxByte<br>bytes<br>#\$00<br>I2CTxByte<br>Value                                                                                              | <pre>7-bit address + 0 as LSbit<br/>;Slave device address<br/>;Need this to align addres<br/>;Send the eight bits<br/>;\$00 is command byte for D.<br/>;Send the 8 bits<br/>;Value is value to set DAC</pre>                                                                                                            |

| * data<br>*                                                    | , and S<br>; STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA<br>LDA<br>JSR<br>LDA<br>JSR                                                                           | ' condition<br>I2CStartBit<br>SS byte, consists of<br>#DACADDR<br>I2CTxByte<br>bytes<br>#\$00<br>I2CTxByte<br>Value<br>I2CTxByte                                                                                  | <pre>7-bit address + 0 as LSbit ;Slave device address ;Need this to align addres ;Send the eight bits ;\$00 is command byte for D.</pre>                                                                                                                                                                                |

| * data<br>*                                                    | , and S<br>; STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA<br>LDA<br>JSR<br>LDA<br>JSR<br>; STOP                                                                 | condition<br>I2CStartBit<br>SS byte, consists of<br>#DACADDR<br>I2CTxByte<br>bytes<br>#\$00<br>I2CTxByte<br>Value<br>I2CTxByte<br>condition                                                                       | <pre>7-bit address + 0 as LSbit<br/>;Slave device address<br/>;Need this to align addres<br/>;Send the eight bits<br/>;\$00 is command byte for D.<br/>;Send the 8 bits<br/>;Value is value to set DAC<br/>;Send it</pre>                                                                                               |

| * data<br>*                                                    | , and S<br>; STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA<br>LDA<br>JSR<br>LDA<br>JSR                                                                           | ' condition<br>I2CStartBit<br>SS byte, consists of<br>#DACADDR<br>I2CTxByte<br>bytes<br>#\$00<br>I2CTxByte<br>Value<br>I2CTxByte                                                                                  | <pre>7-bit address + 0 as LSbit<br/>;Slave device address<br/>;Need this to align addres<br/>;Send the eight bits<br/>;\$00 is command byte for D.<br/>;Send the 8 bits<br/>;Value is value to set DAC</pre>                                                                                                            |

| * data<br>*                                                    | , and S<br>; STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA<br>LDA<br>JSR<br>LDA<br>JSR<br>; STOP<br>JSR<br>JSR                                                   | <pre>' condition<br/>I2CStartBit<br/>SS byte, consists of<br/>#DACADDR<br/>I2CTxByte<br/>bytes<br/>#\$00<br/>I2CTxByte<br/>Value<br/>I2CTxByte<br/>condition<br/>I2CStopBit<br/>I2CBitDelay</pre>                 | <pre>7-bit address + 0 as LSbit<br/>;Slave device address<br/>;Need this to align addres<br/>;Send the eight bits<br/>;\$00 is command byte for D.<br/>;Send the 8 bits<br/>;Value is value to set DAC<br/>;Send it<br/>;Give STOP condition<br/>;Wait a bit</pre>                                                      |

| * data<br>*                                                    | , and S<br>; STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA<br>LDA<br>JSR<br>LDA                                                                                  | ' condition<br>I2CStartBit<br>SSS byte, consists of<br>#DACADDR<br>I2CTxByte<br>bytes<br>#\$00<br>I2CTxByte<br>Value                                                                                              | <pre>7-bit address + 0 as LSbit<br/>;Slave device address<br/>;Need this to align addres<br/>;Send the eight bits<br/>;\$00 is command byte for I<br/>;Send the 8 bits<br/>;Value is value to set DAG</pre>                                                                                                             |

| * data<br>*                                                    | , and S<br>; STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA<br>LDA<br>JSR<br>LDA<br>JSR<br>; STOP<br>JSR<br>JSR                                                   | <pre>' condition<br/>I2CStartBit<br/>SS byte, consists of<br/>#DACADDR<br/>I2CTxByte<br/>bytes<br/>#\$00<br/>I2CTxByte<br/>Value<br/>I2CTxByte<br/>condition<br/>I2CStopBit<br/>I2CBitDelay</pre>                 | <pre>7-bit address + 0 as LSbit<br/>;Slave device address<br/>;Need this to align addres<br/>;Send the eight bits<br/>;\$00 is command byte for D<br/>;Send the 8 bits<br/>;Value is value to set DAC<br/>;Send it<br/>;Give STOP condition<br/>;Wait a bit</pre>                                                       |

| * data<br>*                                                    | , and S<br>; STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA<br>LDA<br>JSR<br>LDA<br>JSR<br>; STOP<br>JSR                                                          | <pre>' condition<br/>I2CStartBit<br/>SS byte, consists of<br/>#DACADDR<br/>I2CTxByte<br/>bytes<br/>#\$00<br/>I2CTxByte<br/>Value<br/>I2CTxByte<br/>condition<br/>I2CStopBit</pre>                                 | <pre>7-bit address + 0 as LSbit<br/>;Slave device address<br/>;Need this to align addres<br/>;Send the eight bits<br/>;\$00 is command byte for D<br/>;Send the 8 bits<br/>;Value is value to set DAC<br/>;Send it<br/>;Give STOP condition</pre>                                                                       |

| * data<br>*<br>SendIt                                          | , and S<br>; STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA<br>LDA<br>JSR<br>LDA<br>JSR<br>; STOP<br>JSR<br>JSR<br>BRA                                            | <pre>' condition<br/>I2CStartBit<br/>SS byte, consists of<br/>#DACADDR<br/>I2CTxByte<br/>bytes<br/>#\$00<br/>I2CTxByte<br/>Value<br/>I2CTxByte<br/>condition<br/>I2CStopBit<br/>I2CBitDelay<br/>TxLoop</pre>      | <pre>7-bit address + 0 as LSbit<br/>;Slave device address<br/>;Need this to align addres<br/>;Send the eight bits<br/>;\$00 is command byte for D<br/>;Send the 8 bits<br/>;Value is value to set DAC<br/>;Send it<br/>;Give STOP condition<br/>;Wait a bit<br/>;Repeat</pre>                                           |

| * data<br>*<br>SendIt<br>;-=-=-<br>; 12CT:                     | , and S<br>, STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA<br>LDA<br>JSR<br>LDA<br>JSR<br>; STOP<br>JSR<br>JSR<br>BRA<br>=========                               | <pre>' condition<br/>I2CStartBit<br/>SS byte, consists of<br/>#DACADDR<br/>I2CTxByte<br/>bytes<br/>#\$00<br/>I2CTxByte<br/>Value<br/>I2CTxByte<br/>condition<br/>I2CStopBit<br/>I2CBitDelay<br/>TxLoop</pre>      | <pre>7-bit address + 0 as LSbit<br/>;Slave device address<br/>;Need this to align addres<br/>;Send the eight bits<br/>;\$00 is command byte for D.<br/>;Send the 8 bits<br/>;Value is value to set DAC<br/>;Send it<br/>;Give STOP condition<br/>;Wait a bit<br/>;Repeat</pre>                                          |

| * data<br>*<br>SendIt<br>; 12CT<br>; Trans<br>; (Acc           | , and S<br>, STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA<br>LDA<br>JSR<br>LDA<br>JSR<br>LDA<br>JSR<br>STOP<br>JSR<br>BRA<br>=======<br>xByte<br>smit th        | <pre>' condition<br/>I2CStartBit<br/>SS byte, consists of<br/>#DACADDR<br/>I2CTxByte<br/>bytes<br/>#\$00<br/>I2CTxByte<br/>Value<br/>I2CTxByte<br/>condition<br/>I2CStopBit<br/>I2CBitDelay<br/>TxLoop<br/></pre> | <pre>7-bit address + 0 as LSbit<br/>;Slave device address<br/>;Need this to align addres<br/>;Send the eight bits<br/>;\$00 is command byte for D<br/>;Send the 8 bits<br/>;Value is value to set DAC<br/>;Send it<br/>;Give STOP condition<br/>;Wait a bit<br/>;Repeat<br/>====================================</pre>  |

| * data<br>*<br>SendIt<br>; 12CT<br>; Trans<br>; (Acc<br>; Must | , and S<br>, STARI<br>JSR<br>; ADDRE<br>LDA<br>ASLA<br>JSR<br>; DATA<br>LDA<br>JSR<br>LDA<br>JSR<br>; STOP<br>JSR<br>BRA<br>=-=-==<br>xByte<br>smit th<br>will n<br>be car | <pre>' condition<br/>I2CStartBit<br/>SS byte, consists of<br/>#DACADDR<br/>I2CTxByte<br/>bytes<br/>#\$00<br/>I2CTxByte<br/>Value<br/>I2CTxByte<br/>condition<br/>I2CStopBit<br/>I2CBitDelay<br/>TxLoop<br/></pre> | <pre>7-bit address + 0 as LSbit<br/>;Slave device address<br/>;Need this to align addres<br/>;Send the eight bits<br/>;\$00 is command byte for D.<br/>;Send the 8 bits<br/>;Value is value to set DAC<br/>;Send it<br/>;Give STOP condition<br/>;Wait a bit<br/>;Repeat<br/>====================================</pre> |

MOTOROLA

| I2CNex   | +Bi+·       |                                                |                             |

|----------|-------------|------------------------------------------------|-----------------------------|

| TZCHEN   | ROLA        |                                                | ;Shift MSbit into Carry     |

|          | BCC         | SendLow                                        | ;Send low bit or high bit   |

| SendHi   | gh:         |                                                | 2                           |

|          | BSET        | SDA, PORTA                                     | ;Set the data bit value     |

|          | JSR         | I2CSetupDelay                                  | ;Give some time for data    |

| setup    |             |                                                |                             |

|          | BSET        | SCL, PORTA                                     | ;Clock it in                |

|          | JSR         | I2CBitDelay                                    | ;Wait a bit                 |

| ~ 1-     | BRA         | I2CTxCont                                      | ;Continue                   |

| SendLo   |             |                                                |                             |

|          | BCLR        | SDA, PORTA                                     |                             |

|          | JSR         | I2CSetupDelay                                  |                             |

|          | BSET        | SCL, PORTA                                     |                             |

| TOCTAC   | JSR<br>opt: | I2CBitDelay                                    |                             |

| I2CTxC   | BCLR        | SCL, PORTA                                     | ;Restore clock to low state |

|          | DEC         | BitCounter                                     | Decrement the bit counter   |

|          | BEQ         | I2CAckPoll                                     | ;Last bit?                  |

|          | BRA         | I2CNextBit                                     | HAST DIT:                   |

| I2CAck   |             | IZCHEAUDIU                                     |                             |

| IZCACA.  | BSET        | SDA, PORTA                                     |                             |

|          | BCLR        | SDA, DDRA                                      | ;Set SDA as input           |

|          | JSR         | I2CSetupDelay                                  | Voet box as input           |

|          | BSET        | SCL, PORTA                                     | ;Clock the line to get ACK  |

|          | JSR         | I2CBitDelay                                    | , eroen ene rine to get nen |

|          | BRSET       | SDA, PORTA, I2CNoAck                           | ;Look for ACK from slave    |

|          | 211021      | 2211, 201111, 2201011011                       | device                      |

|          | BCLR        | SCL, PORTA                                     | Restore clock line          |

|          | BSET        | SDA, DDRA                                      | ;SDA back as output         |

|          | RTS         |                                                | -                           |

|          | ·No og      |                                                | from alore dorei ao         |

|          |             | knowledgment received<br>error action can be p |                             |

|          |             | ow, just restore the                           |                             |

| I2CNoA   |             |                                                | 545                         |

| 12011011 | BCLR        | SCL, PORTA                                     |                             |

|          | BSET        |                                                |                             |

|          | RTS         |                                                |                             |

|          |             |                                                |                             |

|          |             |                                                | =-=-=-=-=-=-=-=-=-=-=       |

|          |             | dition is defined as                           | a falling edge              |

|          |             | e SCL is high                                  |                             |

| -        |             | -=-=-=-=-=-=-=-=-=-                            |                             |

| I2CSta   |             |                                                |                             |

|          | BCLR        | SDA, PORTA                                     |                             |

|          | JSR         | I2CBitDelay                                    |                             |

|          | BCLR        | SCL, PORTA                                     |                             |

|          | RTS         |                                                |                             |

|          |             |                                                |                             |

| -        |             |                                                |                             |

|          |             | ition is defined as a                          | rising eage                 |

|          |             | e SCL is high                                  |                             |

|          |             | =-=-=-=-=-=-=-                                 |                             |

| I2CSto   | BCLR        | SDA, PORTA                                     |                             |

|          | BSET        | SCL, PORTA                                     |                             |

|          | BSET        | SDA, PORTA                                     |                             |

|          | JSR         | I2CBitDelay                                    |                             |

|          | RTS         | - 2 CD - CD C + CA y                           |                             |

|          | 1(10)       |                                                |                             |

AN1820

MOTOROLA

#### **Application Note**

| ; SDA to stak<br>; Completely                     | oilize in sl<br>arbitrary d | =-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-       |

|---------------------------------------------------|-----------------------------|----------------------------------------------|

| ;-=-=-=-===<br>I2CSetupDelay<br>NOP<br>NOP<br>RTS |                             |                                              |

| ; SCL frequer                                     | ncy                         | approximately) the desired<br>ry (16 cycles) |

| *<br>* Vector Defi<br>*                           | nitions                     |                                              |

| ORG<br>FDB                                        | \$07FE<br>Start             | ;Reset vector                                |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights or the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death masociated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and  $\widehat{A}$  are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution, P.O. Box 5405, Denver, Colorado 80217, 1-303-675-2140 or 1-800-441-2447. Customer Focus Center, 1-800-521-6274

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu, Minato-ku, Tokyo, 106-8573 Japan. 81-3-3440-8573

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852-26668334

Mfax<sup>™</sup>, Motorola Fax Back System: RMFAX0@email.sps.mot.com; http://sps.motorola.com/mfax/; TOUCHTONE, 1-602-244-6609; US and Canada ONLY, 1-800-774-1848

HOME PAGE: http://motorola.com/sps/

Mfax is a trademark of Motorola, Inc.

© Motorola, Inc., 1999

AN1820/D

For More Information On This Product, Go to: www.freescale.com