# **ADC803**

# High-Speed ANALOG-TO-DIGITAL CONVERTER

## **FEATURES**

- 12-BIT RESOLUTION

- ±0.012% LINEARITY ERROR MAXIMUM (C GRADE)

- NO MISSING CODES -55°C to +125°C (S GRADE)

- HIGH SINAD RATIO: 72dB

- LOW HARMONIC DISTORTION: -73dB

- CONVERSION TIME: 500ns, 8 bits 670ns, 10 bits 1.5\(\mu\s,\) 12 bits

### DESCRIPTION

The ADC803 is a high speed successive approximation analog-to-digital converter utilizing state-of-the-art IC and laser-trimmed thin film components.

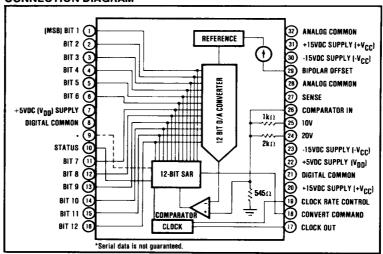

It is complete with internal reference, clock, and comparator and is packaged in a 32-pin metal package. Conversion time is set at the factory to  $1.5\mu s$ .

With user-adjusted conversion time set at  $l\mu s$ ,  $\pm 1LSB$  accuracy can be achieved. The gain and offset errors may be externally trimmed to zero.

Internal scaling resistors are provided for the selection of analog signal input ranges of 0V to -10V,  $\pm 5V$ , and  $\pm 10V$ .

Output codes available are complementary binary for unipolar inputs and bipolar offset binary for bipolar inputs.

All digital inputs and outputs are TTL-compatible. Power supply requirements are  $\pm 15V$  and  $\pm 5V$ .

PDS-493D

Burr-Brown IC Data Book

9.2-124

## **SPECIFICATIONS**

#### **ELECTRICAL**

At +25°C, rated power supplies, 1.5µs conversion time, and after 6-minute warm-up unless otherwise noted.

| MODEL                                                 |          | ADC803CM |              | ADC803BM     |               | ADC8038M        |               |          |        |                                         |

|-------------------------------------------------------|----------|----------|--------------|--------------|---------------|-----------------|---------------|----------|--------|-----------------------------------------|

|                                                       | MIN      | TYP      | MAX          | MIN          | TYP           | MAX             | MIN           | TYP      | MAX    | UNITS                                   |

| RESOLUTION                                            |          |          | 12           |              |               | 12              |               |          | 12     | Bits                                    |

| INPUTS                                                |          |          |              |              |               |                 |               |          |        |                                         |

| ANALOG                                                |          |          |              |              |               |                 |               |          |        | .,                                      |

| Voltage Ranges: Bipolar                               |          | ±5, ±10  |              |              | ٠ .           |                 |               | •        |        | V                                       |

| Unipolar                                              |          | 0 to -10 |              |              | ٠ .           |                 |               | •        |        | V                                       |

| Impedance: -10V to 0V, ±5V                            | l .      | 1.4      |              |              |               |                 |               |          |        | kΩ                                      |

| ±10V                                                  |          | 2.4      |              |              | •             |                 |               |          |        | kΩ                                      |

| DIGITAL                                               |          |          |              |              | l             |                 |               |          |        |                                         |

| Convert Command                                       | !        | Negati   | ve pulse 50r | is wide (mir | ) trailing ed | ige (U to 1) in | iitiates conv | ersion.  |        | TTL Loads                               |

| Logic Loading                                         |          |          | 4            |              | L             |                 |               | •        |        | I I L LOROS                             |

| TRANSFER CHARACTERISTICS                              |          |          |              |              |               |                 |               |          |        |                                         |

| ACCURACY                                              |          |          |              |              | ±0.08         | +0.2            |               | +0.04    | +0.1   | %                                       |

| Gain Error <sup>(1)</sup>                             | 1        | ±0.04    | ±0.1         |              |               | ±0.2<br>±0.3    |               | 70.04    | +0.1   | % of FSR®                               |

| Offset Error <sup>(1)</sup> : Unipolar                | 1        | ±0.05    | ±0.2         |              | ±0.07         | ±0.3<br>±0.2    |               |          |        | % of FSR                                |

| Bipolar                                               | 1        | ±0.02    | ±0.1         |              | ı •           | ±0.2            |               | •        | _      | 70 U F 3 N                              |

| Linearity Error:                                      | 1        |          |              |              |               | ±0.020          |               | ±0.012   | ±0.015 | % of FSR                                |

| 1.5µs Conversion Time                                 | 1        | ±0.009   | ±0.012       | 1            | ±0.020        | ±0.020          |               | ±0.012   | 10.013 | % of FSR                                |

| 1.0µs Conversion Time                                 | 1        | ±0.015   | ±0.020       | 1            | ±0.020        | l               |               |          |        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| Differential Linearity Error:                         | 1        | +0.010   | ±0.015       | 1            | 1             | ±0.020          | 1             |          |        | % of FSR                                |

| 1.5µs Conversion Time                                 | 1        | ±0.012   |              |              | ±0.024        | ±0.020          |               | ;        |        | % of FSR                                |

| 1.0µs Conversion Time                                 | l        | 1/2      | ±0.024       |              | ±0.024        |                 |               | •        |        | LSB                                     |

| Inherent Quantization Error                           | <u> </u> | 1/2      |              |              | <u> </u>      | <u> </u>        |               | <u> </u> |        | - 205                                   |

| POWER SUPPLY SENSITIVITY                              |          |          |              |              |               |                 |               | ١.       |        | % of FSR/%V                             |

| Gain and Offset: +15VDC                               |          | ±0.0036  |              |              |               | ļ               | l             | :        |        | % of FSR/%V                             |

| -15VDC                                                |          | ±0.0005  |              |              |               | 1               | ł             | l I      |        | % of FSR/%V                             |

| +5VDC                                                 |          | ±0.001   |              | 1            |               |                 |               | :        |        | %/%Vcc                                  |

| Conversion Time: +15VDC                               |          | ±0.7     |              | i            |               | i               | i             | 1 :      |        | %/%Vcc                                  |

| -15VDC                                                |          | None     |              | 1            | !             | 1               |               | 1 :      |        | %/%Vcc<br>%/%Vpp                        |

| +5VDC                                                 |          | ±0.8     |              |              |               |                 |               | · -      |        | 70/70 400                               |

| CONVERSION TIME                                       |          |          | 1.5          |              |               |                 | ١.            |          |        | μ8                                      |

| Factory Set                                           | 1.3      | 1        | 2.2          |              |               |                 |               |          |        | μ8                                      |

| Range of Adjustments                                  | 0.8      | <u> </u> | 2.2          | <u> </u>     | ļ             |                 |               | ļ        |        | — <del></del>                           |

| DRIFT                                                 |          | ±10      | ±30          |              | ±15           |                 |               |          |        | ppm of FSR/9                            |

| Gain                                                  |          | ±10      | ±30          |              | ±3            |                 |               |          |        | ppm of FSR/s                            |

| Offset: Unipolar                                      | ļ        | ±2       | ±10          |              | ±5            |                 |               |          |        | ppm of FSR/s                            |

| Bipolar<br>Linearity Error                            | i        | 1 =3     | -''          |              | +             | i               |               |          | ł      |                                         |

| -25°C to +85°C:                                       | 1        | 1        | I            | 1            | 1             |                 |               |          | 1      | 1                                       |

| 1.5us Conversion Time                                 | 1        | ±0.012   | ±0.018       |              | 1             | ±0.024          |               |          |        | % of FSR                                |

| 1.0µs Conversion Time                                 |          | ±0.012   | 1 -0.0.0     |              | ±0.020        |                 |               |          |        | % of FSR                                |

| -55°C to +125°C:                                      |          | 1 -0.0,5 | i            |              | 1 -5.020      |                 |               |          | l      |                                         |

| 1.7us Conversion Time.                                |          | 1        | 1            |              | 1             |                 |               |          | l      |                                         |

| max. <sup>(4)</sup>                                   |          | 1        | 1            |              | 1             |                 |               | ±.015    | ±.024  | % of FSR                                |

| max. Differential Linearity Error                     |          | 1        | 1            |              | 1             |                 |               |          |        |                                         |

| -25°C to +85°C:                                       |          | i        |              |              | 1             |                 |               |          | l      |                                         |

| 1.5µs Conversion,Time                                 |          | ±0.012   | ±0.018       |              | 1             | ±0.024          |               | 1        | l      | % of FSR                                |

| 1.0us Conversion Time                                 | 1        | ±0.012   |              | 1            | ±0.024        |                 | 1             | ł        |        | % of FSR                                |

| -55°C to +125°C:                                      |          | 1 -0.013 |              |              | 10.024        | 1               |               | 1        |        |                                         |

| 1.7µs Conversion Time,                                | 1        | 1        | 1            | 1            |               |                 |               | 1        | 1      | 1                                       |

| 1.7µs Conversion 1 Ime,<br>max <sup>(4)</sup>         | 1        | 1        | I            | 1            |               | 1               |               | ±.015    | ±.024  | % of FSR                                |

| max*** Conversion Time                                |          | ±0.1     |              |              |               | 1               |               | 1        |        | % of FSR                                |

|                                                       |          | 1 10.1   |              | 1            |               | 1               | 1             | 1        |        | 1                                       |

| No Missing Code Temp. Range:<br>1,5µs Conversion Time | -25      |          | +85          |              | 1             |                 |               | 1        |        | °C                                      |

|                                                       |          | 1        | , 00         | 1            | i .           | 1               | 1             | I        | I      |                                         |

| 1.7µs Conversion Time,                                | 1        | 1        |              |              | 1             |                 |               | 1        | 1      |                                         |

ADC803 dynamic performance characteristics are described in a report titled "Analogue-to-Digital Converter Performance Tests Using the Fast Fourier Transform" by R. A. Belcher, University College of Swansea, Wales, U.K. (available from Burr-Brown on letterhead request).

| MODEL                        | ADC803CM |              | ADC803BM    |     | ADC803SM |     | •   |       |      |           |

|------------------------------|----------|--------------|-------------|-----|----------|-----|-----|-------|------|-----------|

|                              | MIN      | TYP          | MAX         | MIN | TYP      | MAX | MIN | TYP   | MAX  | UNITS     |

| OUTPUT                       |          |              |             |     | •        | •   |     |       |      |           |

| DIGITAL DATA<br>Parallel     |          |              |             |     |          |     |     |       |      |           |

| Output Codes: Unipolar       | Complem  | entary Stra  | ight Binary |     | *        | l   |     | *     |      |           |

| Bipolar                      | Bipo     | lar Offset E | inary       |     | *        |     |     |       |      |           |

| Output Drive                 | 6        | l            | 1 1         | •   |          |     |     | 1     |      | TTL Loads |

| Status                       | Logic "1 | " during Co  | nversion    |     | •        |     | 1   |       |      |           |

| Status Output Drive          | 6        | ł            | 1           | •   | 1        | ļ   |     |       |      | TTL Loads |

| Internal Clock:              | 1        |              | } I         |     |          | ĺ   |     |       |      |           |

| Clock Output Drive           | 3        |              | 1 1         |     |          |     |     |       | !    | TTL Loads |

| Frequency (without external  |          |              | l i         |     |          |     |     |       |      |           |

| clock adjustment)            | 1        | 8            | 1 1         | İ   | ٠ .      | ł   |     | *     |      | MHz       |

| POWER SUPPLY REQUIREMENT     | s        |              |             |     |          |     | •   |       |      |           |

| Power Consumption            |          |              |             |     |          |     | l   |       |      |           |

| Rated Voltage: Analog (±Vcc) | ±14.25   | ±15.0        | ±15.75      |     | •        |     |     |       | !    | VDC       |

| Digital (V <sub>DO</sub> )   | +4.75    | +5.0         | +5.25       | •   |          |     |     |       | *    | VDC       |

| Supply Drain: +15V           | 1        | +27          | +32         |     | •        | *   | ĺ   |       |      | mA        |

| -15V                         | 1        | -38          | 55          |     | *        |     |     | ( • I | *    | mA        |

| +5V                          |          | +180         | +210        |     |          |     | ļ   |       | *    | mA        |

| TEMPERATURE RANGE (AMBIEN    | IT)      |              |             |     |          |     |     |       |      |           |

| Specification                | 25       |              | +85         | •   |          | *   | -55 |       | +125 | °C        |

| Storage                      | 55       |              | +125        |     |          | *   | *   |       |      | °C        |

<sup>\*</sup>Same specification as for ADC803CM

NOTES: (1) Adjustable to zero. See Optional Gain and Offset Adjustment section. (2) FSR means Full Scale Range. For example, unit connected for ±10V has 20V FSR. (3) See Optional Clock Rate Control section. For faster conversion time at less resolution, see section on External Short Cycle. (4) Conversion time is factory-set at approximately 1.4 $\mu$ s at +25°C at semperature increases, the conversion time increases. At +125°C the conversion time will be no more than 1.7 $\mu$ s. No Missing Codes is guaranteed over -55°C to +125°C provided the conversion time is allowed to increase with temperature.

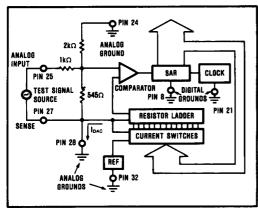

#### **CONNECTION DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Analog Supply Voltage To Analog Common   | ±18V  |

|------------------------------------------|-------|

| Digital Supply Voltage To Digital Common | . +7V |

| Digital Controls Inputs                  | +5.5V |

| Analog Inputs                            | ±15V  |

| Operating Temperature: Ambient+          | 125°C |

| Case +                                   |       |

| Storage Temperature                      | 125°C |

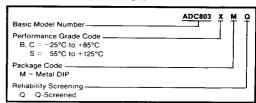

#### ORDERING INFORMATION

Burr-Brown IC Data Book

9.2-126

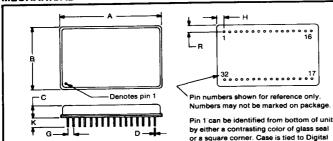

Common.

connected to case.

NOTE: Leads in true position within 0.10" (0.25mm) R at MMC at seating plane. Pin 8

PINS: Pin material and plating composition conform to method 2003 (solderability) of MIL-STD-883 (except paragraph 3.2) CASE: Kovar, Nickel plated HERMETICITY: Gross Leak Test MATING CONNECTOR: 2302MC Set of two 16-pin strips WEIGHT: 13 grams (0.46 oz.)

|     | 4410   | HES   | MILLIMETERS |       |  |  |

|-----|--------|-------|-------------|-------|--|--|

|     | INC    | HES   | MILLIMETERS |       |  |  |

| DIM | MIN    | MAX   | MIN         | MAX   |  |  |

| A   | 1.720  | 1.760 | 43.69       | 44.70 |  |  |

| в   | 1.120  | 1.160 | 28.45       | 29.46 |  |  |

| С   | .170   | .250  | 4.32        | 6.35  |  |  |

| ь   | .016   | .021  | 0.41        | 0.53  |  |  |

| G   | .100 B | ASIC  | 2.54 B      | ASIC  |  |  |

| н   | .100   | .140  | 2.54        | 3.56  |  |  |

| к   | .150   | .300  | 3.81        | 7.62  |  |  |

| L   | .900 B | ASIC  | 22.86 B     | ASIC  |  |  |

| R   | .100   | .140  | 2.54        | 3.56  |  |  |

## THEORY OF OPERATION

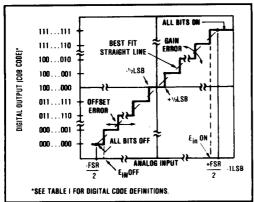

The accuracy of a successive approximation analog-todigital converter is described by the transfer function shown in Figure 1. All successive approximation A/D converters have an inherent Quantization Error of ±1/2LSB. The remaining errors in the A/D converter are combinations of analog errors due to the linear circuitry matching and tracking properties of the ladder and scaling networks, power supply rejection, reference errors and the dynamic errors of the DAC and comparator. In summary, these errors consist of initial errors including Gain, Offset, Linearity, Differential Linearity, and Power Supply Sensitivity. Initial Gain and Offset errors may be adjusted to zero. Gain drift over temperature rotates the transfer function (Figure 1) about the zero point and Offset drift shifts the transfer function left or right over the operating temperature range. Linearity error is not adjustable but it is the most meaningful indicator of A/D converter accuracy. Linearity error is the deviation of an actual bit transition from the best fit straight line transfer function of the A/D converter. A Differential Linearity error of

FIGURE 1. Input versus Output for an Ideal Bipolar A/D Converter.

$\pm 1/2$ LSB means that the width of each bit step over the range of the A/D converter is 1LSB,  $\pm 1/2$ LSB. The ADC803 is guaranteed to have no missing codes over the specified temperature range.

#### **TIMING CONSIDERATIONS**

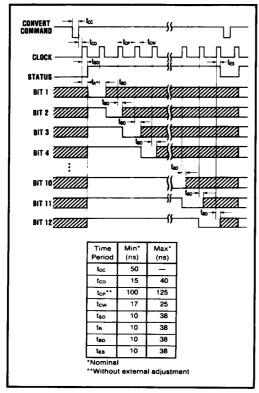

The timing diagram (Figure 2) shows the relationship between the convert command, clock and outputs. The digital output word is positive true logic for bipolar operation and complementary logic for unipolar operation.

The following are some important notes on the ADC803 timing. The times given are typical unless otherwise noted. Nominal maximum and minimum times are also given in Figure 2.

- When power is first applied, the status of the ADC803 will be undetermined. A CONVERT COMMAND must be applied to initialize the ADC803.

- The CONVERT COMMAND must be low at least 50nsec prior to the "0" to "1" edge that starts a conversion.

- 3. The clock runs continuously when the initial CON-VERT COMMAND goes high and whenever the CONVERT COMMAND is high thereafter. It does not run when CONVERT COMMAND is low. It may be beneficial to keep CONVERT COMMAND low except during conversions to limit the digital noise induced in the ground and power supply lines.

- 4. The clock starts 25ns after the "0" to "1" transition of the CONVERT COMMAND.

- 5. Parallel Output Data: The Successive Approximation Register (SAR) is reset 26ns after the leading edge of the first clock period in the conversion cycle. The MSB is set to logic "0" and all other bits are set to logic "1". The bits are determined in succession starting with the MSB, Bit 1, as shown in Figure 2. Each bit will be valid 26ns after its corresponding clock pulse.

The falling edge of the STATUS signal should not be used to strobe parallel data out of the ADC803

FIGURE 2. ADC803 Timing Diagram.

directly. The table in Figure 2 indicates that the falling edge of STATUS may occur prior to bit 12 data becoming valid.

- STATUS goes high 26ns after the leading edge of the first clock pulse and goes low 18ns after the leading edge of the last clock pulse.

- Bit 12 will become valid at about the same time STATUS goes low and a new conversion can be initiated at anytime after the output data has been read.

- 8. The converter may be restarted during a conversion. When CONVERT COMMAND makes a "0" to "1" transition after the minimum set-up time, the SAR will be reset and a new conversion will start regardless of the state of the converter prior to the CONVERT COMMAND being received.

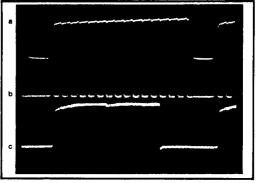

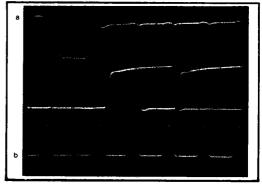

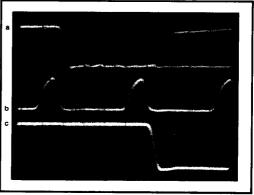

Figures 3, 4, and 5 are photographs of the actual pulse shapes and relationships.

FIGURE 3. Photo of (a) Convert Command, (b) Clock, and (c) Status (200ns/div).

FIGURE 4. Photo of (a) Convert Command, (b) Clock (50ns/div).

FIGURE 5. Photo of (a) Bit-12 Data (Parallel), (b) Clock, and (c) Status (20ns/div).

# DIGITAL CODES Parallel Data

Two binary codes are available on the ADC803 parallel output; they are complementary straight binary (Logic "0" true) for unipolar input signal ranges and bipolar offset binary (Logic "1" true) for bipolar input signal ranges. Binary two's complement may be obtained for bipolar input ranges by inverting the MSB. It should be noted that for unipolar input ranges -10 volts is full scale.

Table 1 shows the LSB, transition values, and code definitions for each possible analog signal range.

TABLE I. Input Voltages, Transition Values, LSB Values, and Code Definitions.

| Analog Input<br>Voltage Range                     | ±10V                                      | ±5V                                     | 0 to -10V                                |

|---------------------------------------------------|-------------------------------------------|-----------------------------------------|------------------------------------------|

| Code<br>Designation                               | BOB(1)<br>or BTC(2)                       | BOB<br>or BTC                           | CSB(3)                                   |

| One Least<br>Significant<br>Bit (LSB)             | 4.88mV                                    | 2.44mV                                  | 2.44mV                                   |

| Transition Values MSB LSB(4) 000000 000011 110000 | -10V + 1/2LSB<br>-1/2LSB<br>+10V - 3/2LSB | -5V + 1/2LSB<br>-1/2LSB<br>+5V - 3/2LSB | -10V + 3/2LSB<br>-5V + 1/2LSB<br>-1/2LSB |

| 111111                                            |                                           |                                         |                                          |

NOTES: 1. BOB = Bipolar Offset Binary.

- BTC = Binary Two's Complement (obtained by inverting the most significant bit (pin 1).

- 3. CSB = Complementary Straight Binary.

- Voltages given are the nominal value for the transition from the next lower code.

#### Serial Data (NRZ)

ADC803 serial data operation is not guaranteed. To operate in serial output mode a pin-for-pin replacement ADC806 is recommended.

# DISCUSSION OF SPECIFICATIONS

The ADC803 is specified to meet critical performance criteria for a wide variety of applications. The most critical specifications for an A/D converter are Linearity, Drift, Gain and Offset errors, and Conversion speed effects on accuracy. This ADC is factory-trimmed and tested for all critical key specifications.

#### GAIN AND OFFSET ERROR

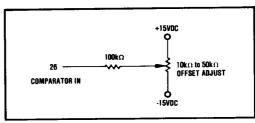

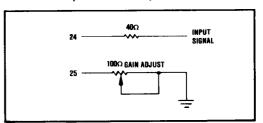

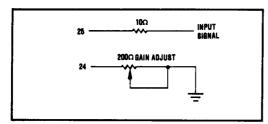

Initial Gain and Offset errors are factory-trimmed to typically  $\pm 0.05\%$  of FSR at  $25^{\circ}$ C. These errors may be trimmed to zero by connecting external trim potentiometers as shown in Figures 10, 11, and 12.

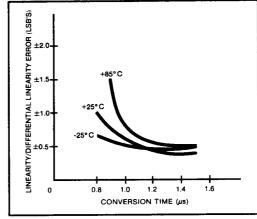

### **ACCURACY VERSUS CONVERSION TIME**

In successive approximation A/D converters, the conversion time affects Linearity and Differential Linearity errors. Conversion time and its effect on Linearity and

Differential Linearity errors for the ADC803 are shown in Figure 6.

FIGURE 6. Linearity and Differential Linearity Error versus Conversion Time.

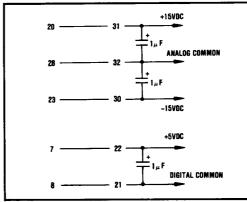

#### POWER SUPPLY SENSITIVITY

Changes in the DC power supply voltages will affect accuracy. Normally, regulated power supplies with 1% or less ripple are recommended for use with this ADC. See Layout Precautions, Power Supply Decoupling, and Figure 7.

FIGURE 7. Recommended Power Supply Decoupling.

#### **LINEARITY ERROR**

Linearity error is not adjustable by the user. Linearity is the deviation of an actual bit transition from the best fit straight line value at any level over the range of the A/D converter.

#### **DIFFERENTIAL LINEARITY ERROR**

Differential Linearity describes the step size between transition values. A Differential Linearity error of

9.2-129

$\pm 1/2$ LSB indicates that the size of any step may not vary from 1LSB by more than  $\pm 1/2$ LSB.

#### **ENVIRONMENTAL SCREENING**

Q screening is now available for all models of the ADC803 family. The Q-screened versions have the same specifications as the unscreened versions listed in the Specifications table.

#### **Q** Screening

Burr-Brown Q-screened models are environmentally-screened versions of our standard industrial products, designed to provide enhanced reliability. The screening, tabulated below, is performed to selected methods of MIL-STD-883. Reference to these methods provides a convenient method of communicating the screening levels and basic procedures employed; it does not imply conformance to any other military standards or to any methods of MIL-STD-883 other than those listed below. Burr-Brown's detailed procedures may vary slightly from those of MIL-STD-883.

#### SCREENING FLOW FOR ADC8030

| Şcreen                                        | Method<br>Burr-Brown or<br>MIL-STD-883 | Condition                                       |

|-----------------------------------------------|----------------------------------------|-------------------------------------------------|

| Internal Visual                               | Burr-Brown QC4118                      |                                                 |

| High Temperature Storage (Stabilization Bake) | 1008                                   | B<br>(150°C, 24hr)                              |

| Temperature<br>Cycling                        | 1010                                   | B (10cy,<br>-55°C to +125°C)                    |

| Constant Acceleration                         | 2001                                   | (2000G, Y1 axis)                                |

| Burn-in<br>ADC803BMQ, CMQ<br>ADC803SMQ        | 1015                                   | D<br>(160 hrs, +85°C)<br>(160 hrs, +125°C)      |

| Electrical Test                               | Burr-Brown<br>Test Specification       |                                                 |

| Hermeticity<br>Fine Leak<br>Gross Leak        | 1014                                   | A1 or A2 (Helium,<br>5 × 10 <sup>-7</sup> cc/s) |

|                                               |                                        | Ü                                               |

| Final Electrical                              | Burr-Brown<br>Test Specification       |                                                 |

| External Visual                               | Burr-Brown QC5150                      |                                                 |

# LAYOUT AND OPERATING INSTRUCTIONS

### **LAYOUT PRECAUTIONS**

The ADC803 is a high speed analog-to-digital converter which requires more layout precautions than general purpose products.

The ADC803 has two pins for analog common, two pins for digital common, and two pins for each power supply input. Each pair of these pins must be connected together externally. The connection between the digital supply pins and the connection between the digital common pins must be as short as possible. The analog and digital

commons are not connected together internally in the ADC803, but should be connected together externally to a ground plane.

Connecting all commons to a ground plane at the ADC803 is the best method to minimize noise and dissipate heat. Pin 8 (Digital Common) is internally connected to the case.

The ADC803 also has an analog common Sense input (pin 27) for the analog input. This sense pin must be connected to analog common as close to the input signal source as possible or connected to the ground plane. Low impedance analog and digital common returns are essential for low noise performance. Coupling between analog inputs and digital lines should be minimized by careful layout. Special attention should be taken to ensure that the clock noise on the +5V supply line does not couple into the analog inputs.

The Comparator input (pin 26) is extremely sensitive to noise. Any connection to this point should be as short as possible and shielded by analog common or ±15VDC supply patterns. The Clock Output (pin 17) is sensitive to stray capacitance; capacitance on this pin could alter the clock wave shape.

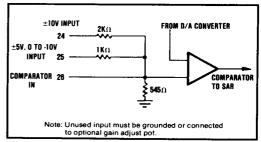

#### POWER SUPPLY DECOUPLING

The power supplies should be bypassed with  $1\mu$ F tantalum capacitors as shown in Figure 8 to obtain noise-free operation. These capacitors should be located close to the ADC.

FIGURE 8. Input Scaling Circuit.

#### INPUT SCALING

The analog input should be scaled as close to the maximum input signal range as possible in order to utilize the maximum signal resolution of the A/D converter. Connect the input signals as shown in Table II. See Figure 8 for circuit details.

#### **OUTPUT DRIVE**

All ADC803 outputs except the clock will drive six TTL loads; the clock will drive three TTL loads. If long digital lines must be driven, external logic buffers are required particularly for the clock which is sensitive to capacitive loading.

TABLE II. ADC803 Input Scaling Connections.

| Input<br>Signal<br>Range | Output<br>Code    | Connect<br>Pin 29<br>To | With<br>Gain<br>Adjust | Connect<br>Pin 24<br>To                        | Connect<br>Pin 25<br>To                        |

|--------------------------|-------------------|-------------------------|------------------------|------------------------------------------------|------------------------------------------------|

| ±10V                     | BOB<br>or<br>BTC* | 26                      | Yes                    | 40Ω resistor in<br>series with<br>input signal | Gain Adjust<br>Potentiometer                   |

|                          |                   |                         | No                     | Input Signal                                   | Analog<br>Common                               |

| ±5V                      | BOB<br>or<br>BTC* | 26                      | Yes                    | Gain Adjust<br>Potentiometer                   | 10Ω resistor in<br>series with<br>input signal |

| ļ                        |                   |                         | No                     | Analog<br>Common                               | Input Signal                                   |

| 0 to-10V                 | CSB               | Analog<br>Common        | Yes                    | Gain Adjust<br>Potentiometer                   | 10Ω resistor in<br>series with<br>input signal |

|                          |                   |                         | No                     | Analog<br>Common                               | Input Signal                                   |

<sup>\*</sup>Obtained by inverting MSB (pin 1) externally.

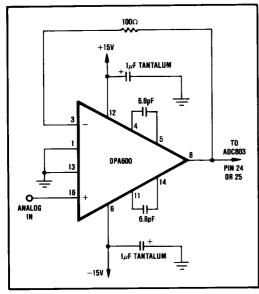

#### INPUT IMPEDANCE

The source impedance to the ADC803 should be low, such as the output of an op amp, to avoid any errors due to the relatively low input impedance of the ADC803.

If this impedance is not low, a buffer amplifier should be added between the input signal and the ADC803 input as shown in Figure 9.

FIGURE 9. Source Impedance Buffering.

A common problem with successive approximation A/D converters is the transients in input current caused by the comparator input being switched back and forth. This requires a fast settling amplifier to drive the input.

The ADC803 comparator is connected in a differential mode (see Figure 8), greatly reducing the size of the input transients. The user, therefore, may use a fast settling wideband operational amplifier to drive the ADC803. The small signal settling time of the amplifier should be less than 100ns.

# OPTIONAL EXTERNAL GAIN AND OFFSET ADJUSTMENTS

Gain and Offset errors may be trimmed to zero using external trim potentiometers connected to the ADC as shown in Figures 10, 11, and 12. For proper gain adjust range a series resistor must be connected to the analog input pin as specified in Table II and shown in Figures 11 and 12. Multiturn potentiometers with  $100\text{ppm}/^{\circ}\text{C}$  or better TCR's are recommended for minimum drift over temperature and time. All resistors should be  $\pm 1\%$  metal film or better. If the Offset adjust is not used, pin 26 should be left open except for bipolar operation when it is connected to pin 29. If the Gain adjust is not used, the unused input (pin 24 or 25) must be grounded to meet specified gain accuracy.

#### **Adjustment Procedure**

Refer to Table I for LSB voltages and transition values. Unipolar offset - connect the offset potentiometer and resistors as shown in Figure II, sweep the input through the end point transition voltage, from 111...110 to 111...111. Adjust the Offset potentiometer until the actual end point transition voltage occurs at -1/2LSB.

Bipolar offset - connect the offset potentiometer and resistors as shown in Figure 10. Sweep the input through zero and adjust the offset potention.eter until the transition from 0111 1111 1111 to 1000 0000 0000 occurs at -1/2LSB.

FIGURE 10. Optional Offset Adjust

FIGURE 11. Optional Gain Adjust for ±10V Bipolar Operation.

FIGURE 12. Optional Gain Adjust for ±5V Bipolar or 0 to -10V Unipolar Operation.

Gain - connect the Gain potentiometer as shown in Figure 11 or 12. Sweep the input through the end point transition voltage that should cause an output transition from 000...001 to 000...001. Adjust the Gain potentiometer until this transition occurs at the correct end point trans. On voltage as given in Table 1.

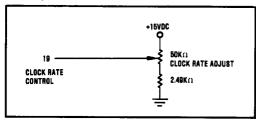

#### **OPTIONAL CLOCK RATE CONTROL**

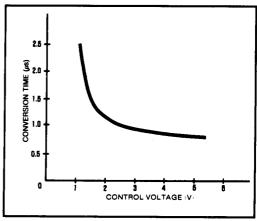

The clock is factory-set for a conversion time between  $1.3\mu s$  and  $1.5\mu s$ . By use of the optional Clock Rate Control as shown in Figure 13, the Conversion time can be adjusted down to  $0.8\mu s$  for 12-bit resolution. If the optional Clock Rate Control is not used, pin 19 should be left open. Figure 14 shows Conversion Time versus Clock Rate Control voltage and Figure 6 shows Differential Linearity error versus Conversion time.

FIGURE 13. Optional Clock Rate Control.

#### **POWER DISSIPATION**

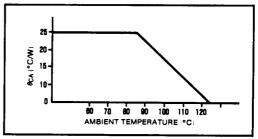

The ADC803 dissipates approximately 1.9W (typical) and the package has a case-to-ambient thermal resistance  $(\theta_{CA})$  of  $25^{\circ}\text{C/W}$ . For operation above  $+85^{\circ}\text{C}$ ,  $\theta_{CA}$  should be lowered by a heat sink or by forced air over the surface of the package. See Figure 15 for  $\theta_{CA}$  requirements above  $+85^{\circ}\text{C}$ . Improved thermal contact with the PC card copper ground plane under the case can be achieved using a silicone heat sink compound. On a 0.062" thick PC card with a 16-square-inch (minimum) area, this technique will allow operation to  $+100^{\circ}\text{C}$ . Forced air plus heat sink is recommended for  $+125^{\circ}\text{C}$  operation.

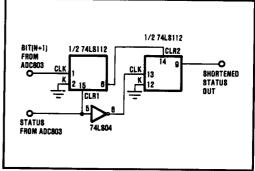

#### **EXTERNAL SHORT CYCLE**

If less than 12 bits of resolution is required, the cycle time of the ADC803 can be shortened with the addition of two external components as shown in Figure 16. This circuit will create a shortened status signal directly proportional

FIGURE 14. Conversion Time versus Clock Rate Control Voltage.

FIGURE 15.  $\theta_{CA}$  Requirement Above +85°C.

to the reduction of resolution. For n bits of resolution, the n+1 bit is used to create the falling edge of the shortened status signal. It is possible to obtain the equivalent of a 10-bit converter with 670ns conversion time and an 8-bit converter with 500ns conversion time using this short cycle technique and the external clock rate control shown in Figure 13. To begin a new conversion, simply give the converter a new convert command pulse. The SAR will reset and a new conversion will begin.

FIGURE 16. External Short Cycle Circuit.

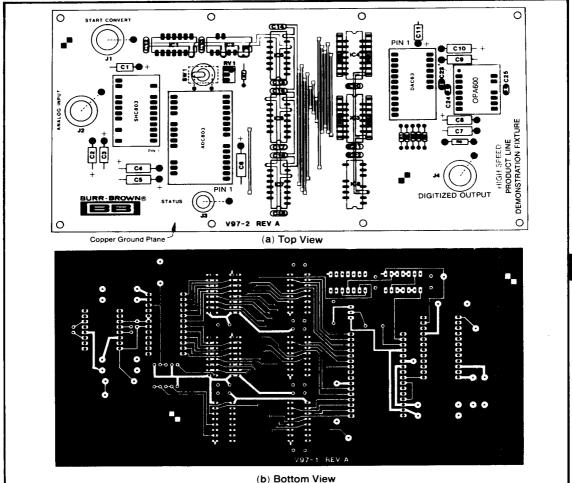

## **TESTING OF THE ADC803**

In order to validate the test results of the ADC803 obtained during final test, the customer must take extreme care in the design and layout of his test fixtures. Proper grounding, correct routing of analog and digital signals and power supply bypassing are crucial in achieving successful results.

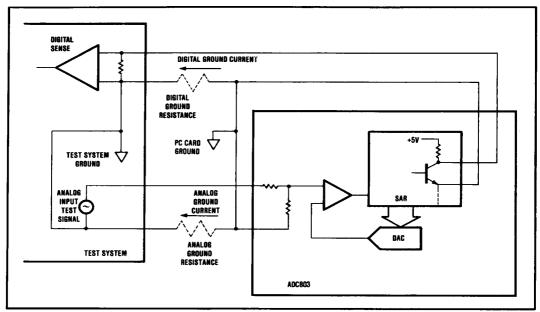

#### ANALOG GROUND, DIGITAL GROUND, SENSE

Figure 17 shows a simplified model of the ADC depicting proper analog and digital grounding. Several analog and digital ground pins have been provided to allow for optimizing the internal layout of the ADC. As will be explained in more detail later, analog and digital grounds should be connected together only at one point by an extremely low resistive and inductive connection (a ground plane is ideal). A special analog ground called "sense" has been provided to eliminate the voltage drop that would otherwise be in the ground return of the R-2R ladder. Measuring the input signal with respect to the sense terminal makes the measurement independent of the impedance that is developed in the connection between the sense terminal and the analog ground, pin 28.

# ANALOG-TO-DIGITAL CONVERTER TEST TECHNIQUE

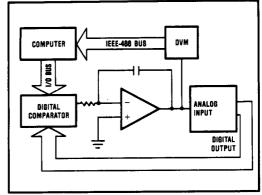

A very effective way of determining the DC performance of an ADC is by using the "servo loop method." The block diagram of this technique is shown in Figure 18. This measurement system automatically locates the analog voltage that causes the digital output to alternate between the desired code and the adjacent code. The

FIGURE 17. Simplified Model of ADC803 Depicting Proper Analog and Digital Ground.

FIGURE 18. Servo Loop Analog-to-Digital Tester.

computer is programmed to place the desired code on the I/O bus which is one set of inputs to the digital comparator. The other set of inputs to this comparator is the digital output of the ADC. Depending upon the result of this comparison, the integrator is directed to change its output until an equilibrium state is achieved. Once in equilibrium, the DVM measures the analog input to the ADC and transmits the information to the computer via the IEEE-488 bus. The test program checks all the desired code combinations, verifying the performance of the ADC. Test time will range from 10 seconds to several minutes depending on the speed of the test program, settling time of the DVM, and number of codes to be checked.

#### **GROUND LOOPS**

Figure 19 illustrates the interaction that occurs between the analog and digital grounds when an ADC is connected into a test circuit. This interaction is created by ground loops. The circuit in Figure 19 shows how ground loops are created when the ADC tester combines digital and analog portions of the circuit together—in this case, the test signal generator (analog) and the digital circuitry that detects the ADC code which corresponds to the analog signal (digital). The ground loop exists when the digital ground connection between the ADC and the tester is in parallel with the analog grounds that connect the tester with the ADC. When the connection is made in this manner some of the digital current is diverted into the analog signal return, which creates a code-dependent error signal due to the resistance in the analog signal return. This error distorts the linearity measurement and induces hysterisis. The error can be substantially reduced if the analog and digital grounds are isolated from each other in the ADC tester.

FIGURE 19. Ground Loop Interaction Between Analog and Digital Grounds When ADC Is Connected Into Test Circuit.

#### **BEAT FREQUENCY TEST**

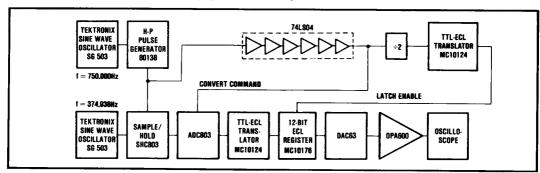

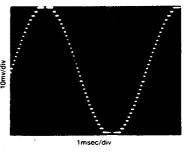

A "beat frequency test" applied to an ADC803 with a companion sample hold illustrates both an effective means of testing the high frequency performance of such a system and demonstrating that the ADC803 with its associated sample/hold is capable of digitizing high frequency signals cleanly. A sample/hold must be used when performing this test to hold the input of the ADC803 constant during the conversion time. Figure 20 is a block diagram of the beat frequency test setup.

The beat frequency test is useful for being able to rapidly determine whether there are any serious problems with the ADC. In this test the input frequency is set at slightly less than one-half the sampling rate. The slight difference is selected to allow the sample point to vary by 1LSB, or

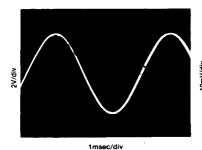

less, on successive samples. The data is clocked into a low frequency reconstruction DAC at one-half the sampling rate to enable viewing on an oscilloscope. Figure 21 is a photograph of the response to a full-scale input sine wave centered around the MSB and Figure 22 is a photograph of the response of a small signal sine wave centered around the MSB. For comparison, a photograph (Figure 23) is included which shows the response of the ADC803 to a 125Hz input signal which is the same as the beat frequency.

Figure 24 is the PC card layout that was used for the beat frequency test. This layout demonstrates some of the layout practices that must be followed when using a high speed ADC like the ADC803.

FIGURE 20. Block Diagram of Beat Frequency Test Circuit.

Burr-Brown IC Data Book

9.2-134

1msec/div

FIGURE 21. Beat Frequency Test Response of Full Scale Sine Wave Input.

FIGURE 22. Beat Frequency Test Response of Small Signal Sine Wave Input.

FIGURE 23. Response of Small Signal 125Hz Sine Wave Input.

FIGURE 24. PC Board Layout for Beat Frequency Test Fixture.