# MC13202

2.4 GHz Low Power Transceiver for the IEEE® 802.15.4 Standard

Reference Manual

Document Number: MC13202RM

Rev. 1.1 04/2008

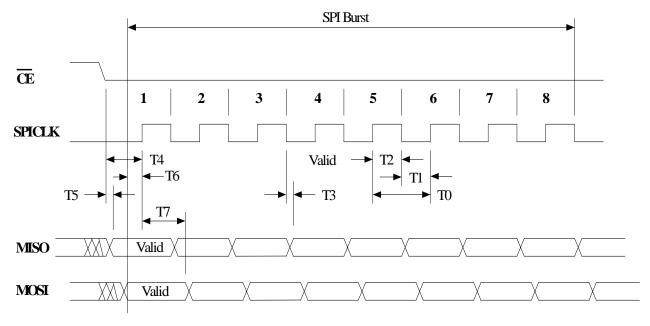

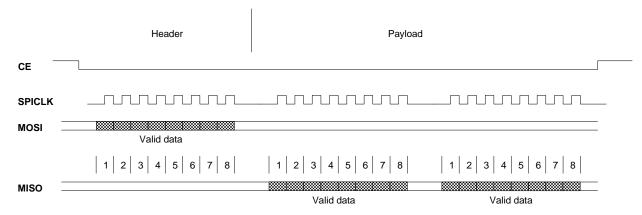

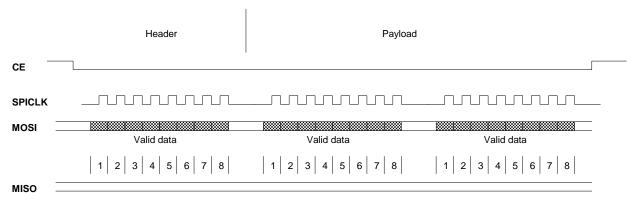

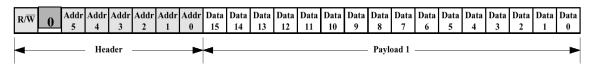

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### E-mail:

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

**Europe, Middle East, and Africa:** Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate

Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-521-6274 or 303-675-2140 Fax: 303-675-2150 LDCF or Free scale Semiconductor@hibbert group.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2005, 2006, 2007, 2008. All rights reserved.

# **Contents**

| ADOL                                                                                                  | IT THIS BOOK                                                                                                                                                                                                                                                                                                                                    |                                                             |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Chau                                                                                                  | Audience. Organization Revision History. Conventions Definitions, Acronyms, and Abbreviations References.                                                                                                                                                                                                                                       | . ix<br>x<br>x                                              |

| Chap<br>Intro                                                                                         | duction                                                                                                                                                                                                                                                                                                                                         |                                                             |

| 1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.2.3<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7                              | Features Software Support Simple MAC (SMAC) IEEE 802.15.4-Compliant MAC ZigBee-Compliant Network Stack (BeeStack) Block Diagrams Data Transfer Modes Packet Structure Receive Path Description Transmit Path Description                                                                                                                        | 1-2<br>1-3<br>1-3<br>1-3<br>1-4<br>1-4<br>1-5               |

| Chap<br>MC13                                                                                          | oter 2<br>3202 Pins and Connections                                                                                                                                                                                                                                                                                                             |                                                             |

| 2.1<br>2.2                                                                                            | Device Pin Assignment                                                                                                                                                                                                                                                                                                                           |                                                             |

| Chap<br>Syste                                                                                         | oter 3<br>em Considerations                                                                                                                                                                                                                                                                                                                     |                                                             |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.6<br>3.6.1<br>3.6.2<br>3.6.3 | Introduction. Power Connections Test Pin SM Reset Usage.  MC13202 Interface to MCU.  SPI Command Channel.  Interrupt Request to MCU  Modem Control Signals  Modem Status Signals  System Oscillator and Clock Considerations  Modem Crystal Oscillator.  System Clock Configurations  Single System Crystal with CLKO driving MCU crystal input | 3-1<br>3-2<br>3-3<br>3-3<br>3-4<br>3-4<br>3-4<br>3-4<br>3-5 |

| 3.7                                                                                                   | GPIO Characteristics                                                                                                                                                                                                                                                                                                                            |                                                             |

| 3.8    | MC13202 Digital Signal Properties Summary                         | 3-7  |

|--------|-------------------------------------------------------------------|------|

| 3.9    | Transceiver RF Configurations and External Connections            | 3-8  |

| 3.9.1  | RF Interface Pins                                                 | 3-8  |

| 3.9.2  | Controlling RF Modes of Operation                                 | 3-11 |

| 3.9.3  | RF Control Output CT_Bias                                         | 3-12 |

| 3.10   | Low Power Considerations                                          |      |

| 3.10.1 | Modem Low Power States                                            | 3-13 |

| 3.10.2 | Special Consideration Where Doze Current Is Higher Than Specified | 3-14 |

| 3.10.3 | Recovery Times from Low Power Modes                               |      |

| 3.10.4 | General System Considerations for Low Power                       |      |

| Chap   |                                                                   |      |

| Mode   | em SPI Register Descriptions                                      |      |

| 4.1    | Overview                                                          |      |

| 4.2    | Register Model and Description Details                            |      |

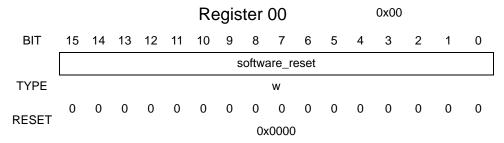

| 4.3    | Reset - Register 00                                               |      |

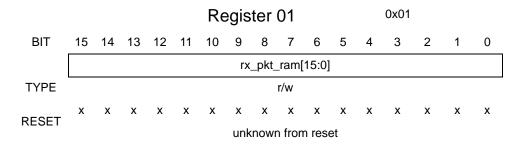

| 4.4    | RX_Pkt_RAM - Register 01                                          |      |

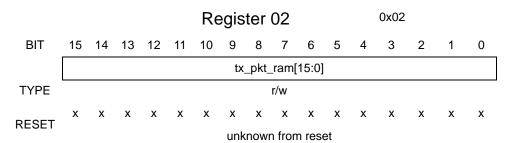

| 4.5    | TX_Pkt_RAM - Register 02                                          | 4-5  |

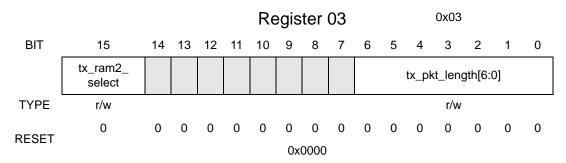

| 4.6    | TX_Pkt_Ctl - Register 03                                          | 4-6  |

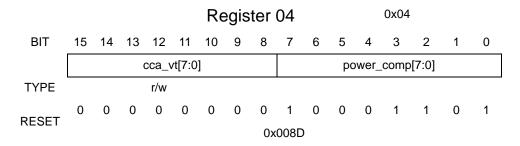

| 4.7    | CCA_Thresh - Register 04                                          |      |

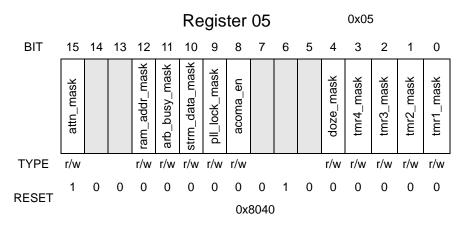

| 4.8    | IRQ_Mask - Register 05                                            | 4-7  |

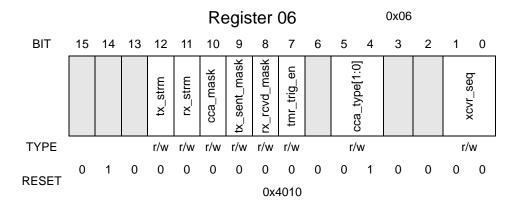

| 4.9    | Control_A - Register 06                                           | 4-9  |

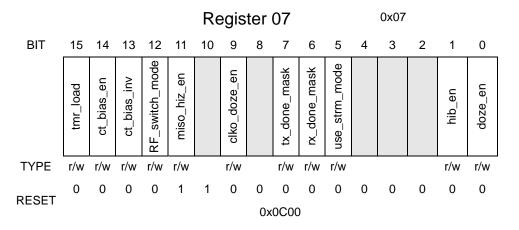

| 4.10   | Control_B - Register 07                                           |      |

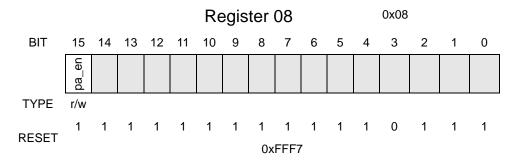

| 4.11   | PA_Enable - Register 08                                           |      |

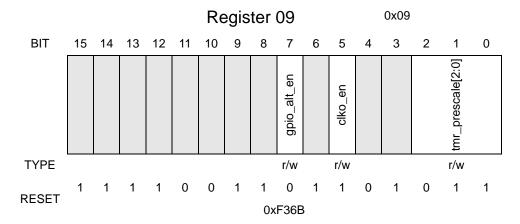

| 4.12   | Control_C - Register 09                                           | 4-12 |

| 4.13   | CLKO_Ctl - Register 0A                                            |      |

| 4.14   | GPIO_Dir - Register 0B                                            | 4-14 |

| 4.15   | GPIO_Data_Out - Register 0C                                       | 4-16 |

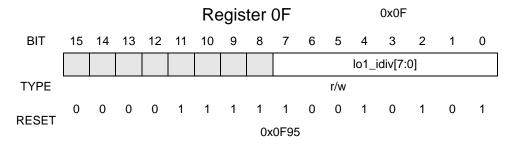

| 4.16   | LO1_Int_Div - Register 0F                                         |      |

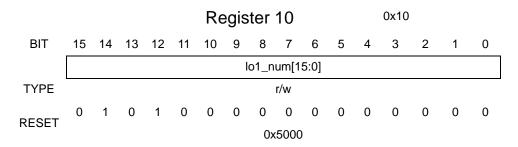

| 4.17   | LO1_Num - Register 10                                             |      |

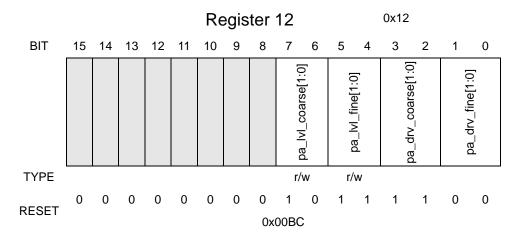

| 4.18   | PA_Lvl - Register 12                                              | 4-18 |

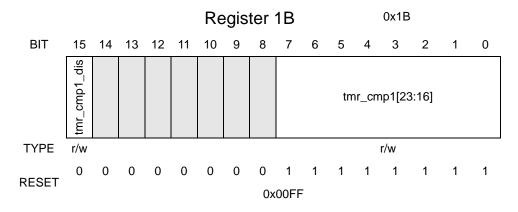

| 4.19   | Tmr_Cmp1_A - Register 1B.                                         | 4-19 |

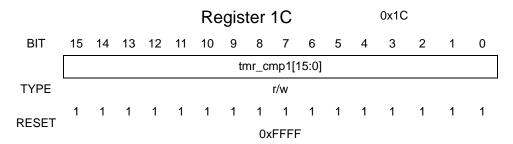

| 4.20   | Tmr_Cmp1_B - Register 1C                                          |      |

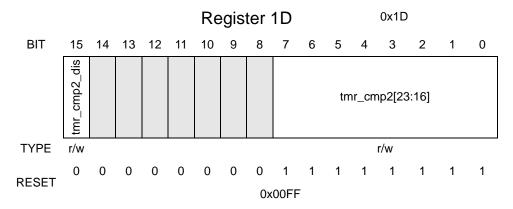

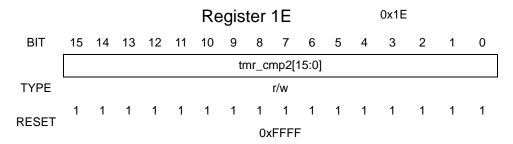

| 4.21   | Tmr_Cmp2_A - Register 1D                                          |      |

| 4.22   | Tmr_Cmp2_B - Register 1E                                          |      |

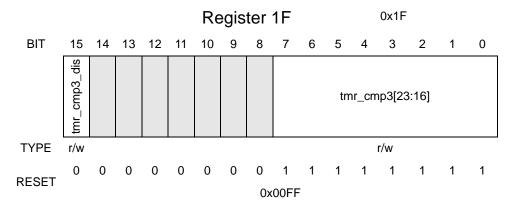

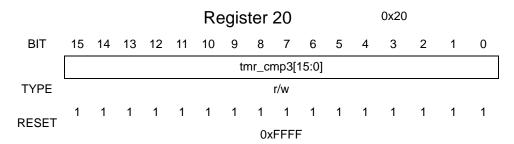

| 4.23   | Tmr_Cmp3_A - Register 1F                                          |      |

| 4.24   | Tmr_Cmp3_B - Register 20                                          | 4-23 |

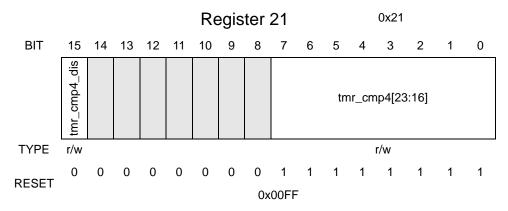

| 4.25   | Tmr_Cmp4_A -Register 21                                           | 4-24 |

| 4.26   | Tmr_Cmp4_B - Register 22                                          |      |

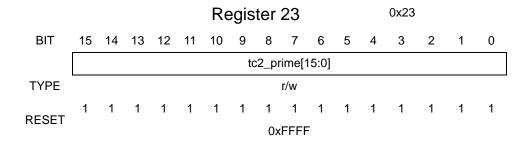

| 4.27   | TC2_Prime - Register 23                                           | 4-25 |

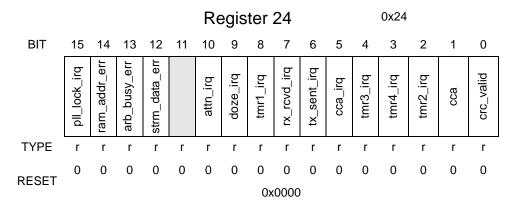

| 4.28   | IRQ_Status - Register 24                                          | 4-26 |

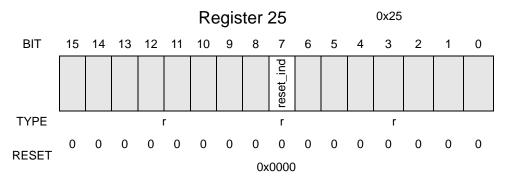

| 4.29   | RST_Ind - Register 25                                             | 4-28 |

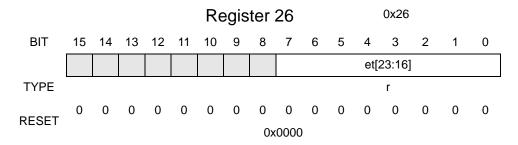

| 4.30   | Current_Time_A - Register 26                                      |      |

| 4.31   | Current_Time_B - Register 27                                      | 4-29 |

|        |                                                                   |      |

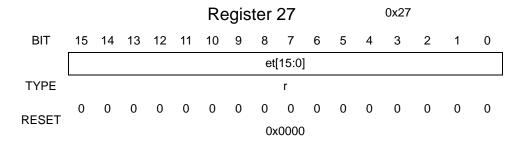

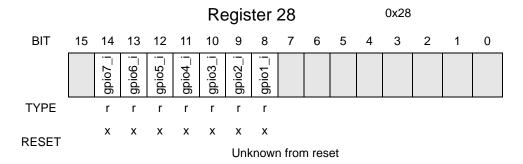

| 4.32  | GPIO_Data_In - Register 28                                               | 4-30 |

|-------|--------------------------------------------------------------------------|------|

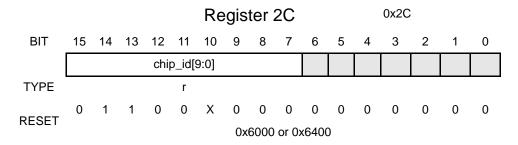

| 4.33  | Chip_ID - Register 2C                                                    | 4-31 |

| 4.34  | RX_Status - Register 2D                                                  | 4-31 |

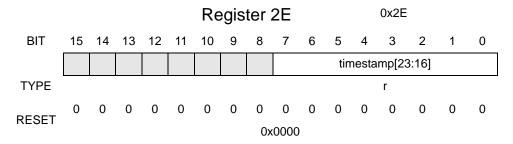

| 4.35  | Timestamp_A - Register 2E                                                |      |

| 4.36  | Timestamp_B - Register 2F                                                | 4-33 |

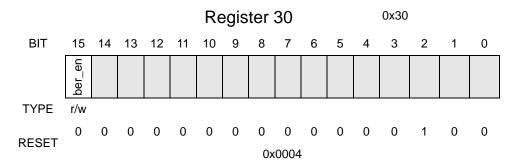

| 4.37  | BER_Enable - Register 30                                                 | 4-33 |

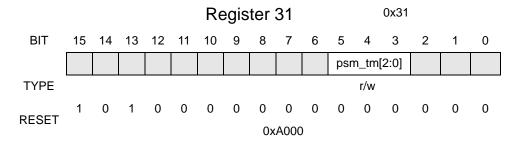

| 4.38  | PSM_Mode - Register 31                                                   |      |

|       | oter 5<br>al Peripheral Interface (SPI)                                  |      |

|       | • • •                                                                    |      |

| 5.1   | Overview                                                                 |      |

| 5.2   | SPI Basic Operation                                                      |      |

| 5.2.1 | SPI Pin Definition                                                       |      |

| 5.2.2 | SPI Burst Operation                                                      |      |

| 5.3   | SPI Singular Transactions                                                |      |

| 5.3.1 | SPI Singular Transaction Signalling                                      |      |

| 5.3.2 | SPI Singular Transaction Protocol                                        |      |

| 5.4   | Symbol / Data Format                                                     |      |

| 5.5   | SPI Recursive Transactions                                               |      |

| 5.5.1 | Recursive SPI Register Read                                              |      |

| 5.5.2 | Recursive SPI Register Write                                             |      |

| 5.5.3 | Special Case - Packet RAM Access                                         |      |

| 5.6   | Program Reset (Writing Address 0x00)                                     | 5-10 |

|       | oter 6                                                                   |      |

| Mode  | es of Operation                                                          |      |

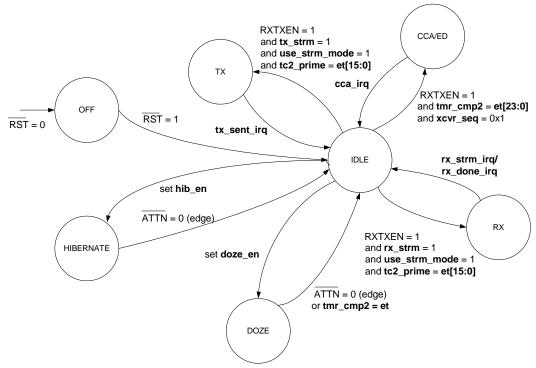

| 6.1   | Operational Modes Summary                                                |      |

| 6.2   | Low Power Modes                                                          |      |

| 6.2.1 | Off Mode                                                                 |      |

| 6.2.2 | Hibernate Mode                                                           | 6-4  |

| 6.2.3 | Doze Mode                                                                |      |

| 6.3   | Active Modes                                                             |      |

| 6.3.1 | Idle Mode                                                                |      |

| 6.3.2 | Controlling Transition to Other Active Modes from Idle                   |      |

| 6.3.3 | Packet Mode Data Transfer TX and RX Operation                            |      |

| 6.3.4 | Stream Mode Data Transfer TX and RX Operation                            |      |

| 6.3.5 | Clear Channel Assessment (CCA) Modes (including Link Quality Indication) |      |

| 6.4   | Frequency of Operation                                                   |      |

| 6.5   | Transmit Power Adjustment                                                |      |

| 6.6   | 2.4GHz PLL Out-of-Lock Interrupt                                         | 6-20 |

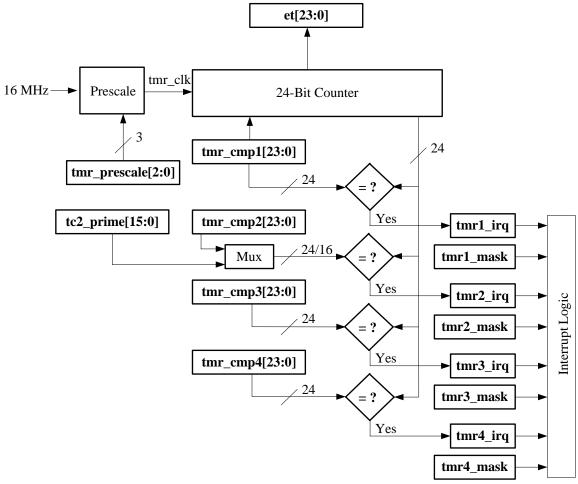

# Chapter 7 Timer Information

| 7.1   | Event Timer Block                                | 7-1 |

|-------|--------------------------------------------------|-----|

| 7.2   | Event Timer Time Base                            | 7-2 |

| 7.3   | Setting Current Time                             | 7-2 |

| 7.4   | Reading Current Time                             | 7-3 |

| 7.5   | Latching the Timestamp                           |     |

| 7.6   | Event Timer Comparators                          |     |

| 7.6.1 | Timer Compare Fields                             | 7-4 |

| 7.6.2 | Timer Disable Bits                               | 7-4 |

| 7.6.3 | Timer Status Flags                               | 7-4 |

| 7.6.4 | Timer Interrupt Masks                            | 7-5 |

| 7.6.5 | Setting Compare Values                           | 7-5 |

| 7.7   | Intended Event Timer Usage                       | 7-5 |

| 7.7.1 | Generating Time-Based Interrupts                 | 7-6 |

| 7.7.2 | Using tmr_cmp2[23:0] to Exit Doze Mode           | 7-6 |

| 7.7.3 | Timer-Triggered Transceiver Events               |     |

| Char  | oter 8                                           |     |

|       | rupt Description                                 |     |

| 8.1   | Interrupts                                       | 8-1 |

| 8.1.1 | Interrupt Sources                                |     |

| 8.1.2 | Output Pin IRQ                                   | 8-3 |

| 8.2   | PLL_lock_irq Status Bit and Operation            |     |

| 8.3   | Attn_irq Status Bit and Interrupt Operation      |     |

| 8.4   | Interrupts from Exiting Low Power Modes          |     |

| 8.4.1 | Exiting Off Mode (Reset)                         |     |

| 8.4.2 | Exiting Hibernate Mode                           |     |

| 8.4.3 | Exiting Doze Mode(s)                             |     |

| Chap  | oter 9                                           |     |

| Misc  | ellaneous Functions                              |     |

| 9.1   | Reset Function                                   | 9-1 |

| 9.1.1 | Input Pin RST                                    | 9-1 |

| 9.1.2 | Software Reset (Writing to Register 00)          | 9-1 |

| 9.1.3 | Reset Indicator Bit (RST_Ind Register 25, Bit 7) | 9-1 |

| 9.2   | General Purpose Input/Output                     | 9-2 |

| 9.2.1 | Configuring GPIO Direction                       |     |

| 9.2.2 | Setting GPIO Output Drive Strength               |     |

| 9.2.3 | Programming GPIO Output Value                    |     |

| 9.2.4 | Reading GPIO Input State                         |     |

| 9.2.5 | GPIO1 and GPIO2 Status Indicators                |     |

| 9.3   | Crystal Oscillator                               | 9-3 |

|       |                                                  |     |

| 9.3.1 | Crystal Requirements                                                      | 9-4 |

|-------|---------------------------------------------------------------------------|-----|

| 9.3.2 | Crystal Trim Operation                                                    | 9-4 |

| 9.4   | Output Clock Pin CLKO                                                     | 9-5 |

| 9.4.1 | Enable CLKO (clko_en, Control_C Register 09, Bit 5)                       | 9-5 |

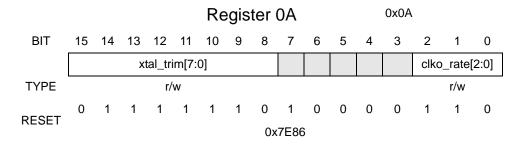

| 9.4.2 | Setting CLKO frequency (clko_rate[2:0], CLKO_Ctl Register 0A, Bits 2-0)   | 9-5 |

| 9.4.3 | Enable CLKO During Doze Mode (clko_doze_en, Control_B Register 07, Bit 9) | 9-6 |

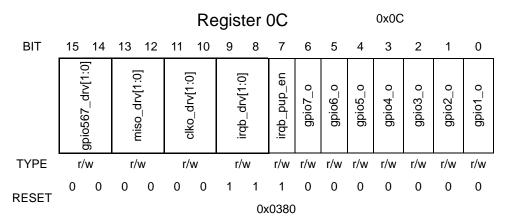

| 9.4.4 | Setting CLKO Output Drive Strength (clko_drv[1:0],                        |     |

|       | GPIO_Data_Out Register 0C, Bits 11-10)                                    | 9-6 |

| 9.5   | Input Pin ATTN                                                            | 9-6 |

viii Freescale Semiconductor

### **About This Book**

This manual describes the Freescale MC13202. The MC13202 is a 2.4 GHz ISM band transceivers built for the IEEE<sup>®</sup> 802.15.4 Standard. The MC13202 transceiver can function as a standalone transceiver or when combined with a software package and an HCS08 MCU, they form the Freescale 802.15.4 Standard platform solution.

### **Audience**

This manual is intended for system designers.

# Organization

This document is organized into nine (9) chapters.

| Chapter 1 | <b>Introduction</b> — The MC13202 is Freescale's second-generation ZigBee <sup>™</sup> transceiver. This transceiver is a low power, 2.4 GHz radio frequency transceiver that can be coupled with an 8-bit microcontroller. |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Chapter 2 | Pins and Connections — Describes device pinout and functionality.                                                                                                                                                           |  |  |  |

| Chapter 3 | <b>System Considerations</b> — Describes system level considerations of the MC13202 modem.                                                                                                                                  |  |  |  |

| Chapter 4 | <b>Modem Register Descriptions</b> — Details how all control, reading of status, writing of data, and reading of data is done through the MC13202 SPI port.                                                                 |  |  |  |

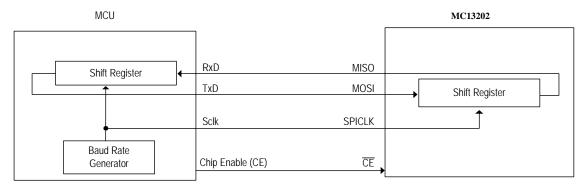

| Chapter 5 | MC13202 Serial Peripheral Interface (SPI) — Shows how the MC13202 modem and CPU communicate primarily through the onboard SPI command channel.                                                                              |  |  |  |

| Chapter 6 | <b>Modem Modes of Operation</b> — Describes the numerous MC13202 passive operational modes that allow for low-current operation as well as modes where the transceiver is active.                                           |  |  |  |

| Chapter 7 | <b>Modem Timer Information</b> — Describes how the MC13202 uses its internal Event Timer block to manage system timing.                                                                                                     |  |  |  |

| Chapter 8 | <b>Modem Interrupt Description</b> — Shows how interrupts provide a way for the MC13202 to inform the host microcontroller (MCU) of onboard events without requiring the MCU to constantly query MC13202 status.            |  |  |  |

| Chapter 9 | <b>Modem Miscellaneous Functions</b> — Describes how the MC13202 can be placed in one of two reset conditions either through hardware input M_RSTB or by writing to Reset Register 00.                                      |  |  |  |

# **Revision History**

The following table summarizes revisions to this document since the previous release (Rev 1.0).

#### **Revision History**

| Location        | Revision                                                                                                                   |

|-----------------|----------------------------------------------------------------------------------------------------------------------------|

| Entire document | Updated various specification numbers, fixed numerous stale cross references and updated for most recent software updates. |

#### Conventions

This document uses the following notational conventions:

- Courier monospaced type indicate commands, command parameters, code examples, expressions, datatypes, and directives.

- Italic type indicates replaceable command parameters.

- All source code examples are in C.

# Definitions, Acronyms, and Abbreviations

The following list defines the acronyms and abbreviations used in this document.

ACK Acknowledgement Frame

API Application Programming Interface

BB Baseband

CCA Clear Channel Assessment

CRC Cyclical Redundancy Check

DCD Differential Chip Decoding

DME Device Management Entity

FCS Frame Check Sequence

FFD Full Function Device

FFD-C Full Function Device Coordinator

FLI Frame Length Indicator

GTS Guaranteed Time Slot

HW Hardware

IRQ Interrupt Request

ISR Interrupt Service Routine

LO Local Oscillator

MAC Medium Access Control

MCPS MAC Common Part Sublayer

MCU Microcontroller Unit

MLME MAC Sublayer Management Entity

MSDU MAC Service Data Unit

NWK Network

PA Power Amplifier

PAN Personal Area Network

PANID PAN Identification

PHY PHYsical Layer

PIB PAN Information Base

PPDU PHY Protocol Data Unit

PSDU PHY Service Data Unit

RF Radio Frequency

RFD Reduced Function Device

SAP Service Access Point

SFD Start of Frame Delimiter

SPI Serial Peripheral Interface

SSCS Service Specific Convergence Layer

SW Software

VCO Voltage Controlled Oscillator

#### References

The following sources were referenced to produce this book:

- [1] IEEE<sup>®</sup> 802.15.4 Standard

- [2] Freescale MC13202 Data Sheet

# Chapter 1 Introduction

The MC13202 is a short range, low power, 2.4 GHz Industrial, Scientific, and Medical (ISM) band transceiver. The MC13202 contains a complete 802.15.4 physical layer (PHY) modem designed for the 802.15.4 wireless standard which supports peer-to-peer, star, and mesh networking.

The MC13202 includes the 802.15.4 PHY/MAC for use with the HCS08 Family of MCUs.

When combined with an appropriate microcontroller (MCU), the MC13202 provide a cost-effective solution for short-range data links and networks. Interface with the MCU is accomplished using a four wire Serial Peripheral Interface (SPI) connection and an interrupt request output which allows for the use of a variety of processors. The software and processor can be scaled to fit applications ranging from simple point-to-point systems, through complete ZigBee<sup>TM</sup> networking.

Applications include, but are not limited to, the following:

- Residential and commercial automation

- Lighting control

- Security

- Access control

- Heating, ventilation, air-conditioning (HVAC)

- Automated meter reading

- Industrial Control

- Asset tracking and monitoring

- Homeland security

- Process management

- Environmental monitoring and control

- HVAC

- Automated meter reading (AMR)

- Health Care

- Patient monitoring

- Fitness monitoring

The transceiver includes a low noise amplifier, 1mW nominal output power, PA with internal voltage controlled oscillator (VCO), integrated transmit/receive switch, on-board power supply regulation, and full spread-spectrum encoding and decoding. The device supports 250 kbps Offset-Quadrature Phase Shift Keying (O-QPSK) data in 2.0 MHz channels with 5.0 MHz channel spacing per the 802.15.4 Standard. The SPI port and interrupt request output are used for receive (RX) and transmit (TX) data transfer and control.

#### 1.1 Features

- Power supply range: 2.0 to 3.4 V

- Operates on one of 16 selectable channels in the 2.4 GHz ISM band

- -1 to 0 dBm nominal output power, programmable from -27 dBm to +3 dBm typical

- Buffered transmit and receive data packets for simplified use with low cost MCUs

- Supports both Packet Mode and Streaming Mode

- Supports 250 kbps O-QPSK data in 5.0 MHz channels and full spread-spectrum encode and decode (compatible with 802.15.4 Standard)

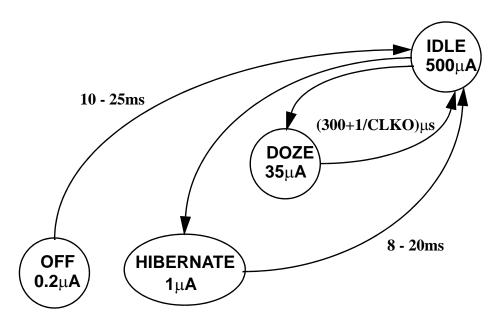

- Three power down modes for power conservation:

- $--<1 \,\mu A$  Off current

- 1.0 μA Typical Hibernate current

- 35 µA Typical Doze current

- Receive sensitivity of <-92 dBm (typical) at 1% PER, 20-byte packet, much better than the IEEE 802.15.4 Standard of -85 dBm

- Integrated transmit/receive switch

- Dual PA output pairs which can be programmed for full differential single port or dual port operation that supports an external LNA and/or PA

- Four internal timer comparators available to reduce MCU resource requirements

- Programmable frequency clock output for use by MCU

- Onboard trim capability for 16 MHz crystal reference oscillator eliminates the need for external variable capacitors and allows for automated production frequency calibration.

- Seven general purpose input/output (GPIO) signals

- Operating temperature range: -40°C to 85°C

- Small form factor QFN-32 Package

- RoHS compliant

- Meets moisture sensitivity level (MSL) 3

- 260°C peak reflow temperature

- Meets lead-free requirements

# 1.2 Software Support

Freescale provides a wide range of software functionality to complement the MC13202 hardware. There are three levels of application solutions:

- Simple proprietary wireless connectivity

- User networks built on the 802.15.4 MAC standard

- ZigBee-compliant network stack (BeeStack)

1-2 Freescale Semiconductor

# 1.2.1 Simple MAC (SMAC)

- Small memory footprint (about 3 kbytes typical))

- Supports point-to-point and star network configurations

- Proprietary networks

- Source code and application examples provided

# 1.2.2 IEEE 802.15.4-Compliant MAC

- Supports star, mesh and cluster tree topologies

- Supports beaconed networks

- Supports GTS for low latency

- Multiple power saving modes (idle, doze, hibernate)

# 1.2.3 ZigBee-Compliant Network Stack (BeeStack)

- Supports ZigBee 1.0 specification

- Supports star, mesh and tree networks

- Advanced Encryption Standard (AES) 128-bit security

# 1.3 Block Diagrams

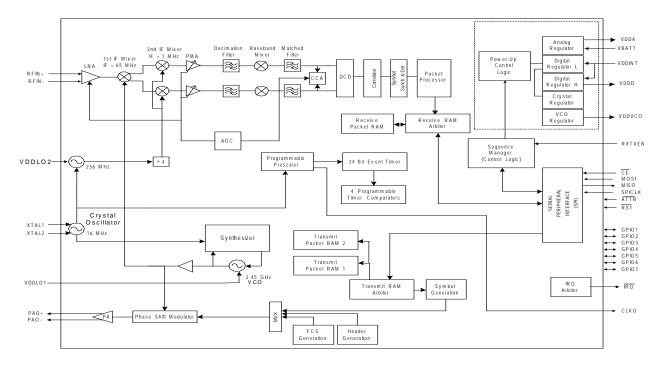

Figure 1-1 shows a simplified block diagram of the MC13202 which is an 802.15.4 Standard compatible transceiver that provides the functions required in the physical layer (PHY) specification.

Figure 1-1. MC13202 Simplified Block Diagram

MC13202 Reference Manual, Rev. 1.1

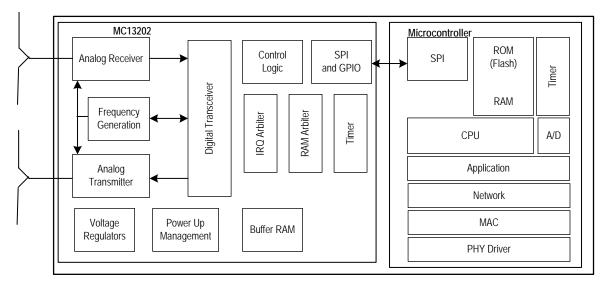

Figure 1-2 shows the basic system block diagram for the MC13202 in an application. Interface with the transceiver is accomplished through a 4-wire SPI port and interrupt request line. The media access control (MAC), drivers, and network and application software (as required) reside on the host processor. The host can vary from a simple 8-bit device up to a sophisticated 32-bit processor depending on application requirements.

Figure 1-2. System Level Block Diagram

#### 1.4 Data Transfer Modes

The MC13202 has two data transfer modes:

- 1. Packet Mode Data is buffered in on-chip RAM

- 2. Streaming Mode Data is processed word-by-word

The Freescale 802.15.4 MAC software only supports the streaming mode of data transfer. For proprietary applications, Packet Mode can be used to conserve MCU resources.

#### 1.5 Packet Structure

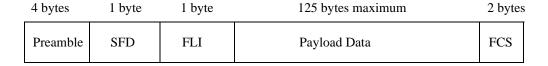

Figure 1-3 shows the packet structure of the MC13202. Payloads of up to 125 bytes are supported. The MC13202 adds a four-byte preamble, a one-byte Start of Frame Delimiter (SFD), and a one-byte Frame Length Indicator (FLI) before the data. A Frame Check Sequence (FCS) is calculated and appended to the end of the data.

Figure 1-3. MC13202 Packet Structure

1-4 Freescale Semiconductor

# 1.6 Receive Path Description

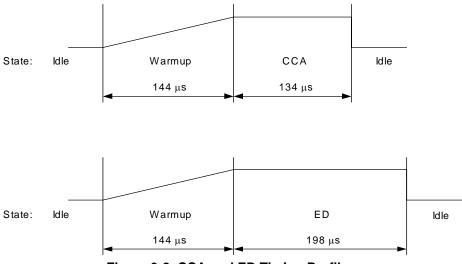

In the receive signal path, the RF input is converted to low IF In-phase and Quadrature (I & Q) signals through two down-conversion stages. A Clear Channel Assessment (CCA) can be performed based upon the baseband energy integrated over a specific time interval. The digital back end performs Differential Chip Detection (DCD), the correlator "de-spreads" the Direct Sequence Spread Spectrum (DSSS) Offset QPSK (O-QPSK) signal, determines the symbols and packets, and detects the data.

The preamble, SFD, and FLI are parsed and used to detect the payload data and FCS which are stored in RAM. A two-byte FCS is calculated on the received data and compared to the FCS value appended to the transmitted data, generating a Cyclical Redundancy Check (CRC) result. Link Quality is measured over a 64 µs period after the packet preamble and stored in RAM.

If the MC13202 is in Packet Mode, the data is processed as an entire packet. The MCU is notified that an entire packet has been received via an interrupt.

If the MC13202 is in streaming mode, the MCU is notified by an interrupt on a word-by-word basis.

# 1.7 Transmit Path Description

For the transmit path, the TX data that was previously stored in RAM are retrieved (Packet Mode) or the TX data is clocked in via the SPI (Stream Mode), formed into packets per the 802.15.4 PHY, spread, and then up converted to the transmit frequency.

If the MC13202 is in Packet Mode, data is processed as an entire packet. The data is first loaded into the TX buffer. The MCU then requests that the MC13202 transmit the data. The MCU is notified via an interrupt when the whole packet has successfully been transmitted.

In streaming mode, the data is fed to the MC13202 on a word-by-word basis with an interrupt serving as a notification that the MC13202 is ready for more data. This continues until the whole packet is transmitted.

Introduction

1-6 Freescale Semiconductor

# **Chapter 2 MC13202 Pins and Connections**

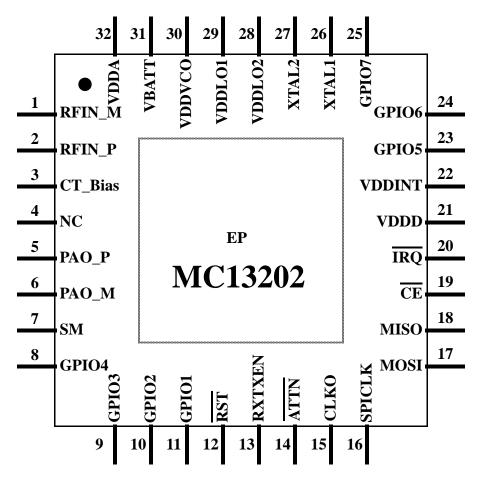

# 2.1 Device Pin Assignment

Figure 2-1. MC13202 Pinout

# 2.2 Pin Definitions

**Table 2-1. Pin Function Description**

| Pin # | Pin<br>Name | Туре                  | Description                                                                                                                                                                                                                                                                                      | Functionality                                                                                                                                                                                 |

|-------|-------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | RFIN_M      | RF Input              | RF input/output negative.                                                                                                                                                                                                                                                                        | When used with internal T/R switch, this is a bi-directional RF port for the internal LNA and PA                                                                                              |

| 2     | RFIN_P      | RF Input              | RF input/output positive.                                                                                                                                                                                                                                                                        | When used with internal T/R switch, this is a bi-directional RF port for the internal LNA and PA                                                                                              |

| 3     | CT_Bias     | Control voltage       | Bias voltage/control signal for external RF components                                                                                                                                                                                                                                           | When used with internal T/R switch, provides RX ground reference and TX VDDA reference for use with external balun. Can also be used as a control signal for external LNA, PA, or T/R switch. |

| 4     | NC          |                       | Tie to Ground.                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                               |

| 5     | PAO_P       | RF Output /DC Input   | RF Power Amplifier Output<br>Positive.                                                                                                                                                                                                                                                           | Open drain. Connect to VDDA through a bias network when used with an external balun. Not used when internal T/R switch is used.                                                               |

| 6     | PAO_M       | RF Output/DC Input    | RF Power Amplifier Output<br>Negative.                                                                                                                                                                                                                                                           | Open drain. Connect to VDDA through a bias network when used with an external balun. Not used when internal T/R switch is used.                                                               |

| 7     | SM          | Input                 | Test mode pin.                                                                                                                                                                                                                                                                                   | Must be grounded for normal operation.                                                                                                                                                        |

| 8     | GPIO4       | Digital Input/ Output | General Purpose Input/Output 4.                                                                                                                                                                                                                                                                  |                                                                                                                                                                                               |

| 9     | GPIO3       | Digital Input/ Output | General Purpose Input/Output 3.                                                                                                                                                                                                                                                                  |                                                                                                                                                                                               |

| 10    | GPIO2       | Digital Input/ Output | General Purpose Input/Output 2.<br>When gpio_alt_en, Register 9, Bit<br>7 = 1, GPIO2 functions as a "CRC<br>Valid" indicator.                                                                                                                                                                    |                                                                                                                                                                                               |

| 11    | GPIO1       | Digital Input/ Output | General Purpose Input/Output 1.<br>When gpio_alt_en, Register 9, Bit<br>7 = 1, GPIO1 functions as an "Out<br>of Idle" indicator.                                                                                                                                                                 |                                                                                                                                                                                               |

| 12    | RST         | Digital Input         | Active Low Reset. While held low, the IC is in Off Mode and all internal information is lost from RAM and SPI registers. When high, IC goes to IDLE Mode, with SPI in default state.                                                                                                             |                                                                                                                                                                                               |

| 13    | RXTXEN      | Digital Input         | Active High. Low to high transition initiates RX or TX sequence depending on SPI setting. Should be taken high after SPI programming to start RX or TX sequence and should be held high through the sequence. After sequence is complete, return RXTXEN to low. When held low, forces Idle Mode. |                                                                                                                                                                                               |

2-2 Freescale Semiconductor

**Table 2-1. Pin Function Description (continued)**

| Pin# | Pin<br>Name | Туре                 | Description Functionality                                                                                                                                     |                                                                                                                                                                               |

|------|-------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14   | ATTN        | Digital Input        | Active Low Attention. Transitions IC from either Hibernate or Doze Modes to Idle.                                                                             |                                                                                                                                                                               |

| 15   | CLKO        | Digital Output       | Clock output to host MCU. Programmable frequencies of: 16 MHz, 8 MHz, 4 MHz, 2 MHz, 1 MHz, 62.5 kHz, 32.786+ kHz (default), and 16.393+ kHz.                  |                                                                                                                                                                               |

| 16   | SPICLK      | Digital Clock Input  | External clock input for the SPI interface.                                                                                                                   |                                                                                                                                                                               |

| 17   | MOSI        | Digital Input        | Master Out/Slave In. Dedicated SPI data input.                                                                                                                |                                                                                                                                                                               |

| 18   | MISO        | Digital Output       | Master In/Slave Out. Dedicated SPI data output.                                                                                                               |                                                                                                                                                                               |

| 19   | CE          | Digital Input        | Active Low Chip Enable. Enables SPI transfers.                                                                                                                |                                                                                                                                                                               |

| 20   | IRQ         | Digital Output       | Active Low Interrupt Request.                                                                                                                                 | Open drain device. Programmable 40 k $\Omega$ internal pull-up. Interrupt can be serviced every 6 $\mu$ s with <20 pF load. Optional external pull-up must be >4 k $\Omega$ . |

| 21   | VDDD        | Power Output         | Digital regulated supply bypass.                                                                                                                              | Decouple to ground.                                                                                                                                                           |

| 22   | VDDINT      | Power Input          | Digital interface supply & digital regulator input. Connect to Battery.                                                                                       | 2.0 to 3.4 V. Decouple to ground.                                                                                                                                             |

| 23   | GPIO5       | Digital Input/Output | General Purpose Input/Output 5.                                                                                                                               |                                                                                                                                                                               |

| 24   | GPIO6       | Digital Input/Output | General Purpose Input/Output 6.                                                                                                                               |                                                                                                                                                                               |

| 25   | GPIO7       | Digital Input/Output | General Purpose Input/Output 7.                                                                                                                               |                                                                                                                                                                               |

| 26   | XTAL1       | Input                | Crystal Reference oscillator input.                                                                                                                           | Connect to 16 MHz crystal and load capacitor.                                                                                                                                 |

| 27   | XTAL2       | Input/Output         | Crystal Reference oscillator output  Note: Do not load this pin by using it as a 16 MHz source. Measure 16 MHz output at Pin 15, CLKO, programmed for 16 MHz. |                                                                                                                                                                               |

| 28   | VDDLO2      | Power Input          | LO2 VDD supply. Connect to VDDA externally.                                                                                                                   |                                                                                                                                                                               |

| 29   | VDDLO1      | Power Input          | LO1 VDD supply. Connect to VDDA externally.                                                                                                                   |                                                                                                                                                                               |

| 30   | VDDVCO      | Power Output         | VCO regulated supply bypass.                                                                                                                                  | Decouple to ground.                                                                                                                                                           |

#### MC13202 Pins and Connections

**Table 2-1. Pin Function Description (continued)**

| Pin # | Pin<br>Name | Туре         | Description                                                                                                                                                                              | Functionality       |

|-------|-------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 31    | VBATT       | Power Input  | Analog voltage regulators Input.<br>Connect to Battery.                                                                                                                                  | Decouple to ground. |

| 32    | VDDA        | Power Output | Analog regulated supply Output. Connect to directly VDDLO1 and VDDLO2 externally and to PAO± through a bias network. Note: Do not use this pin to supply circuitry external to the chip. | Decouple to ground. |

| EP    | Ground      |              | External paddle / flag ground.                                                                                                                                                           | Connect to ground.  |

# **Chapter 3 System Considerations**

#### 3.1 Introduction

The MC13202 is the embodiment of an IEEE 802.15.4 transceiver in a single QFN package which can provide solutions to proprietary nets, IEEE 802.15.4 MAC-compatible nets, or full ZigBee-compatible nets. All control to the modem is through the common SPI bus, the MCU interrupt request, and several MCU GPIO lines. Primary interface with the modem is through the SPI command structure that allows reading/writing modem registers and provides initialization of parameters, reading of status, and control of modem operation. The modem can ask for real time response through the interrupt request signal.

This chapter presents information regarding operation of the modem from a system level. The areas considered here are also covered in greater detail in the following sections of the book. The book is organized such that the first three chapters present the top-level view of the MC13202 device and the following chapters present individual functions with detailed descriptions.

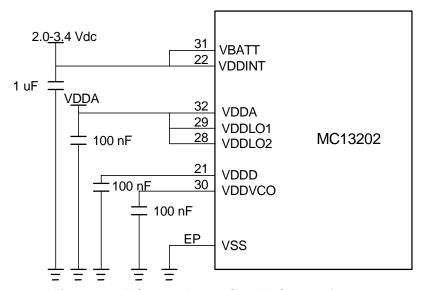

#### 3.2 Power Connections

The MC1321x power connections are listed in Table 3-1.

**Table 3-1. Power Pin Descriptions**

| Pin# | Pin Name | Туре         | Description                                                             | Functionality                                                         |

|------|----------|--------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 22   | VDDINT   | Power Input  | Digital interface supply & digital regulator input. Connect to Battery. | 2.0 to 3.4 V. Decouple to ground.                                     |

| 21   | VDDD     | Power Output | Regulated output supply voltage                                         | Decouple to ground.                                                   |

| 31   | VBATT    | Power Input  | Voltage regulators' input. Connect to Battery                           | Decouple to ground.                                                   |

| 32   | VDDA     | Power Output | Analog regulated supply output                                          | Decouple to ground. Connect to directly VDDLO1 and VDDLO2 externally. |

| 30   | VDDVCO   | Power Output | Modem VCO regulated supply bypass                                       | Decouple to ground.                                                   |

| 29   | VDDLO1   | Power Input  | Modem LO1 VDD supply Connect to VDDA ext                                |                                                                       |

| 28   | VDDLO2   | Power Input  | Modem LO2 VDD supply Connect to VDDA exte                               |                                                                       |

| EP   | VSS      | Power input  | External package flag. Common VSS                                       | Connect to ground.                                                    |

#### **System Considerations**

When designing power to the device, the following points need to be considered:

- The QFN package has a single common EP ground flag (VSS)

- There are two primary power inputs which include VBATT for modem power and VDDINT for digital interface power

- For logic level compatibility between the modem and the system CPU, VBATT, and VDDINT must be connected with the CPU to a common source supply of 2.0 3.4 VDC

- Input VBATT feeds the common supply to the analog and digital circuitry regulators. The analog regulator output VDDA is provided both for bypassing and to supply VDDLO1 and VDDLO2 which are the power rails for the local oscillators

- Output VDDVCO is provided to allow separate bypass of the modem radio VCO regulated supply

Power supply connections are shown in Figure 3-1.

Figure 3-1. MC13202 Power Supply Connections

#### NOTE

There are separate bypass capacitors on VDDA, VDDD, and VDDVCO. In some RF circuitry configurations, VDDA may also need to be DC-coupled to the radio PA outputs.

#### 3.3 Test Pin SM

Input SM is a test pin that must be grounded for normal operation.

MC13202 Reference Manual, Rev. 1.1

# 3.4 Reset Usage

The modem active low reset input  $\overline{RST}$  is recommended to be driven from an MCU GPIO pin. In the interest of lowest power, there is no external pull-up resistor on input  $\overline{RST}$ . An MCU GPIO programmed as an output typically also has a software controlled pull-up resistor. However, it would normally not be used because the modem can be held in hardware reset by the MCU for extended periods of time. The transceiver  $\overline{IRQ}$  pullup can also be disabled, and having no resistor makes for lowest power applications.

From a power-on or "cold start" condition, the MCU GPIO normally initiates as a high-impedance input with its internal pull-up disabled and the  $\overline{IRQ}$  pullup is enabled which holds the modem reset input high. As part of the MCU initialization, GPIO must be programmed as an output and then driven low to reset the modem. The  $\overline{RST}$  input is asynchronous and needs to be held low for only a short period.

In the reset condition, the modem is totally powered down and no clocks are available. After  $\overline{RST}$  is released, the modem will power up, initialize, and go to its idle condition within 10 - 25 milliseconds, and in turn, this causes an ATTN interrupt request and allows CLKO to start toggling at 32.768+ kHz (both of which are default conditions). The ATTN hardware interrupt request is normally caused by asserting modem signal  $\overline{ATTN}$ , however, coming out of reset the ATTN status bit is set and the ATTN interrupt request mask is set.

Once the interrupt request is seen by the MCU, the MCU can assume the modem is alive and ready for programming via the SPI bus. Modem reset operation and control is detailed in Chapter 9, "Miscellaneous Functions".

#### 3.5 MC13202 Interface to MCU

The modem interacts with the host MCU through its SPI interface, interrupt request, and several status and control signals.

#### 3.5.1 SPI Command Channel

Primary interface with the modem is through the SPI command structure that allows reading/writing modem registers and provides initialization of parameters, reading of status, and control of modem operation. The modem is a slave only and the MCU SPI must be programmed and used as a master only. Further, the SPI performance is limited by the modem constraints of 8 MHz maximum SPI clock frequency, and use of the MCU SPI must be programmed to meet the modem SPI protocol. The SPI bus connections for a Freescale 9S08 typically are:

- MCU MOSI1 output drives modem MOSI.

- Modem MISO output drives MCU MISO1.

- MCU SPSCK1 output drives modem SPICLK.

- MCU SS1 output drives modem CE.

The use and programming of the SPI command channel is described in Chapter 5, "Serial Peripheral Interface (SPI)".

### 3.5.2 Interrupt Request to MCU

The modem interrupt request  $\overline{IRQ}$  is an active low open drain output that is asserted when an interrupt request is pending. The signal is released to high by reading the modem IRQ\_Status register via a SPI transaction.  $\overline{IRQ}$  has a programmable pull-up resistor (default is active) and the output also can be programmed for drive strength.  $\overline{IRQ}$  is covered in detail in Section 8.1.2, "Output Pin IRQ", and Section 8.1, "Interrupts".

The IRQ maximum drive strength is suggested as this will give fastest performance for the interrupt fall time.

# 3.5.3 Modem Control Signals

The modem requires two additional input control signals that are typically controlled by the MCU GPIO:

- ATTN is an active low attention signal that is used wake the modem from Hibernate or Doze Mode. An MCU GPIO must be programmed as an output and controls this input.

- RXTXEN is an active high input used to enable transmit, receive, and CCA operations in the modem. An MCU GPIO usually is programmed as an output and controls this input.

# 3.5.4 Modem Status Signals

The modem has two programmable signals that can provide real-time status to the MCU:

- GPIO1/Out\_of\_Idle output The modem GPIO1 signal can optionally be programmed as an "out-of-idle" indicator for monitoring RX, TX, or CCA operation. An MCU GPIO must be programmed as an input to monitor this signal. The modem GPIO1 signal can also be used as a general purpose IO.

- GPIO2/CRC\_Valid output The modem GPIO2 signal can optionally be programmed as an "CRC valid" indicator for monitoring an RX operation. An MCU GPIO must be programmed as an input to monitor this signal. The modem GPIO2 signal can also be used as a general purpose IO.

# 3.6 System Oscillator and Clock Considerations

# 3.6.1 Modem Crystal Oscillator

The modem oscillator source must always be present and an external crystal is used to implement the oscillator. The source frequency must be 16 MHz with a total accuracy of +/- 40 ppm or greater as required by the IEEE 802.15.4 specification. A detailed discussion of required crystal characteristics is in Section 9.3.1, "Crystal Requirements".

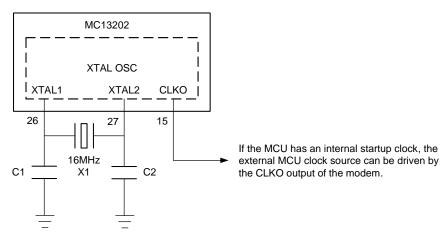

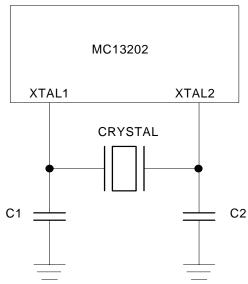

In Figure 3-2 crystal X1 and capacitors C1 and C2 form the modem crystal oscillator circuit. An onboard feedback resistor of approximately 1 MOhm (not shown) between input XTAL1 and output XTAL2 provides DC biasing for the oscillator buffer. An important parameter for the 16 MHz crystal X1 is a load capacitance of <9 pF. The oscillator needs to see a balanced load capacitance at each terminal of about 18pF. As a result, the sum of the stray capacitance of the PCB, device pin (XTAL1 or XTAL2), and load

3-4 Freescale Semiconductor

capacitor (C1 or C2) at each terminal must equal about 18 pF. C1 and C2 are typically values of 6-9 pF. Higher values can load the crystal buffer and cause oscillator start-up problems.

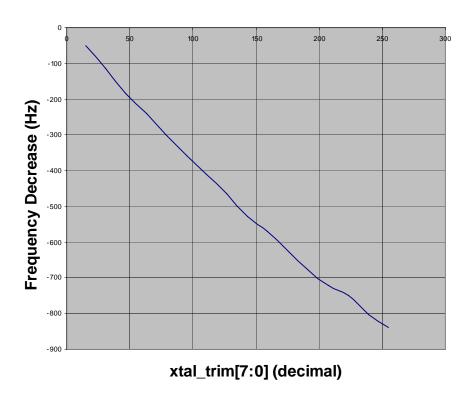

As described in Section 9.3.2, "Crystal Trim Operation", the MC13202 crystal oscillator frequency can be trimmed by programming modem CLKO\_Ctl Register 0A, Bits 15-8 (xtal\_trim[7:0]). The trimming procedure varies the frequency by a few hertz per step, depending on the type of crystal. As xtal\_trim[7:0] is increased, the frequency is decreased. This feature is useful for factory calibration of the crystal frequency to set the accuracy for the radio as required by the IEEE 802.15.4 specification.

Figure 3-2. MC13202 Oscillator and External Clock Connections

# 3.6.2 System Clock Configurations

Because of the multiple clock configurations in an MCU and the CLKO output from the modem, there are a number of variations for system clock configurations. Key considerations for any system clock configuration are:

- The modem 16 MHz source (typically the crystal oscillator) must always be present. The crystal has special requirements and the reference frequency must meet IEEE 802.15.4 requirements

- Battery-operated application requirements for low power can impact the choices for MCU clock source

- The system clock configuration can impact system initialization procedures

- Software requirements can impact MCU processor and bus speed. The user must be aware of the performance requirements for the MCU. In the Freescale software running on the 689S08, the CPU clock is always 2X the internal bus speed, and the application software such as the Freescale BeeStack and/or the IEEE 802.15.4 MAC require either an 8 MHz or 16 MHz bus rate. The implication is that the MCU clock source must be capable of generating these bus speeds

### 3.6.3 Single System Crystal with CLKO driving MCU crystal input

The single crystal (modem crystal) with CLKO driving the MCU external clock input is a common configuration for low cost and excellent frequency accuracy. The CLKO frequency is programmable from 16.393+ kHz to 16 Mhz and drives the MCU external source.

#### NOTE

For this system option to be usable, the system MCU must have an alternative (typically onboard) start-up clock.

In this configuration, clock start-up from a reset condition involves:

- MCU reset is released and MCU starts on an internal clock

- Initialization software must reset and then release reset to the modem (MCU still running on start-up clock)

- Wait for modem start-up interrupt request (approximately 10 25 msec). CLKO default is active with a frequency of 32.786+ kHz

- Program CLKO to a different frequency (if desired)

- Wait for the CLKO source to lock, and then switch MCU clock to external source

Additional considerations for this mode of operation include:

- If the modem is forced to the Off condition and CLKO is killed, there is a 10 25 msec wait for the modem CLKO to start from the Off condition after RST is released

- If the MCU puts the modem into Doze mode, keeping the CLKO alive is a higher power, but available option

- If an accurate period is required for longer time delays (such as a beacon period), keeping CLKO alive for very long periods is an option, but would be a higher power option typically than using a separate crystal for the MCU

#### 3.7 GPIO Characteristics

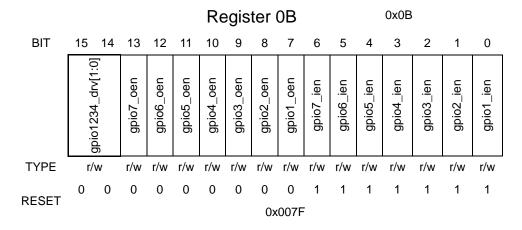

The modem GPIO hardware consists of seven signals total (GPIO1-GPIO7). Immediately after reset, all the GPIO pins are configured as high-impedance general-purpose inputs. There are no internal pullup devices on these pins.

#### **NOTE**

To avoid extra current drain from floating input pins, the power up initialization routine in the application program should change the direction of unused pins to outputs (programmed low) so the pins do not float. Outputs programmed low is the preferred option for lowest power.

As described in Section 3.5.4, "Modem Status Signals", GPIO1 and GPIO2 can be programmed as special status signals. The alternate functionality of the GPIO1-GPIO2 are controlled by the applications program and use of these pins is described in Chapter 9, "Miscellaneous Functions".

3-6 Freescale Semiconductor

The functionality of the modem GPIO is controlled by programming of the modem SPI registers via the SPI interface. For information about controlling all these pins as general-purpose I/O pins, see Chapter 9, "Miscellaneous Functions".

# 3.8 MC13202 Digital Signal Properties Summary

Table 3-2 summarizes digital I/O pin characteristics. These characteristics are determined by the way the common pin interfaces are hard-wired to internal circuits.

Table 3-2. MC13202 Digital Signal Properties

| Pin<br>Name       | Dir | High Current<br>Pin | Output<br>Slew <sup>1</sup> | Pull-Up <sup>2</sup> | Comments                |

|-------------------|-----|---------------------|-----------------------------|----------------------|-------------------------|

| IRQ               | 0   | N                   | SWC                         | SWC                  | Open drain              |

| XTAL1             | 1   |                     |                             | N                    | Open drain              |

|                   | - 1 | _                   | _                           |                      |                         |

| XTAL2             | 0   | N                   | N                           | N                    |                         |

| ATTN              | I   | _                   | _                           | N                    |                         |

| RXTXEN            | I   | _                   | _                           | N                    |                         |

| RST               | Į   | _                   | _                           | N                    |                         |

| CLKO              | 0   | N                   | SWC                         | N                    |                         |

| SPICLK            | I   | _                   | _                           | N                    |                         |

| MOSI              | I   | _                   | _                           | N                    |                         |

| MISO              | 0   | N                   | SWC                         | N                    | Off state is SWC        |

| CE                | I   | _                   | _                           | N                    |                         |

| GPIO1/Out_of_Idle | I/O | N                   | SWC                         | N                    | Programmable status bit |

| GPIO2/CRC_Valid   | I/O | N                   | SWC                         | N                    | Programmable status bit |

| GPIO3             | I/O | N                   | SWC                         | N                    |                         |

| GPIO4             | I/O | N                   | SWC                         | N                    |                         |

| GPIO5             | I/O | N                   | SWC                         | N                    |                         |

| GPIO6             | I/O | N                   | SWC                         | N                    |                         |

| GPIO7             | I/O | N                   | SWC                         | N                    |                         |

SWC is software controlled slew rate, the register is associated with the respective port.

$<sup>^{2}\,</sup>$  SWC is software controlled pull-up resistor, the register is associated with the respective port.

# 3.9 Transceiver RF Configurations and External Connections

The MC13202 radio has features that allow for a flexible as well as low cost RF interface:

- Programmable output power -1dBm to 0 dBm nominal output power, programmable from -27 dBm to +3 dBm typical

- <-92 dBm (typical) receive sensitivity At 1% PER, 20-byte packet (well above IEEE 802.15.4 specification of -85 dBm)

- Optional integrated transmit/receive (T/R) switch for low cost operation With internal PAs and LNA, the internal T/R switch allows a minimal part count radio interface using only a single balun to interface to a single-ended antenna

- Maximum flexibility There are full differential RF I/O pins for use with the internal T/R switch. Optionally, these pins become the RF\_IN signals and a separate set of full differential PA outputs are also provided. Separate inputs and outputs allow for a variety of RF configurations including external LNA and PA for increased range

- CT\_Bias Output The CT\_Bias signal provides a switched bias reference for use with the internal T/R switch, and alternatively can be programmed as an antenna switch signal for use with an external antenna switch

- Onboard trim capability for 16 MHz crystal reference oscillator The IEEE 802.15.4 Standard puts a +/- 40 ppm requirement on the carrier frequency. The onboard trim capability of the modem crystal oscillator eliminates need for external variable capacitors and allows for automated production frequency calibration. Also tighter tolerance can produce greater receive sensitivity

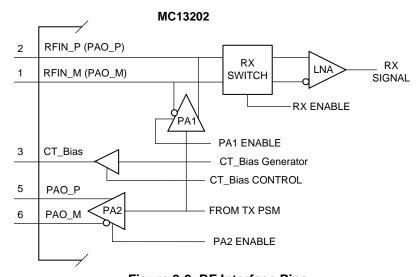

#### 3.9.1 RF Interface Pins

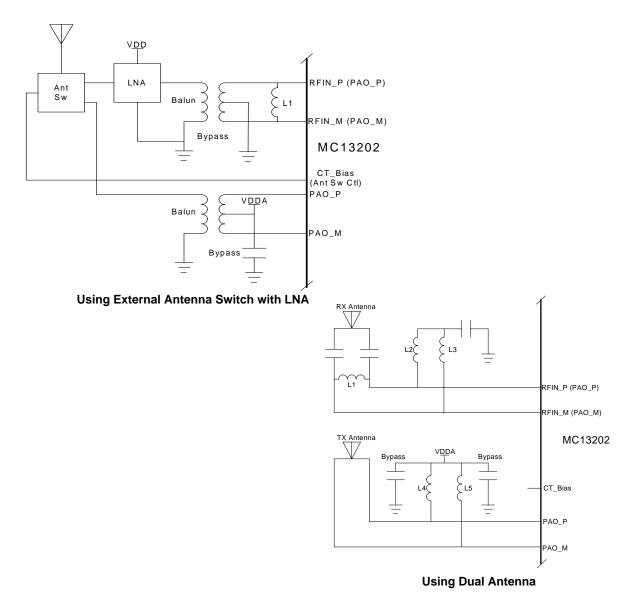

Figure 3-3 shows the RF interface pins and the associated analog blocks. Notice that separate PA blocks are associated with RFIN\_x and PAO\_x signal pairs. The RF interface allows both single port differential operation and dual port differential operation.

Figure 3-3. RF Interface Pins

3-8 Freescale Semiconductor

#### 3.9.1.1 Single Port Operation

The integrated RF switch allows users to operate in a single port configuration. In Single Port Mode, an internal RX switch and separate PA are used and pins RFIN\_P (PAO\_P) and RFIN\_M (PAO\_M) become bidirectional and connect both for TX and RX. When receiving, the RX switch is enabled to the internal LNA and the TX PA1 is disabled. When transmitting, the RX switch is disabled (isolating the LNA) and TX PA1 is enabled. The optional CT\_Bias pin provides a reference or bias voltage which is at VDDA for transmit and is at ground for receive. This signal can be used to provide the proper bias voltage to a balun that converts a single-ended antenna to the differential interface required by the device.

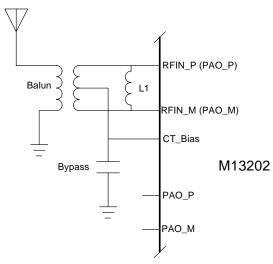

Figure 3-4. Single Port RF Operation with a Balun

Figure 3-4 shows a single port example with a balun. The CT\_Bias is connected to the balun center-tap providing the proper DC bias voltage to the balun depending on RX or TX.

#### 3.9.1.2 **Dual Port Operation**

A second set of pins designated PAO\_P and PAO\_N allow operation in a dual port configuration. There are separate paths for transmit and receive with the optional CT\_Bias pin providing a signal that indicates if the radio is in TX or RX Mode which then can be used to drive an external low noise amplifier or power amplifier.

In dual port operation, the RFIN\_P and RFIN\_N are inputs only, the internal RX switch to the LNA is enabled to receive, and the associated TX PA1 stays disabled. Pins PAO\_P and PAO\_N become the differential output pins and the associated TX PA2 is enabled for transmit.

Figure 3-5 shows two dual port configurations. First is a single antenna configuration with an external low noise amplifier (LNA) for greater range. An external antenna switch is used to multiplex the antenna between receive and transmit. An LNA is in the receive path to add gain for greater receive sensitivity. Two external baluns are required to convert the single-ended antenna switch signals to the differential signals required by the radio. Separate RFIN and PAO signals are provided for connection with the baluns, and the CT\_bias signal is programmed to provide the external switch control. The polarity of the external switch control is selectable.

#### **System Considerations**

Figure 3-5 also shows a dual antenna configuration where there is a RX antenna and a TX antenna. For the receive side, the RX antenna is ac-coupled to the differential RFIN inputs and these capacitors along with inductor L1 form a matching network. Inductors L2 and L3 are ac-coupled to ground to form a frequency trap. For the transmit side, the TX antenna is connected to the differential PAO outputs, and inductors L4 and L5 provide DC-biasing to VDDA but are ac isolated. CT\_Bias is not required or used.

Figure 3-5. Dual Port RF Configuration Examples

MC13202 Reference Manual, Rev. 1.1

3-10

### 3.9.2 Controlling RF Modes of Operation

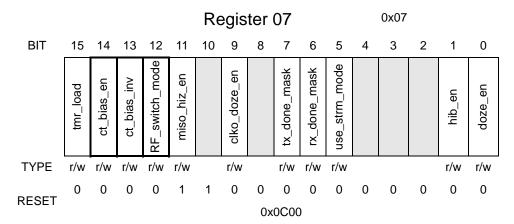

Use of the RF interface pins and RF modes of operation are controlled through several bits of Control\_B Register 07. Figure 3-6 shows the model for Register 07 with the RF interface control bits highlighted.

Figure 3-6. Modem Control\_B Register 07 Model

The RF interface control bits include:

- RF\_switch\_mode (Bit 12) This bit selects Dual Port Mode versus Single Port Mode

- The default condition (Bit 12 = 0) is Dual Port Mode where the RF inputs are RFIN\_M and RFIN\_P and the RF outputs are PAO\_M and PAO\_P and operation is as described in Section 3.9.1.2, "Dual Port Operation". The use of CT\_Bias pin in Dual Port Mode in controlled by Bit 13 and Bit 12

- When Bit = 1, the Single Port Mode is selected where RFIN\_M (PAO\_M) and RFIN\_P (PAO\_P) become bidirectional pins and operation is as described in Section 3.9.1.1, "Single Port Operation". The use of CT\_Bias pin in Single Port Mode in controlled by Bit 14 and operation of the radio

- ct\_bias\_en (Bit 14) This bit is the enable for the CT\_Bias output. When Bit 14 = 0 (default), the CT\_Bias is disabled and stays in a Hi-Z or tri-stated condition. When Bit 14 = 1 the CT\_Bias output is active and its state is controlled by the selected mode (Bit 12), ct\_bias\_inv, and operation of the radio

- ct\_bias\_inv (Bit 13) This bit only affects the state of CT\_Bias when Dual Port Mode is selected and CT\_Bias is active. The CT\_Bias changes state in Dual Port Mode based on the TX or RX state of the radio. The ct\_bias\_inv bit causes the sense of the active state to change or invert based on Bit 13's setting. In this manner the user can select the CT\_Bias as a control signal for external components and make the control signal active high or active low

Table 3-3 summarizes the operation of the RF interface control bits.

Table 3-3. RF Interface Control Bits

| Bit | Designation    | Default | Operation                                                                                                                                                                                                                                          |

|-----|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | ct_bias_en     | 0       | 1 = CT_Bias enabled. Output state is defined by Table 3-4. 0 = CT_Bias disabled. Output state is tri-stated.                                                                                                                                       |

| 13  | ct_bias_inv    | 0       | The output state of CT_Bias under varying conditions is defined in Table 3-4.  This bit only has effect for dual port operation.  1 = CT_Bias inverted.  0 = CT_Bias not inverted                                                                  |

| 12  | RF_switch_mode | 0       | 1= Single Port Mode selected where RF switch is active and RFIN_M and RFIN_P and bidirectional signals. 0 = Dual Port Mode selected where RFIN_M and RFIN_P are inputs only and PAO_P and PAO_N are separate outputs. (This is default operation). |

#### 3.9.3 RF Control Output CT\_Bias

CT\_Bias is a useful signal for interface with external RF components. It must be enabled via the ct\_bias\_en control bit, and then its state is determined first by the selected RF mode and then by the active state of the radio, i.e., whether a TX or RX operation is active:

- Single Port Operation In this mode, the CT\_Bias can be used to establish the proper DC bias voltage to a balun depending on the RX state versus TX state as described in Section 3.9.1.1, "Single Port Operation". Note that in single port operation, the ct\_bias\_inv has no effect and CT\_Bias is at VDDA for TX and is at ground for RX

- Dual Port Operation In this mode, the CT\_Bias can be used as a control signal to enable an LNA or to determine the direction of an antenna switch as described in Section 3.9.1.2, "Dual Port Operation". In dual port operation ct\_bias\_inv is used to control the sense of the output control, i.e., CT\_Bias can be active high or active low for TX and vice-versa for RX

Table 3-4 defines the CT\_Bias output state depending on control bits and operation mode of the modem. Note that the output state is also defined for the modem low power states of Idle, Hibernate, and Doze as well as RX and TX operation.

Table 3-4. CT\_Bias Output vs. Register Settings

| Mode | CT_Bias_en | RF_switch_mode | CT_Bias_inv | CT_Bias |

|------|------------|----------------|-------------|---------|

| RX   | 1          | 1              | 0           | 0       |

| RX   | 1          | 1              | 1           | 0       |

| RX   | 1          | 0              | 0           | 0       |

| RX   | 0          | Х              | Х           | Hi-Z    |

| RX   | 1          | 1              | 0           | 1       |

| TX   | 1          | 1              | 0           | 1       |

| TX   | 1          | 1              | 1           | 1       |

| TX   | 1          | 0              | 0           | 1       |

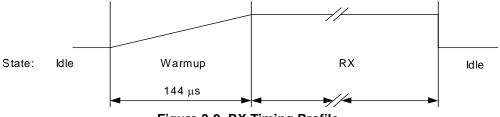

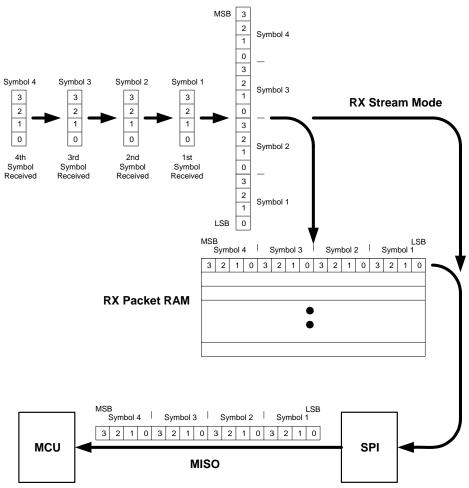

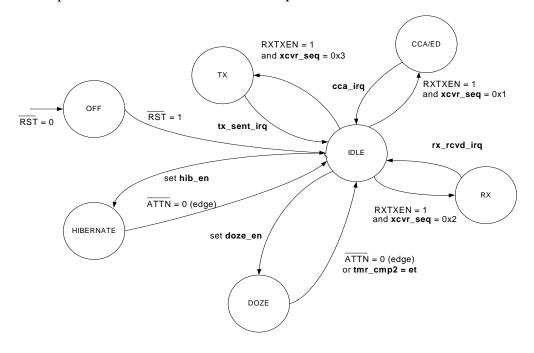

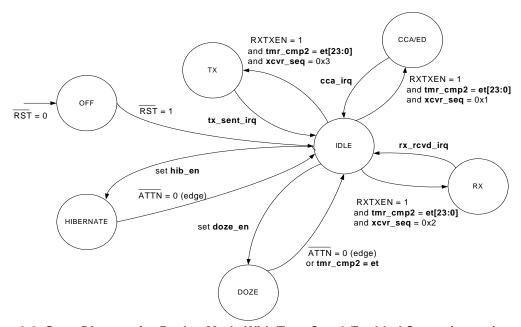

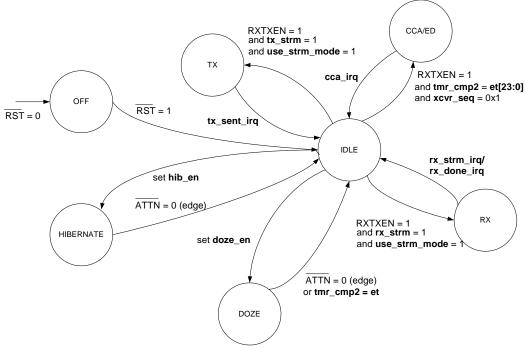

MC13202 Reference Manual, Rev. 1.1