### **OPERATOR'S MANUAL**

### **MODEL 1110**

### **VME ADC/TDC TESTER**

# CE

#### **Corporate Headquarters**

700 Chestnut Ridge Road Chestnut Ridge, NY 10977-6499 Tel: (914) 578-6013 Fax: (914) 578-5985 E-mail: Irs\_sales@lecroy.com Irs\_support@lecroy.com

Copyright© August 1997. LeCroy™ is a registered trademark of LeCroy Corporation. All rights reserved. Information in this publication supersedes all earlier versions.

#### **CE CONFORMITY**

#### CONDITIONS FOR CE CONFORMITY

Since this product is a subassembly, it is the responsibility of the end user, acting as the system integrator, to ensure that the overall system is CE compliant. This product was demonstrated to meet CE conformity using a CE compliant crate housed in an EMI/RFI shielded enclosure. It is strongly recommended that the system integrator establish these same conditions.

# CAUTION

| ELECTROSTATIC<br>DISCHARGE<br>PROTECTION | The Model 1110 is shipped in ESD protective packaging. Do not remove<br>the module from the anti-static packaging unless you are in a static-free<br>environment.                    |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COOLING                                  | It is imperative that the Model 1110 VME ADC/TDC Tester be well cooled. Be sure the cooling fans move sufficient air to maintain an exhaust air temperature of below 50 degrees C.   |

| INSTALLATION                             | Crate Power should be turned OFF during insertion or removal of mod-<br>ules in accordance with the VME bus specification.                                                           |

| SPECIFICATIONS                           | The information contained in this manual is subject to change without notice. The reference for product specification is the Technical Data Sheet effective at the time of purchase. |

# TABLE OF CONTENTS

| 1. General Information                                  |          |

|---------------------------------------------------------|----------|

| 1.1 Purpose                                             | 9        |

| 1.2 Unpacking and Inspection                            | 9        |

| 1.3 Warranty                                            | 9        |

| 1.4 Product Assistance                                  | 9        |

| 1.5 Maintenance Agreements                              | 9        |

| 1.6 Documentation Discrepancies                         | 10       |

| 1.7 Software Licensing Agreement                        | 10       |

| 1.8 Service Procedure                                   | 10       |

| 2. Product Description                                  |          |

| 2.1 Introduction                                        | 11       |

| 2.2 Specifications                                      | 11       |

| 2.3 Controls                                            | 11       |

| 2.3.1 Registers                                         | 11       |

| 2.3.2 Base Address DIP                                  | 11       |

| 2.4 Front Panel Outputs, Switches and Indicators        | 11       |

| 2.4.1 LEMO Outputs                                      | 11<br>12 |

| 2.4.2 Charge Fanout Header                              | 12       |

| 2.4.3 ECL Outputs<br>2.4.4 Other Front Panel Objects    | 12       |

|                                                         | 12       |

| 3. Installation                                         |          |

| 3.1 General Information                                 | 13       |

| 4. Operating Instructions                               |          |

| 4.1 VME Address Map                                     | 15       |

| 4.2 Trigger Register Operation                          | 15       |

| 4.3 Fast Clear Mask and Charge Range Register Operation | 15       |

| 4.3.1 FAST CLEAR Mask                                   | 15       |

| 4.3.2 Charge Range Selection                            | 15       |

| 4.4 Width Register and DAC Operation                    | 15       |

| 4.5 Charge DAC Register Operation                       | 16       |

| 5. Theory of Operation                                  | 17       |

| Calibration Procedures                                  | 19       |

### **GENERAL INFORMATION**

| PURPOSE                     | This manual is intended to provide instruction regarding the setup and operation of the covered instruments. In addition, it describes the theory of operation and presents other information regarding its functioning and application.                                                                                                                                                                                                                                                                                                                  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UNPACKING AND<br>INSPECTION | It is recommended that the shipment be thoroughly inspected immedi-<br>ately upon delivery. All material in the container should be checked<br>against the enclosed Packing List and shortages reported promptly.<br>If the shipment is damaged in any way, please notify the Customer<br>Service Department or the local field service office. If the damage is<br>due to mishandling during shipment, you may be requested to assist in<br>contacting the carrier in filing a damage claim.                                                             |

| WARRANTY                    | LeCroy warrants its instrument products to operate within specifications<br>under normal use and service for a period of one year from the date of<br>shipment. Component products, replacement parts, and repairs are<br>warranted for 90 days. This warranty extends only to the original pur-<br>chaser. Software is thoroughly tested, but is supplied "as is" with no<br>warranty of any kind covering detailed performance. Accessory products<br>not manufactured by LeCroy are covered by the original equipment<br>manufacturers' warranty only. |

|                             | In exercising this warranty, LeCroy will repair or, at its option, replace any<br>product returned to the Customer Service Department or an<br>authorized service facility within the warranty period, provided that the<br>warrantor's examination discloses that the product is defective due to<br>workmanship or materials and has not been caused by misuse, neglect,<br>accident or abnormal conditions or operations.                                                                                                                              |

|                             | The purchaser is responsible for the transportation and insurance charges arising from the return of products to the servicing facility. LeCroy will return all in-warranty products with transportation prepaid.                                                                                                                                                                                                                                                                                                                                         |

|                             | This warranty is in lieu of all other warranties, express or implied, includ-<br>ing but not limited to any implied warranty of merchantability, fitness, or<br>adequacy for any particular purpose or use. LeCroy shall not be liable<br>for any special, incidental, or consequential damages, whether in con-<br>tract, or otherwise.                                                                                                                                                                                                                  |

| PRODUCT ASSISTANCE          | Answers to questions concerning installation, calibration, and use of LeCroy equipment are available from the Customer Service Department, 700 Chestnut Ridge Road, Chestnut Ridge, New York, 10977-6499, (914) 578-6030.                                                                                                                                                                                                                                                                                                                                 |

| MAINTENANCE<br>AGREEMENTS   | LeCroy offers a selection of customer support services. For example,<br>Maintenance Agreements provide extended warranty that allows the<br>customer to budget maintenance costs after the initial warranty has<br>expired. Other services such as installation, training, on-site repair, and<br>addition of engineering improvements are available through specific<br>Supplemental Support Agreements. Please contact the Customer<br>Service Department for more information.                                                                         |

| DOCUMENTATION<br>DISCREPANCIES  | LeCroy is committed to providing state-of-the-art instrumentation and is<br>continually refining and improving the performance of its products. While<br>physical modifications can be implemented quite rapidly, the corrected<br>documentation frequently requires more time to produce. Consequently,<br>this manual may not agree in every detail with the accompanying product<br>and the schematics in the Service Documentation. There may be small<br>discrepancies in the values of components for the purposes of pulse<br>shape, timing, offset, etc., and, occasionally, minor logic changes.<br>Where any such inconsistencies exist, please be assured that the unit is<br>correct and incorporates the most up-to-date circuitry.                                                                                                                                                                                                                                                  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOFTWARE LICENSING<br>AGREEMENT | Software products are licensed for a single machine. Under this license you may:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                 | Copy the software for backup or modification purposes in support of<br>your use of the software on a single machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                 | Modify the software and/or merge it into another program for your use on a single machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                 | Transfer the software and the license to another party if the other<br>party accepts the terms of this agreement and you relinquish all<br>copies, whether in printed or machine readable form, including all<br>modified or merged versions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SERVICE PROCEDURE               | Products requiring maintenance should be returned to the Customer<br>Service Department or authorized service facility. If under warranty,<br>LeCroy will repair or replace the product at no charge. The purchaser is<br>only responsible for the transportation charges arising from return of the<br>goods to the service facility. For all LeCroy products in need of repair<br>after the warranty period, the customer must provide a Purchase Order<br>Number before any inoperative equipment can be repaired or replaced.<br>The customer will be billed for the parts and labor for the repair as well<br>as for shipping. All products returned for repair should be identified by<br>the model and serial numbers and include a description of the defect or<br>failure, name and phone number of the user. In the case of products<br>returned, a Return Authorization Number is required and may be<br>obtained by contacting the Customer Service Department at (914) 578-<br>6030. |

# **PRODUCT DESCRIPTION**

| 2.1 INTRODUCTION                                | The Model 1110 ADC/TDC Tester is a programmable Pulse Generator in a VME 6U x 160mm single width package, primarily designed as a test instrument for servicing VME ADCs and TDCs.              |                                                                                                                                                                                                                                                              |  |  |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                 | difference between<br>For ADC testing, mu<br>available. A FAST C                                                                                                                                | outputs are included for testing TDCs. The time<br>these outputs is programmable with a 16-bit DAC.<br>ultiple charge outputs and a 0-10 V DAC output are<br>CLEAR output is also included. All logic signals have<br>outputs on LEMO and Header connectors. |  |  |

|                                                 | -                                                                                                                                                                                               | are implemented, one for triggering the module and<br>the Full Scale Range of the charge output and mask-<br>Fast Clear.                                                                                                                                     |  |  |

| 2.2 SPECIFICATION                               | ■ VME 6U x 160 r                                                                                                                                                                                | VME 6U x 160 mm single width                                                                                                                                                                                                                                 |  |  |

|                                                 | ■ A24/D16 VME                                                                                                                                                                                   | Module                                                                                                                                                                                                                                                       |  |  |

|                                                 | ■ Responds to the 39, 3B, 3D and                                                                                                                                                                | e following address modifier (AM) codes:<br>3F                                                                                                                                                                                                               |  |  |

|                                                 | ■ Uses 0x0006 lo                                                                                                                                                                                | ocations of A24 VME address space                                                                                                                                                                                                                            |  |  |

|                                                 | Power Requirer                                                                                                                                                                                  | ments: $\pm 12$ and $\pm 5$ V                                                                                                                                                                                                                                |  |  |

| 2.3 CONTROLS                                    |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                              |  |  |

| 2.3.1 Registers                                 | face. Registers are                                                                                                                                                                             | All programmability of Model 1110 outputs are through the VME inter-<br>face. Registers are mapped directly to the VME address space. See the<br>Operating Instructions for implementation.                                                                  |  |  |

|                                                 | Register Name                                                                                                                                                                                   | Description                                                                                                                                                                                                                                                  |  |  |

|                                                 | Trigger                                                                                                                                                                                         | Generates cycle when written to                                                                                                                                                                                                                              |  |  |

|                                                 | Width DAC                                                                                                                                                                                       | Controls START-STOP time difference,<br>GATE width, and DAC LEMO voltage                                                                                                                                                                                     |  |  |

|                                                 | Charge DAC                                                                                                                                                                                      | Controls charge delivered to all charge outputs                                                                                                                                                                                                              |  |  |

|                                                 | Fast Clear /<br>Charge Range                                                                                                                                                                    | Enables/disables Fast clear output, sets charge output range                                                                                                                                                                                                 |  |  |

| 2.3.2 Base Address DIP                          | The module base address is determined by an 8-position DIP switch located near the top of the board (SW1 = A16, SW8 = A24). See installation page for instructions on setting the Base Address. |                                                                                                                                                                                                                                                              |  |  |

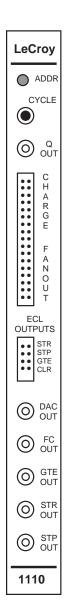

| 2.4 FRONT PANEL OUTPUT<br>SWITCHES AND INDICATO | •                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |  |  |

| 2.4.1 LEMO Outputs                              |                                                                                                                                                                                                 | <b>CHARGE (Q OUT):</b> Programmable in 4 ranges: 0 to 300 pC, 0 to 600 pC, 0 to 900 pC, 0 to 1200 pC; 16 bit resolution.                                                                                                                                     |  |  |

|                                                 | DAC (DAC OUT): 0 to 10 V DC level; 16 bit resolution.                                                                                                                                           |                                                                                                                                                                                                                                                              |  |  |

|                                                 | FAST CLEAR (FC (                                                                                                                                                                                | <b>OUT):</b> 0 to -800 mV pulse, nominal width 30 nsec.                                                                                                                                                                                                      |  |  |

|                                                 | GATE (GTE OUT):<br>30 to 2400 nsec.                                                                                                                                                             | 0 to -800 mV pulse, width programmable                                                                                                                                                                                                                       |  |  |

|                                                 | START (STR OUT)                                                                                                                                                                                 | : 0 to -800 mV pulse, nominal width 10 nsec.                                                                                                                                                                                                                 |  |  |

|                                                 | STOP (STP OUT):                                                                                                                                                                                 | 0 to -800 mV pulse, nominal width 10 nsec.                                                                                                                                                                                                                   |  |  |

|                                                 |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                              |  |  |

| 2.4.2 Charge Fanout Header         | The 1110 has a 16 channel fan-out. The signal pin is on left side of the connector; the right side is tied to ground. It is programmable in 4 ranges: 0 to 300 pC, 0 to 600 pC, 0 to 900 pC, and 0 to 1200 pC. |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.4.3 ECL Outputs                  | Pins on the left side of the connector are -1.8 V quiescent, rising to -0.8 mV when becoming "true". Pins on the left side of the connector are complimentary.                                                 |

|                                    | START (STR): Equivalent of LEMO STR OUT.                                                                                                                                                                       |

|                                    | STOP (STP): Equivalent of LEMO STP OUT.                                                                                                                                                                        |

|                                    | GATE (GTE): Equivalent of LEMO GTE OUT.                                                                                                                                                                        |

|                                    | FAST CLEAR (CLR): Equivalent of LEMO FC OUT.                                                                                                                                                                   |

| 2.4.4 Other Front Panel<br>Objects | <b>Cycle Button:</b> Depressing cycle button initiates trigger cycle.                                                                                                                                          |

| Objects                            |                                                                                                                                                                                                                |

ADDR LED: Flashes to indicates VME access.

### **INSTALLATION**

#### GENERAL

Before inserting the Model 1110 VME ADC/TDC Tester into any VME crate, the base address must first be set. The 8-position DIP switch defines the module VME address, decoded from address lines A16 to A24; e.g., for Address 0x00, set SW1 to SW8 to be CLOSED (UP at the OPEN end of switch).

To set Address 0x80 set SW8 to be OPEN (Down at the OPEN end of switch). To set Address 0x01 set SW1 to be OPEN.

### **OPERATING INSTRUCTIONS**

| 4.1 VME ADDRESS MAP                                           | The Model 1110<br>(hexadecimal):                                                                             | occupies the                         | following VME A24 a                                               | address space                                                                           |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                                                               | Base address + 0x0000 to 0x0006                                                                              |                                      |                                                                   |                                                                                         |

|                                                               | The internal memory map in hexadecimal is as follows:                                                        |                                      |                                                                   |                                                                                         |

|                                                               | Base Address -<br>Base Address -<br>Base Address -<br>Base Address -                                         | + 0x0002: \<br>+ 0x0004: (           | Width DAC Register<br>Charge DAC Registe                          |                                                                                         |

| 4.2 TRIGGER REGISTER<br>OPERATION                             | A24/D16 VME tra                                                                                              | ansfers. Writir<br>nerating STA      | E ONLY" and can on<br>ng anything to the Tr<br>RT, STOP, GATE, F/ | igger register causes a                                                                 |

| 4.3 FAST CLEAR MASK<br>AND CHARGE RANGE<br>REGISTER OPERATION | can only be acce                                                                                             | ssed via A24/<br>3) are used ir      | /D16 VME transfers.<br>this register, detern                      |                                                                                         |

| 4.3.1 FAST CLEAR Mask                                         | VME IDATA0 enables or disables generation of the front panel FAST CLEAR pulse.                               |                                      | e front panel FAST                                                |                                                                                         |

|                                                               |                                                                                                              | Fast clear en<br>FAST CLEAF          |                                                                   |                                                                                         |

| 4.3.2 Charge Range<br>Selection                               | VME IDATA1- IDATA3 are used to provide the CHARGE output selection (duplicating range values are by design): |                                      |                                                                   |                                                                                         |

|                                                               | IDATA3                                                                                                       | IDATA2                               | IDATA1                                                            | CHARGE RANGE                                                                            |

|                                                               | 0<br>0<br>0<br>1<br>1<br>1<br>1                                                                              | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1                              | No Charge Output<br>300 pC<br>300 pC<br>600 pC<br>600 pC<br>900 pC<br>900 pC<br>1200 pC |

| 4.4 WIDTH REGISTER<br>AND DAC OPERATION                       | -                                                                                                            |                                      | -                                                                 | be accessed via A24/<br>nmed by this register                                           |

|                                                               | <ol> <li>The width of t</li> <li>Time interval</li> <li>The voltage of</li> </ol>                            | between the                          | START and STOP or                                                 | utputs.                                                                                 |

3. The voltage output to DAC OUT.

|                                      | For the timing output (numbers 1 and 2 above), the full scale width is 2400 ns, with an LSB of ~36.6 ps. The formula for calculating the appropriate DAC codes and output widths are:                          |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | DAC Code = 65535 * (Desired Value in ns) / 2400                                                                                                                                                                |

|                                      | For the DAC output (number 3 above), the range is 0 to 10 V, with an LSB of ~0.15 mV. The conversion formula is:                                                                                               |

|                                      | DAC Code = 65535 * [1.0- (Desired Value in Volts) / 10 ]                                                                                                                                                       |

| 4.5 CHARGE DAC<br>REGISTER OPERATION | The Charge DAC registers is "WRITE ONLY" and can only be accessed via A24, D16 data transfers. The 16 bit DAC that is programmed by this register controls the charge output to the LEMO and HEADER Q outputs. |

|                                      | Charge DAC Code $= 65535 * [1.0 - (Desired Value in pC) / (Full Scale Range in pC)]$                                                                                                                           |

#### THEORY OF OPERATION

This section is provided to outline the theory behind the hardware. The information is provided to aid the user in understanding the function of this device and is not intended as a guide for repair.

#### 5.1 1110 ADC/TDC TESTER

The VME connector P1, located on sheet 1 of the schematic, contains all the signal and power supply lines used by the module, together with the derived power supplies.

Sheet 2 of the schematic shows the primary interaction with the VME bus. All the VME bus control signals are buffered with U21, U23, U24 and U25 before being decoded by PAL U26. During all VME bus cycles, address bits A16 to A24 are compared with the 8 position DIP switch (Base Address) settings; if valid U23 pin 19 generates a valid address signal which, in turn, generates the latched address strobe (LAS) and delayed address strobe (DLAS) to the PAL, the PAL then generates the VME bus DTACK signal in response.

On addressing the Width DAC register (Base address + 0x0002) the PAL generates WCLK0 and WCLK1 clock signals latching VME data via U13 and U16 into the width DAC (U3). Similarly the Charge DAC register (Base address + 0x0004) clocks QCLK0 and QCLK1 are generated, latching VME data via U14 and U15 into Charge DAC (U2). Monostable U1 is used to drive the front panel led for each accepted VME command and to provide an 100 nsec pulse to drive the Trigger circuit at (Base address + 0x0000). IDATA0 is latched with (Base address + 0x0006) at U18 to provide the Fast Clear enable or disable.

Sheet 3 contains all the timing and the START, STOP, GATE and FAST CLEAR outputs. The width DAC is applied to U11 which provides an attenuated level to the STOP comparator U10 pin 7. A Ramp generator initiated by each trigger command is applied to the START comparator U10 pin 9 and these outputs generate the START, STOP and GATE outputs at both ECL and NIM levels. U4 enables or disables monostable U5 from issuing the FAST CLEAR on the back edge of the GATE pulse, U6 providing the pulse width of the FAST CLEAR signal.

Sheet 4 contains the Charge output circuitry. The QDAC output is applied to the two FETs Q1 and Q5 which are switched by the QSTART pulse to Q3 base. Q5 outputs charge through the Charge Fan-out from panel header, Q1 outputs charge to the front panel Q OUT LEMO connector. This output range is selected by IDATA1, IDATA2 and IDATA3 via U17 and relays K1, K2 and K3.

#### **Calibration Procedure**

#### Model 1110 VME ADC/ADC Tester

- 1. Before inserting the 1110 in the VME Crate, determine the Base Address from the 8-Position DIP switch.

- 2. For this exercise it is assumed the base address is 0x80.

- 3. Switch on and allow 10 minutes to reach stable operating conditions.

- 4. Run any VME Program such as VIC (National Instruments).

- 5. Loop Trigger command 0x800000 a thousand times and check that the Front Panel LED is lit.

- 6. Program the Width DAC to Min. Address 0x800002 set to 0xffff.

**Note:** A value of 0xffff is equivalent to 0 V at the 'DAC OUT' and to Max. START - STOP interval of 2400 nsec.

- 7. Connect DVM to 'DAC OUT' and adjust pot R54 for a reading of 0 V  $\pm$ 10 mV.

- 8. Change data to Max. (0x0000) and adjust pot R52 for 10 V  $\pm$ 10 mV.

- 9. Check for 5.00 V  $\pm$ 10 mV with data set to 0x7fff (Mid Scale).

- 10. Program Width DAC back to Min. (0xfff). Check the voltage at U11 pin 6, should be 2 V  $\pm$ 0.25 V.

- 11. Record the voltage at U10 pin 9. ( -3.000 V ±0.5 V) ....... Vref \_\_\_\_\_

- 12. Change data Max. (0x0000) and adjust pot R102 for a reading at U11 pin 6 of Vref + 800 mV.

- 13. Adjust pot R104 for a reading at U10 pin 10 for a value in Step 12 -20 mV.

Note: Vref = -3.125 V then U11 pin 6 would be -2.325 V and U10 pin 10 -2.345 V.

- 14. Change the data to 0x7fff (Mid Scale).

- 15. Connect Oscilloscope to 'GATE OUT'. Write any data to Base Address (0x800000) and cycle by looping a number of times (10000). Check for 1.2 μsec wide NIM Pulse at 'GATE OUT'.

- 16. Loop checking for 'START OUT' to 'STOP OUT' timing of 1.2  $\mu$ sec.

- 17. Connect 'START OUT' and 'STOP OUT' of the 1110 to the 'START' and 'STOP' of a HP5370B or similar Counter. Set the HP5370B as follows:

| FUNCTION:    | T1                                                     |

|--------------|--------------------------------------------------------|

| STATISTICS:  | Mean                                                   |

| TRIG LVL:    | 0.3 V (Channels A & B)                                 |

| SAMPLE SIZE: | 100                                                    |

| ARMING:      | +T1 Only                                               |

| INPUTS:      | Slope Neg, 50 $\Omega$ , ÷1, DC, STEP (Channels A & B) |

18. Program Width DAC back to Min. (0xffff). Write any data to Base Address (0x800000) and cycle by looping a number of times (10000). Adjust pot R101 for a reading of 2400 nsec ±1 nsec.

- 19. Program Width DAC to (0x0334). Write any data to Base Address (0x800000) and cycle by looping a number of times (10000). Adjust pot R104 for a reading of 30 nsec ±1 nsec.

- 20. Program the Q DAC to Min. Address 0x800004 set to 0xffff.

- 21. Connect DVM to U2 pin 17 and adjust pot R51 for a reading of 0 V  $\pm 10$  mV.

- 22. Change data to Max. (0x0000) and adjust pot R48 for 10.00 V  $\pm 10$  mV.