# **OPERATOR'S MANUAL**

MODEL 1875A (1872A) FASTBUS TIME-TO-DIGITAL CONVERTERS

#### **Corporate Headquarters**

700 Chestnut Ridge Road Chestnut Ridge, NY 10977-6499 Tel: (914) 578-6013 Fax: (914) 578-5984

#### **European Headquarters**

2, rue du Pre-de-la-Fontaine P.O. Box 341 1217 Meyrin 1 Geneva, Switzerland Tel: (022) 719 21 11 Fax: (022) 719 22 30

Copyright<sup>©</sup> June 1994. LeCroy is a registered trademark of LeCroy Corporation. All rights reserved. Information in this publication supersedes all earlier versions. Specifications are subject to change.

## 1. General Information

2.

3.

4.

| Purpose                                 | 1-1        |

|-----------------------------------------|------------|

| Unpacking and Inspection                | 1-1        |

| Warranty                                | 1-1        |

| Product Assistance                      | 1-1        |

| Maintenance Agreements                  | 1-1        |

| Documentation Discrepancies             | 1-2        |

| Software Licensing Agreement            | 1-2        |

| Service Procedure                       | 1-2        |

| Product Description                     |            |

| Overview                                | 2-1        |

| Features                                | 2-1        |

| Other Features                          | 2-1        |

| Installation                            |            |

| Equipment Needed                        | 3-1        |

| Resolution                              | 3-1        |

| Inputs                                  | 3-1        |

| Standard Input Scheme                   | 3-1        |

| Control Signal Inputs                   | 3-2        |

| Com                                     | 3-2        |

| Measure Pause Interval (MPI)            | 3-3        |

| Clear<br>Trigger Outpute                | 3-3        |

| Trigger Outputs<br>Hits                 | 3-3<br>3-3 |

| Acquisition Timeout                     | 3-3        |

| Operating Instructions                  |            |

| N vs F Operating Modes                  | 4-1        |

| Chapter Organization                    | 4-1        |

| Initial Checkout                        | 4-1        |

| Read the Module Identification and Mode | 4-2        |

| Internal Test Pulsing and Readout       | 4-2        |

| Using the Test Pulser                   | 4-3        |

| Checkout Using the Test Pulser and the  |            |

| LeCroy Model 1810 CAT                   | 4-4        |

| CSR0 Write                              | 4-6        |

| Bit Type Definitions                    | 4-6        |

| Control Bits                            | 4-7        |

| Pulsed Bits                             | 4-7        |

| CSR0 Read                               | 4-8        |

| Output Data Word                        | 4-9        |

| N Mode Operation                        | 4-10       |

| N Mode                                  | 4-10       |

| N Mode Readout Scheme                   | 4-11       |

| F Mode Operation                        | 4-15 |

|-----------------------------------------|------|

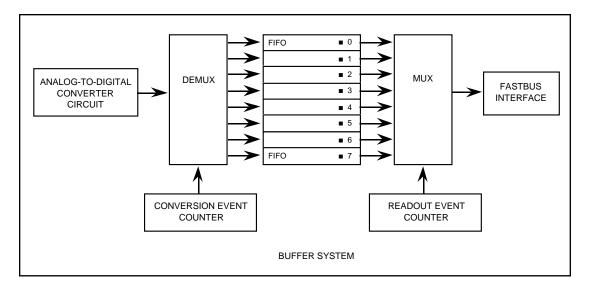

| The Internal Data Buffer                | 4-15 |

| Conversion in Progress (CIP) and WAIT   | 4-16 |

| Slave Status Responses                  | 4-16 |

| FASTBUS Broadcast Functions             | 4-17 |

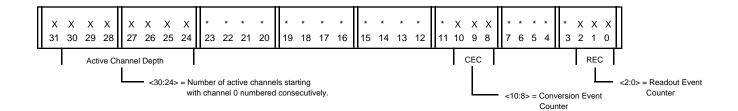

| CSR1                                    | 4-18 |

| Writing to FASTBUS Register CSR1        | 4-19 |

| Depth Field                             | 4-19 |

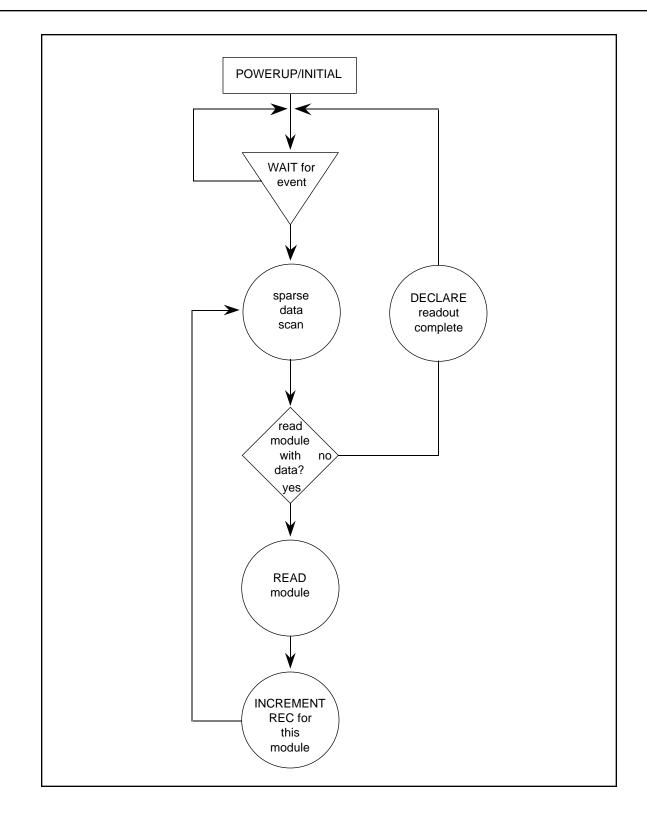

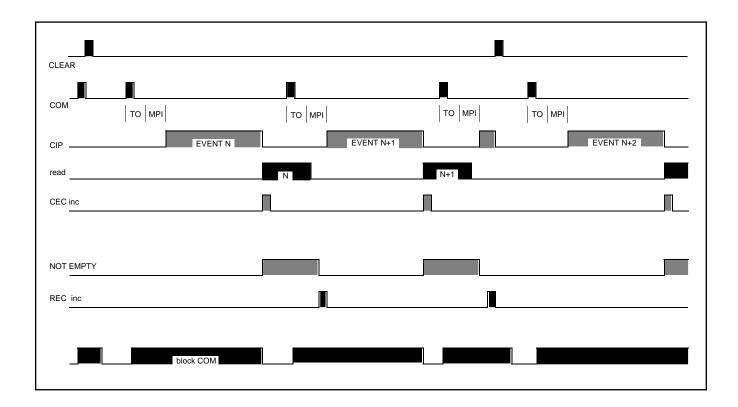

| F Mode Readout Schemes                  | 4-20 |

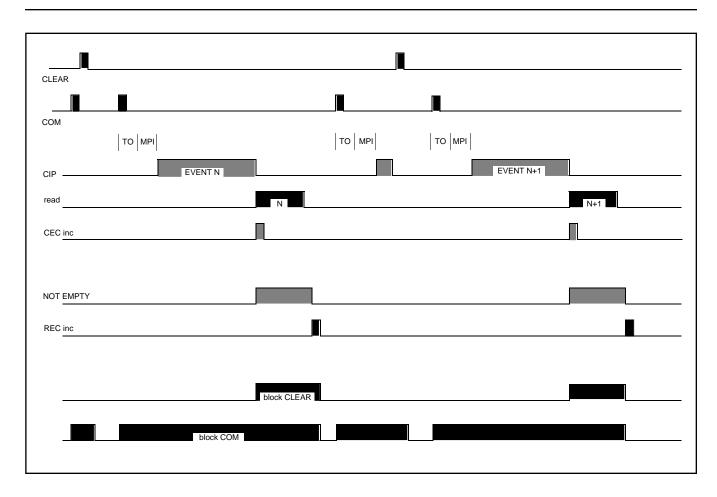

| F Mode - Readout with Next COM and      |      |

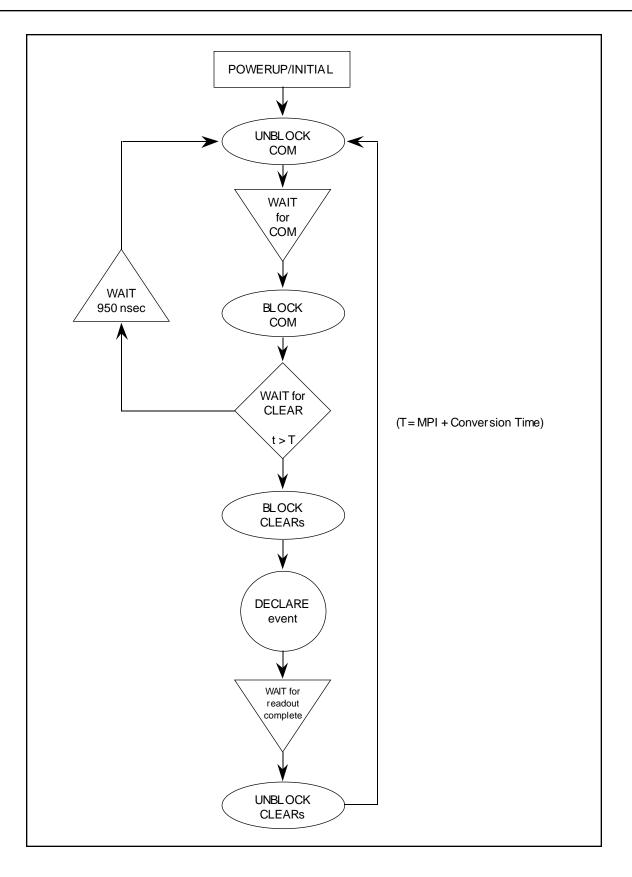

| CLEARs Blocked                          | 4-20 |

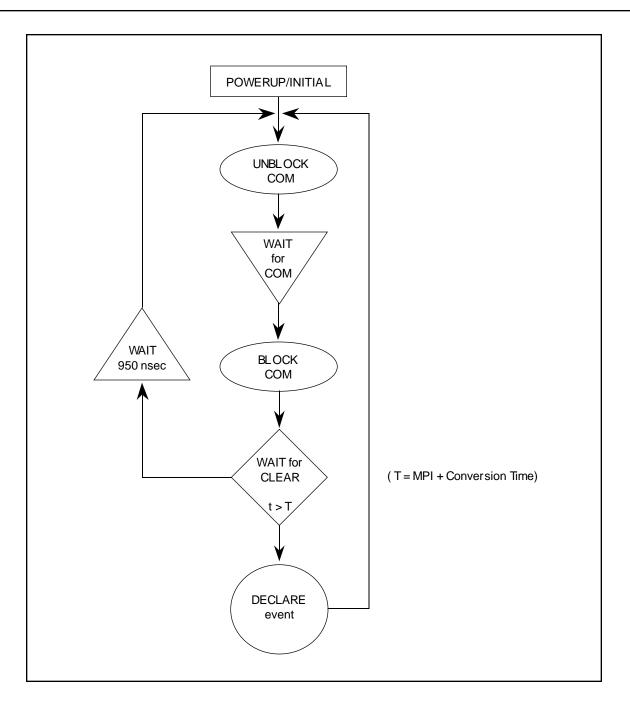

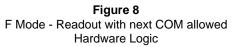

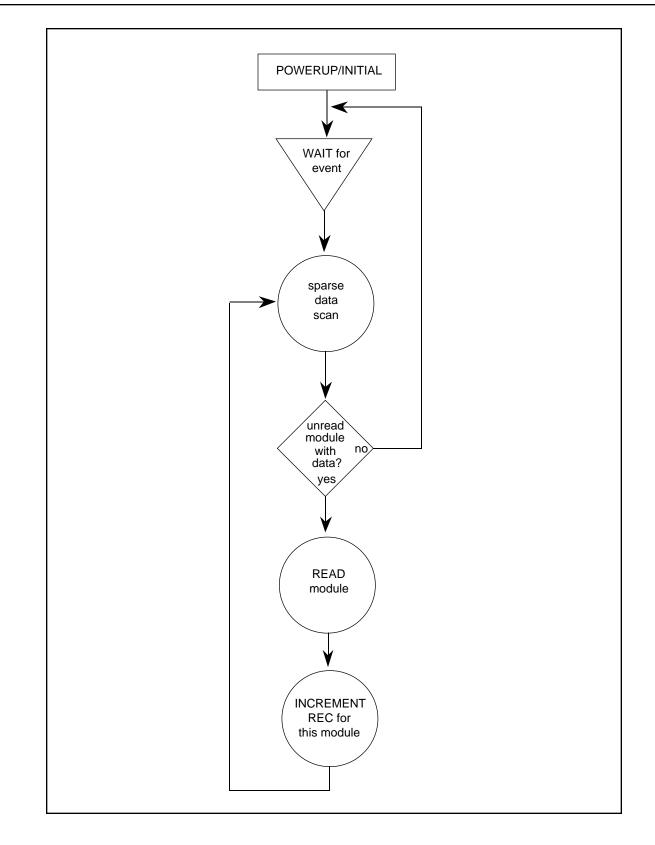

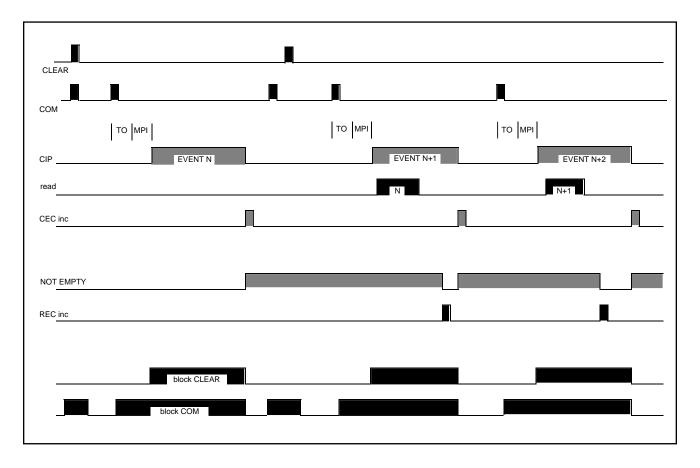

| F Mode - Readout with Next COM Allowed  | 4-24 |

| F Mode - Readout During Next Conversion |      |

| with CLEARs Blocked                     | 4-28 |

| F Mode - Readout During Next Conversion | 4-32 |

| Theory of Operation                     |      |

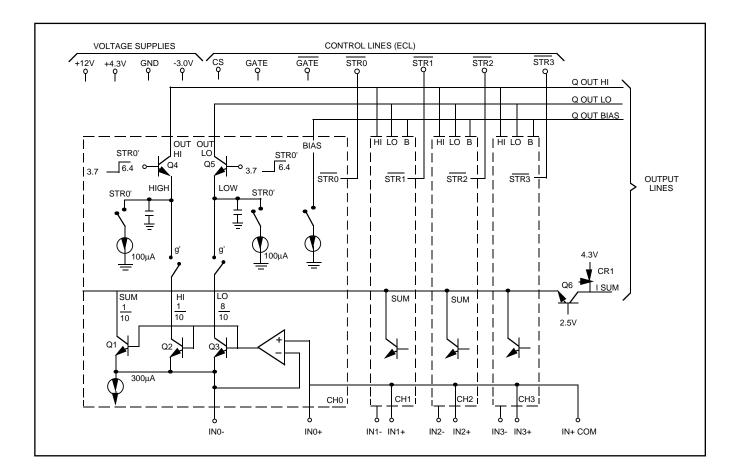

| MIQ401 - Input Monolithic               | 5-1  |

| Time-to-Charge Conversion               | 5-2  |

| Multiplexing and Conversion             | 5-2  |

| Q_OUT Bus Interface                     | 5-3  |

| Integrators                             | 5-3  |

| Range Select                            | 5-4  |

| 3X Amplifier and Level Shifter          | 5-4  |

| Calibration                             | 5-4  |

|                                         |      |

## 6. Additional Information

5.

| Auxiliary Connector        | 6-1 |

|----------------------------|-----|

| Fast Control Signals       | 6-1 |

| User CSR Data Bus          | 6-1 |

| AFC Voltages               | 6-1 |

| AFC T-Pin Assert Broadcast | 6-1 |

| Trigger Outputs            | 6-1 |

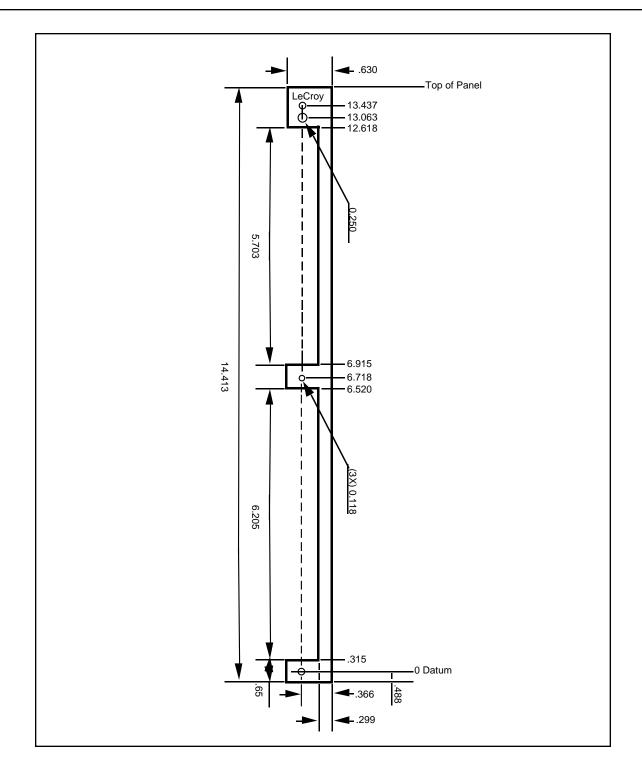

| Front Panel Dimensions     | 6-1 |

# CAUTION

| COOLING              | The high power dissipation of the $1872A/75A^*$ requires that it be well cooled. It is suggested that a FASTBUS bin fan be used to maintain exhaust air temperature at less than $50^\circ$ C.                                                                                                                                                                                                                                                                  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER<br>REQUIREMENT | The 1872A/75A uses significant power from the +5 V and -5.2 V power lines as well as -2 V and $\pm$ 15 V power lines for most of its analog circuitry. Although power consumption to the $\pm$ 15 V lines is relatively small; clean, ripple free, low noise supply voltages are needed to guarantee the performance of the 1872A/75A. Be sure that your crate can supply enough current to this and other modules, especially if multiple 1872A/75As are used. |

|                      | Also, achieving optimum performance from the 1872A/75A requires the power supply to meet FASTBUS specifications, particularly regarding noise.                                                                                                                                                                                                                                                                                                                  |

| SPECIFICATIONS       | The information contained in this manual is subject to change without notice. The reference for product specification is the Technical Data Sheet effective at the time of purchase.                                                                                                                                                                                                                                                                            |

| PURPOSE                     | This manual is intended to provide instruction regarding the setup and operation of the Model 1872A/75A. In addition, it describes the theory of operation and presents other information regarding its functioning and application.                                                                                                                                                                                                                                                                                                                 |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UNPACKING AND<br>INSPECTION | It is recommended that the shipment be thoroughly inspected immediately upon<br>delivery. All material in the container should be checked against the enclosed<br>Packing List and shortages reported promptly. If the shipment is damaged in any<br>way, please notify the Customer Service Department or the local field service<br>office. If the damage is due to mishandling during shipment, you may be<br>requested to assist in contacting the carrier in filing a damage claim.                                                             |

| WARRANTY                    | LeCroy warrants its instrument products to operate within specifications under<br>normal use and service for a period of one year from the date of shipment.<br>Component products, replacement parts, and repairs are warranted for 90 days.<br>This warranty extends only to the original purchaser. Software is thoroughly<br>tested, but is supplied "as is" with no warranty of any kind covering detailed<br>performance. Accessory products not manufactured by LeCroy are covered by<br>the original equipment manufacturers' warranty only. |

|                             | In exercising this warranty, LeCroy will repair or, at its option, replace any product returned to the Customer Service Department or an authorized service facility within the warranty period, provided that the warrantor's examination discloses that the product is defective due to workmanship or materials and has not been caused by misuse, neglect, accident or abnormal conditions or operations.                                                                                                                                        |

|                             | The purchaser is responsible for the transportation and insurance charges arising from the return of products to the servicing facility. LeCroy will return all in-<br>warranty products with transportation prepaid.                                                                                                                                                                                                                                                                                                                                |

|                             | This warranty is in lieu of all other warranties, express or implied, including but<br>not limited to any implied warranty of merchantability, fitness, or adequacy for<br>any particular purpose or use. LeCroy shall not be liable for any special,<br>incidental, or consequential damages, whether in contract, or otherwise.                                                                                                                                                                                                                    |

| PRODUCT ASSISTANCE          | Answers to questions concerning installation, calibration, and use of LeCroy equipment are available from the Customer Service Department, 700 Chestnut Ridge Road, Chestnut Ridge, New York, 10977-6499, (914) 578-6030, or your local field service office.                                                                                                                                                                                                                                                                                        |

| MAINTENANCE<br>AGREEMENTS   | LeCroy offers a selection of customer support services. For example,<br>Maintenance Agreements provide extended warranty that allows the customer to<br>budget maintenance costs after the initial warranty has expired. Other services<br>such as installation, training, on-site repair, and addition of engineering<br>improvements are available through specific Supplemental Support Agreements.<br>Please contact the Customer Service Department or the local field service office<br>for details.                                           |

| DOCUMENTATION                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DISCREPANCIES                   | LeCroy is committed to providing state-of-the-art instrumentation and is<br>continually refining and improving the performance of its products. While physical<br>modifications can be implemented quite rapidly, the corrected documentation<br>frequently requires more time to produce. Consequently, this manual may not<br>agree in every detail with the accompanying product and the schematics in the<br>Service Documentation. There may be small discrepancies in the values of<br>components for the purposes of pulse shape, timing, offset, etc. and<br>occasionally, minor logic changes. Where any such inconsistencies exist, please<br>be assured that the unit is correct and incorporates the most up-to-date circuitry. |

| SOFTWARE LICENSING<br>AGREEMENT | Software products are licensed for a single machine. Under this license you may:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                 | <ul> <li>Copy the software for backup or modification purposes in support of your<br/>use of the software on a single machine.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 | <ul> <li>Modify the software and/or merge it into another program for your use on<br/>a single machine.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                 | • Transfer the software and the license to another party if the other party accepts the terms of this agreement and you relinquish all copies, whether in printed or machine readable form, including all modified or merged versions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SERVICE PROCEDURE               | Products requiring maintenance should be returned to the Customer Service<br>Department or authorized service facility. If under warranty, LeCroy will repair or<br>replace the product at no charge. The purchaser is only responsible for the<br>transportation charges arising from return of the goods to the service facility.                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                 | For all LeCroy products in need of repair after the warranty period, the customer must provide a Purchase Order Number before any inoperative equipment can be repaired or replaced. The customer will be billed for the parts and labor for the repair as well as for shipping.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                 | All products returned for repair should be identified by the model and serial<br>numbers and include a description of the defect or failure, name and phone<br>number of the user. In the case of products returned, a Return Authorization<br>Number is required and may be obtained by contacting the Customer Service<br>Department in New York.                                                                                                                                                                                                                                                                                                                                                                                         |

|                                 | Research Systems Division Customer Service (914) 578-6030                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| OVERVIEW       | The LeCroy Model 1872A and 1875A are fast converting, Common Start, sparsifying, 64-channel, time-to-digital converter modules designed for forefront elementary particle or nuclear physics experiments.                                                                                                                                                                                                                                                                                                                                                   |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Each of the 64 inputs stop the measurement of a time which is started by the com input common to all channels. All inputs are DC-coupled, ECL. The 64 time signals are digitized and the results stored in the module's memory.                                                                                                                                                                                                                                                                                                                             |

|                | The module's physical dimensions, power requirements, control and readout protocol are in compliance with the FASTBUS ECL standard as outlined in the document, IEEE-960-1986. Up to 23 modules may be installed in an appropriately powered crate providing a total of 23x64 = 1472 TDC channels (in a standard 25 slot crate allowing two slots for a master). Larger systems can be built (within the FASTBUS specification) by connecting crate segments via Segment Interconnects (SI) or a LeCroy Model 1821 Segment Manager/Interface (SM/I) module. |

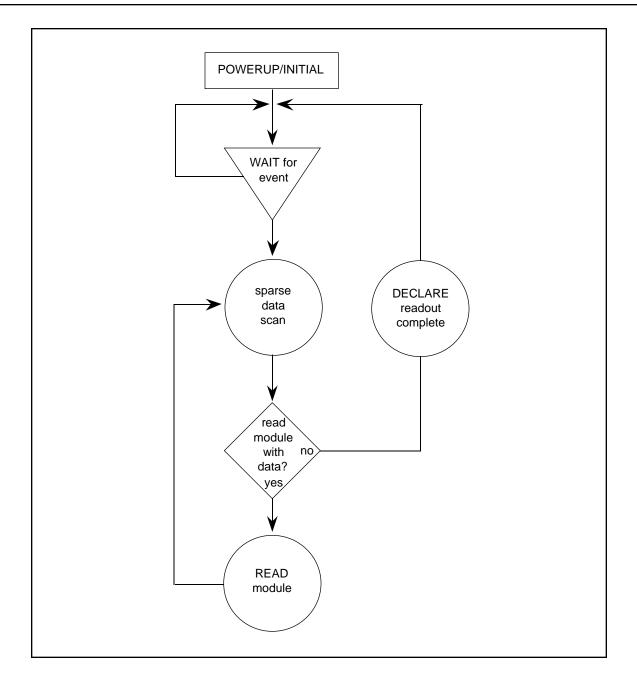

| FEATURES       | The 1872A/75A employs a sparsification scheme to reduce conversion and readout time. Only channels which were hit are digitized and stored. Conversion time varies with the number of hits and is 10 $\mu$ sec + 2.5 $\mu$ sec per hit. A typical, 8 hit event will be converted in less than 30 $\mu$ sec and a full 10 MHz data readout rate is supported in FASTBUS block transfer mode. Thus, a full crate with 184 hit channels (typical case) can be read out in less than 20 $\mu$ sec (not including FASTBUS Master readout time).                  |

|                | The 1872A/75A digitizes time intervals with three jumper selectable resolutions: 25 psec/count, 50 psec/count, or 100 psec/count. Jumpers marked RESOLUTION, TESTER RESOLUTION AND RESOLUTION P4, P1 and P20 respectively, must be changed as indicated on the module, when changing resolutions. These settings result in full scale ranges of 100 nsec, 200 nsec, or 400 nsec for the 1872A. The 1875A has eight times greater full range as discussed below. See Chapter 5 for calibration details.                                                      |

|                | The 1872A/75A also contains an internal buffer for multiple events which may be<br>used to eliminate data readout time as a contributor to experimental dead time.<br>Data for the previous event can be read out while the current event is still being<br>converted. Use of this internal buffering is exactly the same as in the LeCroy<br>Model 1882/85F ADC modules and is referred to as F Mode Operation.<br>Operation without internal buffering is referred to as N mode.                                                                          |

| OTHER FEATURES | The 1872A digitizes time events into 12 bits. The 1875A provides a 15-bit dynamic range via 12-bit data word and a range bit (X8 or X1). The 1875A may be configured to automatically select the appropriate range for each channel on an event-by-event basis.                                                                                                                                                                                                                                                                                             |

|                | The module automatically clears the front end at the end of conversion although digitizing may be interrupted at any time and the modules reset for a new START by applying a CLEAR signal.                                                                                                                                                                                                                                                                                                                                                                 |

|                | An on-board pulser permits time calibration of the TDC channels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                | Sixty-four trigger outputs permit easy trigger logic interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| EQUIPMENT NEEDED | One FASTBUS crate with the following voltage sources connected properly to backplane: +5.0 V (3.4 A), -5.2 V (5.0 A), -2.0 V (2.0 A), +15.0 V (0.6 A), -15.0 V (0.3 A). The crate should be an ECL backplane implementation.                                                                                                                                                                                                                                                                                                                      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | FASTBUS Ancillary Logic such as the Struck Geographical Address Control Card (GAC) Model STR162 and the Arbitration Timing Control Card (ATC) Model STR163. The GAC card should be placed in the rear crate backplane in slot #23 (or 24 or 25) and the ATC card in slot #2 (or 3 or 4). If the crate also has two rear back-planes these cards should be plugged into the lower of the two backplanes. Also, inspect jumper settings on these cards and compare with manufacturer's recommendations.                                             |

|                  | A Crate Master, such as LeCroy Model 1821 Segment Manager Interface (SM/I), to execute standard FASTBUS cycles for control of module and transfer of data to the user's computer.                                                                                                                                                                                                                                                                                                                                                                 |

|                  | A Processor Interface (PI) such as a LeCroy Model 1821/DEC interface card with<br>a DEC DR11-W Unibus of MDB DRV11-2 Qbus parallel I/O board used with the<br>DEC computer line. A less expensive way of getting started with FASTBUS (for<br>example, to check out a small number of crates of FASTBUS modules) is to use<br>an IBM PC/AT <sup>™</sup> with a LeCroy Model 1691A Interface Card which connects to<br>the front panel of a LeCroy Model 1821 SM/I via a LeCroy DC4/34 data cable.                                                 |

|                  | The software package LIFT (LeCroy Interactive FASTBUS software Toolkit) is<br>available for the 1691A/IBM PC system providing the user with a substantial<br>package of software to exercise and test FASTBUS modules with a LeCroy SM/I<br>1821. LIFT also includes an extensive software library which the user may<br>employ in the development of his own data acquisition software.                                                                                                                                                          |

| RESOLUTION       | Remove the side cover of the module and select the desired resolution with jumpers marked RESOLUTION, TESTER RESOLUTION and RESOLUTION (P4, P1 and P20 respectively) as indicated on the board. Although the time interval measurements have three coarse settings of full scale, each with an automatic low and high range change, the on-board test pulser relies entirely upon manual jumper adjustments. REMEMBER - ensure that all jumpers are set for the same resolution (see Section 4, "Using the Test Pulser"). Replace the side cover. |

| FULL SCALE       | The acquisition timeout can be manually set to allow for 12-bit operation only.<br>The P21 jumper normally is set to the 15-bit position. This allows for software<br>selection of 12- or 15-bit range via CSR0. If only 12-bit (low range) operation is<br>desired, the P21 jumper can be set to the 12-bit position. This will reduce the<br>acquisition timeout by a factor of 8, but auto range and high range operation will<br>be adversely affected. When P21 is set to 12-bit, the unit must be operated in<br>Low Range only.            |

#### INPUTS Standard Input Scheme

The use of coax cables as signal cables generally results in less pick-up of noise and EMI signals (especially when long cables are employed) and less crosstalk due to the concentric shielding of the center conductor.

The use of twisted-pair cables generally results in lower cabling costs. Care should be taken by the user to install high quality, shielded cables with randomly twisted-pairs to minimize the effects of noise pickup and crosstalk.

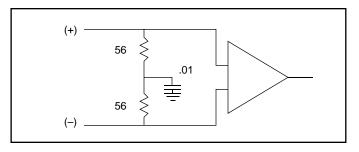

All hit inputs are differential ECL and terminated by 112  $\Omega$  as shown. The terminations are SIP components and may be easily replaced to accommodate other transmission line, characteristic impedances.

#### CONTROL SIGNAL INPUTS

The following sections discuss module control signals sent to the module front panel or the FASTBUS backplane TR lines and include COM (Common), MPI (Measure Pulse Interval), and CLEAR. The COM and CLEAR signals can be triggered via writing appropriate bits in CSR0 (Control and Status Register 0), using standard FASTBUS protocol. The CSR0 bit definitions, use of the on-board pulser calibration, and the module signals used for FASTBUS data readout are discussed in later sections. COM and CLEAR may also be applied via front panel differential ECL input or via TR lines from a LeCroy Model 1810 CAT (calibration and timing) module, for example.

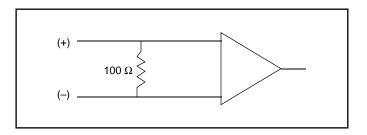

The differential ECL inputs are asserted when the pin labeled "+" is ECL high and the pin labeled "-" is ECL low. The COM and CLEAR front panel inputs are terminated into 100  $\alpha$  resistors, as shown.

3

| СОМ            | The beginning of the time interval which is digitized is defined by the COM signal<br>and is common to all 64 channels. The COM signal is routed to all channels. The<br>variation in COM edge receipt between the 64 channels is no more than 5 nsec.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Digital conversion will begin after the trailing edge of the MPI signal (see below).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | A user COM can be applied to the module either through a differential ECL input,<br>2-pin front-panel connector or via the TR5 line on the FASTBUS backplane. The<br>LeCroy Model 1810 CAT module may be used to apply both COM and CLEAR<br>signals to the crate backplane. However, CAT COM must be enabled via CSR0,<br>and this will disable the front panel STOP. The 1810 CAT module "ICA STOP"<br>front panel input controls the leading edge of the FASTBUS TR5 line which the<br>1872A/75A can use as its Common Start.                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | In addition, the module may be started under program control by writing a "1" to CSR0<11>.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MEASURE PAUSE  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

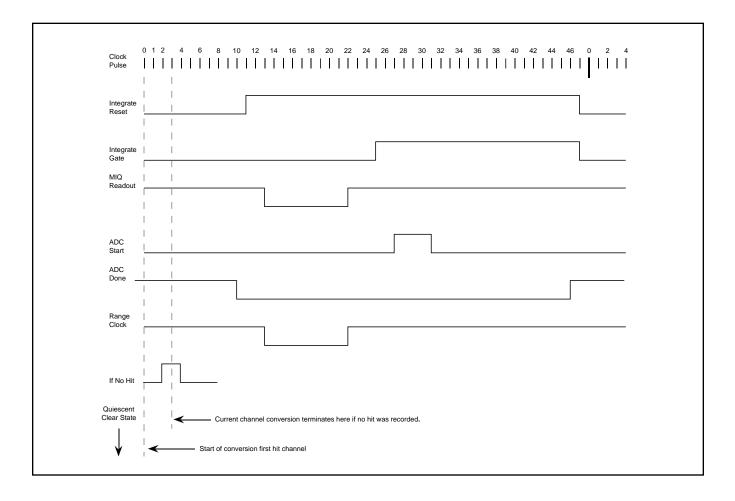

| INTERVAL (MPI) | After a full scale timeout period measured from the COM arrival, the module disables acquisition and waits for an adjustable time period (referred to as the Measure Pause Interval, MPI) from the leading edge before it initiates a digitization or conversion cycle. Within limits, the MPI may be adjusted to provide additional time for experimental trigger logic to issue a CLEAR prior to conversion. Via appropriate bits in CSR0, the MPI may be determined by a labeled on-board potentiometer, MPI, or an external ECL signal applied to the FASTBUS line TR5. In the latter case, the end of the MPI is determined by the trailing edge of the applied ECL signal. This signal can be conveniently generated by the LeCroy Model 1810 CAT module. Use of the external MPI is strongly recommended for crates of multiple TDC modules to avoid possible module-to-module variations in the on-board potentiometer settings. |

|                | A time of 1 $\mu$ sec is the minimum recommended MPI. Settings less than 1 $\mu$ sec are possible with this module but channel zero may not attain the TDC resolution specification. Diminished resolution due to a short MPI setting should be expected to vary between modules. A time of 500 $\mu$ sec is the maximum recommended MPI. Larger MPIs are permitted but performance becomes limited by the storage time of internal capacitors in the Qmux which should start to show significant droop after a millisecond. The on-board MPI potentiometer is typically set at the factory to 10 $\mu$ sec.                                                                                                                                                                                                                                                                                                                             |

| CLEAR          | A CLEAR signal may be sent to the module at any time and the module will be<br>ready to receive another COM 950 nsec later. The CLEAR terminates all<br>operations unconditionally and returns the module to the quiescent state. The<br>FASTBUS registers are unaffected by a clear. A CLEAR signal may be applied to<br>the module either through the 2-pin front-panel differential ECL input, or via a<br>single ended ECL signal on the TR0 line on the FASTBUS backplane. A jumper<br>must be in place, however, to permit CLEAR via the TR0 line. A module CLEAR<br>can also be generated under program control by writing a "1" to the appropriate<br>bit of CSR0.                                                                                                                                                                                                                                                               |

| TRIGGER OUTPUTS     | During MPI, the hit data is available on the FASTBUS Aux connector of the trigger logic interface. Each of the 64 trigger ECL lines representing Channels 0 to 63 will go low if the corresponding channel was hit. This data is valid only during MPI.                                                                                                                                                                                                                                                                                                                |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HITS                | In order to provide better performance of the TDC, a 45 nsec delay is required between the arrival of the COM and the earliest hit. Hits which arrive in less than 45 nsec after the COM will not be registered. Delaying the hits by a 45 nsec cable delay with respect to the COM will satisfy this requirement.                                                                                                                                                                                                                                                     |

| ACQUISITION TIMEOUT | The arrival of the COM starts acquisition of hits. When the acquisition timeout interval is over, acquisition is terminated and the MPI begins. The acquisition timeout delay is a function of both the resolution setting and the maximum number of bits to be digitized. The P20 jumper sets the LSB weighting; 25, 50 or 100 psec per LSB are selectable. Note that there is a corresponding jumper, P4, as well as P1 for the tester that should be set to the same setting.                                                                                       |

|                     | Normally, the acquisition timeout is equal to approximately 1.2 times the resolution setting times 32,768. This is ideal for 15-bit operation. In the event that only 12-bit operation is desired, the P21 jumper can reduce the acquisition timeout by a factor of 8 by selecting the 12-bit position. Note that there is a corresponding jumper, P57, for the tester that should be set to the same setting.                                                                                                                                                         |

| CIP                 | The Conversion in Progress Signal (CIP) is available on the front panel of the 1875A. A pair of jumper holes labeled "CIP" and "TR7" near the FASTBUS connector allows bringing the CIP signal to the FASTBUS TR7 line. This signal could be used in a wire or'ed configuration to interface with trigger logic, for example. It is up to the user to ensure that there are no conflicts in the FASTBUS crate over the use of TR7. Note that the LeCroy 1810 CAT modules use TR7 to distribute a clock reference and would be incompatible with the use of CIP on TR7. |

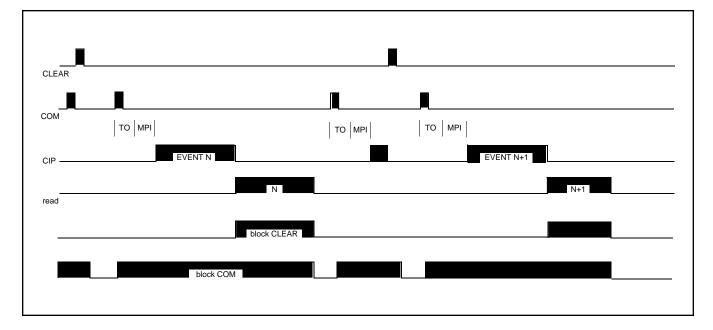

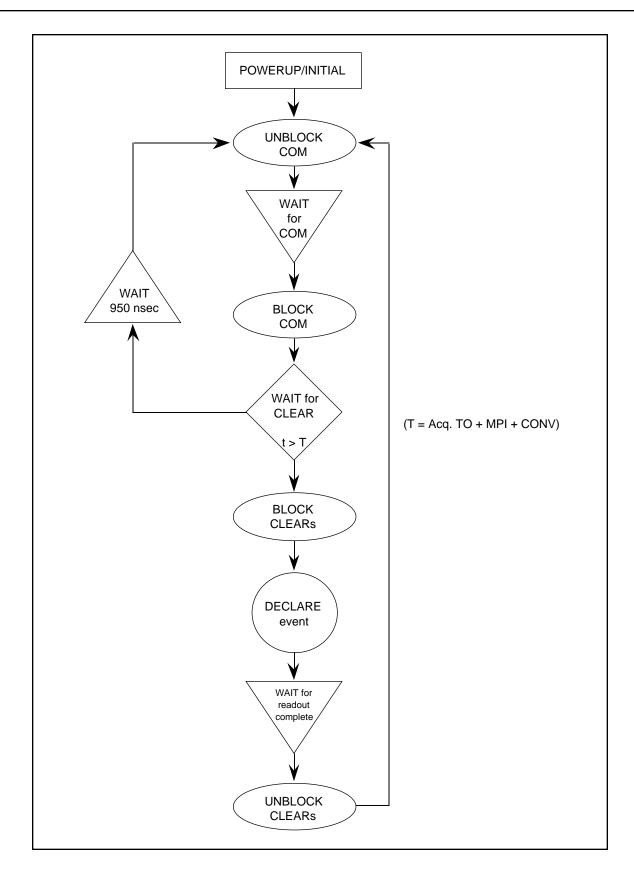

| N VS. F<br>OPERATING MODES | The 1872A/75A TDCs contain an internal buffer which can hold up to 8 events (each containing up to 64 words of data) in the module. Appropriately managed, this buffer can be used to virtually eliminate the contribution of data readout time to experimental dead time. However, for compatibility with other unbuffered FASTBUS slaves use of the N mode is recommended. Operating with the buffer disabled will be referred to as the N mode operation.<br>An 1872A/75A is placed in N mode via a hardware switch located on the bottom edge of the board and labeled "S1". The switch positions for N and F mode are labeled on the board.                                                                                                                                                                         |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER<br>ORGANIZATION    | The rest of this chapter discusses the recommended initial checkout procedures which should be made with the 1872A/75A module in N mode unless otherwise specified. This is followed by a description of Control and Status Register, CSR0, and the output data word bit definitions. The N mode readout scheme is the simplest to implement and therefore is discussed next. Those features of the 1872A/75A which are peculiar to the F mode are then described including operation of the internal buffer, the SS (Slave Status) codes, and the CIP (Conversion in Progress) signal and WAIT assertion capability. Following this background information, some of the possible F mode readout schemes are then discussed. This chapter concludes with a number of sections on other useful features of the 1872A/75A. |

| INITIAL CHECKOUT           | In this section, detailed recipes are given which should help the user begin to use<br>the 1872A/75A in a FASTBUS system. These include reading the module<br>identification (ID) and mode, internally starting and reading the module (no signal<br>inputs), a discussion of the on-board test pulser mode and a checkout procedure<br>with the LeCroy Model 1810 CAT module. Details on the various bit assignments<br>of CSR0 and the output data word are covered in a later section.                                                                                                                                                                                                                                                                                                                                |

|                            | Use of these recipes assumes a working knowledge of the FASTBUS standard.<br>For those users not intimately familiar with FASTBUS, the LIFT software package<br>provides keystroke macros to execute all primitive FASTBUS operations (see<br>Section 3, <i>Installation</i> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Read the Module ID         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and Mode                   | 1. Assure the 1872A/75A is in N mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                            | <ol> <li>Install the TDC module according to instructions in the <i>Installation</i> section<br/>(Section 3).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                   |

|                            | 3. Front-panel signal connections are not required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                            | 4. Power up crate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                            | 5. Address the module in CSR space (CSR0 now addressed).                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                            | <ol> <li>Assure the module is completely Reset. Internally CLEAR module - write<br/>0800 0000 (hex), wait 950 nsec, then Reset module - write 4000 0000 (hex).</li> </ol>                                                                                                                                                                                                                                                                                                                                                  |

|                            | 7. Read the module (fetching the value of CSR0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                            | <ol> <li>The 32-bit value read should be 1036 0200 (hex) if the module is an 1872A<br/>and 1037 3200 (hex) if the module is an 1875A.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                           |

|                            | <ol> <li>To determine if indeed the module is in N mode by internally STARTing the<br/>module (once) - write 0000 0800 (hex).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                   |

|                            | 10. Prepare to read CSR1 by doing a secondary address write with a value 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                            | <ol> <li>Read the module (CSR1). If the module is in N mode, the value read should<br/>be 4000 000 (hex). In F mode, the value would be 4000 0100 (hex). (The<br/>extra bit set in F mode corresponds to the value of the conversion event<br/>counter. See F mode operation page 4-15.)</li> </ol>                                                                                                                                                                                                                        |

|                            | If the above instructions are not understandable, then you should obtain<br>additional information on the operation of FASTBUS systems. Failure to read out<br>the indicated values upon power-up indicates a serious module or FASTBUS<br>system problem. Since all FASTBUS operations discussed in the following<br>sections are based on proper operation of FASTBUS and, in particular, the<br>proper manipulation of CSR0 information, you should not proceed until the above<br>procedure is completed successfully. |

| Internal Test Pulsing and  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Readout (no signal inputs) | 1. Assure the 1872A/75A is in N mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                            | 2. Remove side cover; remove P55 jumper to disable sparsification.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                            | <ol> <li>Install the TDC module according to instructions in the <i>Installation</i> section<br/>(Section 3).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                   |

|                            | 4. Front-Panel start signals should not be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                            | 5. Power up crate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                            | 6. Address module in CSR space. (CSR0 now addressed.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                            | <ol> <li>Assure the module is completely Reset. Internally CLEAR module - write<br/>0800 0000 (hex), wait 950 nsec, then Reset the module - write 4000 0000<br/>(hex).</li> </ol>                                                                                                                                                                                                                                                                                                                                          |

- 8. Cause a COM to occur by writing to the module (CSR0) 0000 0800 (hex). This causes a Start to be internally generated and the current front-panel inputs digitized. With the front-panel signals disconnected, this should provide a measure of the individual channel pedestals.

- 9. Assure that the Master waits 180  $\mu$ sec (170  $\mu$ sec plus the set MPI; see Section 3) for digitization to complete. The factory setting for the MPI is 10  $\mu$ sec.

- 10. Address the module in data space.

- 11. Read the module 64 times fetching the output of digitization process. For example, for a 1872A/75A module located in slot (Geographical address) 17, the first five 32-bit data words in hexadecimal format should be of the form:

- 8800 0000

8801 0000

8802 0000

8803 0000

8804 0000

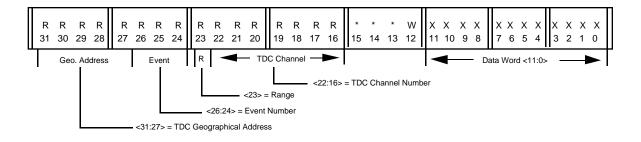

Bits <22:16> contain the TDC channel number. Bit <23> contains the digitization range. Bits <26:24> contain the event number (always zero in N mode). Bits <31:27> contain the geographic address of the module, which in this case for a value of 17 (decimal) results in value of 88 (hex) in the top byte of the output data word (bits 31 and 27 set). (See Output Data Word page 4-9.)

12. After 64 reads, the user can verify that a 65th read operation generates a Slave Status code, SS = 2 response, which indicates all valid data channels have been read out.

- 13. Remove module from the crate, replace P55 jumper to enable sparsification and replace side cover.

# Using the Test PulserThe 1872A/75A TDC modules have a voltage programmable test pulser. The test<br/>pulser is to be used to generate a common start pulse and a stop for each<br/>channel. The intended purpose of this pulser is to provide a quick self-check of<br/>the TDC channels and to enable a $\pm 3\%$ channel-to-channel and module-to-<br/>module calibration.

The test pulser is enabled for operation by setting CSR0<10>.

When the test pulser is enabled, a COM pulse from either the front panel, TR5, or CSR0<11> will generate an internal START and STOP for every channel according to a programming voltage. A jumper connector, P1, provides three programming sensitivities for the test pulser: 80, 160, or 320 nsec/V. A second jumper, P57, determines the test pulser's range: open = low, and shorted = high range. The tester setting is summarized in the following tables:

|                | Jumper P1 Settings |          |          |

|----------------|--------------------|----------|----------|

| TDC Resolution | 25 ps              | 50 ps    | 100 ps   |

| Low Range      | 10 ns/V            | 20 ns/V  | 40 ns/V  |

| High Range     | 80 ns/V            | 160 ns/V | 320 ns/V |

#### Sensitivity Adjustments

| Range | Adjustments |

|-------|-------------|

|-------|-------------|

| Tester Range | Jumper P57 Settings      |

|--------------|--------------------------|

| Low          | Open (jumper removed)    |

| High         | Shorted (jumper applied) |

Jumpers P57 and P1 are located at the top left corner of the TDC board.

The programming voltage should be applied to the module on the two unterminated restricted lines on the FASTBUS backplane UR0, and UR1. The test voltage inputs are high impedance, fully differential with large common mode rejection for at least a 2 V maximum common mode signal.

POSITIVE INPUT - UR1, PIN B56 usually positive.

NEGATIVE INPUT - UR0 PIN B55 usually ground reference.

Maximum voltage input is 10 V.

For bench testing this module, a 2-pin input header P2, is available under the side panel to which the user may apply the test voltage. The header is near the rear top of the module and the pin towards the back is the more positive.

Checkout Using the Test Pulser and the LeCroy Model 1810 CAT (Calibration & Timing Module)

In this section a detailed prescription is presented for using the LeCroy Model 1810 CAT to apply a test voltage to the backplane UR lines, and with the test pulser enabled apply an internal strobe to the TDC for test purposes. This procedure uses a number of the features of the TDC and CAT which make it a good tutorial on the operation of both. The 1810 has a 12-bit DAC and amplifier to allow the user to digitally program the voltage from any FASTBUS Master. With a 12-bit DAC, one should not expect the CAT to serve as a good calibration device for the 15-bit dynamic range of an 1875A TDC. Further, since the Test Pulser is intended only for testing, the Common START and STOPs which are generated have greater jitter than the measurement capabilities of the 1872A/75A.

- 1. Assure the jumpers are in the desired position.

- 2. Install the TDC module according to instructions in Section 3, Installation.

- 3. Install 1810 CAT module in a FASTBUS crate.

- 4. Front panel HIT signals should not be connected.

- 5. Power up crate.

- 6. Confirm that the CAT is addressable. Address the CAT module in CSR space. Read the module (CSR0 ID) should be 1039 0000 (hex).

- 7. Address the TDC module in CSR space.

- 8. Assure the TDC module is completely Reset. Internally Clear the module write 0800 0000 (hex), wait 950 nsec, then Reset the module write 4000 0000 (hex).

- 9. Enable the TDC module test pulser write 0000 0400 (hex).

- 10. Address the CAT module in data space.

- 11. Set the CAT module data space NTA (Next Transfer Address) to 3, using a secondary address write: DS(u), MS=2, AD=3.

- 12. Write the desired Voltage to place on UR lines. 12-bits (4095) is 10 V full scale. When the TDC test pulser is enabled, 1 V will generate a common START and STOP separated as programmed on UR1 and UR0. To set the CAT to 1.0 V, write 0000 019A (hex) which is 410 (dec).

- 13. Address the 1872A/75A in CSR space.

- 14. Cause an Internal Test cycle to occur by writing to the module (CSR0) 0000 0800 (hex). This causes the internal common START and STOP test pulses.

- Assure that the Master waits at least 180 μsec (10 μsec of MPI + 170 μsec of TDC conversion time).

- 16. Address the module in data space.

- Read the module 64 times fetching the output digitization process. For example, for an 1872A/75A module located in slot (geographical address) 17, the first five 32-bit data words in hexadecimal format should be of the form:

8800 0XXX

8801 0XXX

8802 0XXX

8803 0XXX

8804 0XXX

This format is discussed later in the Output Data Word section, page 4-9. Here XXX is the TDC value which includes the time interval from the test pulser added to the channel pedestal.

- After 64 reads, the user can verify that a 65th read operation generates a Slave Status, SS = 2 response, which indicates all valid data channels have been read out.

- 19. Repeat for different CAT voltages as desired beginning with step 10.

Note: The test pulser is the same in both the 1872A and the 1875A. The 1875A test circuitry has no knowledge of whether auto range is enabled or disabled. The tester does not automatically compensate according to the resolution selected for the board. The user must take care to ensure that the programmed voltage from the CAT (on UR1 & UR0), the jumpers controlling the on-board tester, and the board's resolution are all properly selected.

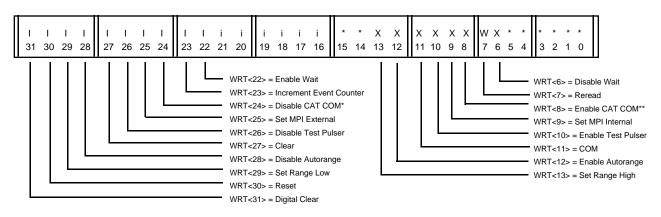

#### **CSR0 WRITE**

**Bit Type Definitions**

- I bits which give module ID upon read, but are also implemented for write operations.

- i bits which give module ID upon read and are not used for write operations.

- \* unused bits which read back zero.

- **R** bits implemented for read operations only.

- W bits implemented for write operations only.

- **X** bits implemented for read and write operations.

- **T** factory reserved; not for read or write operations; ignore value.

\* (and Enable front panel COM)

\*\* (and Disable front panel COM)

| Control Bits | The 2-state control bits are set and reset by writing to different bits in CSR0. This strategy is described in the FASTBUS specification. Briefly, the state of the bit is set by writing a "1" to a specified bit in CSR0 and is reset by writing a "1" to a different bit CSR0. This is to allow the user to set or reset a control bit without having to remember the state of the other bits in the register. If a "0" is written to both bits associated with the control bit then no change will occur, if a "1" is written to both bits the results are undefined. |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | <b>Wait (enable/disable):</b> Allows/disallows the assertion of the WAIT signal. If enabled an 1872A/75A will assert WAIT when addressed in data space and the unit is NOT converting data. (See Conversion in Progress (CIP) and WAIT, page 4-16.)                                                                                                                                                                                                                                                                                                                       |

|              | <b>MPI (set external/internal):</b> Selects internal or backplane as source for Measure Pause Interval (See Section 3).                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              | <b>Test Pulser (enable/disable):</b> Enables/disables internal test pulser for use with Internal COM as a calibration mode (See Using the Test Pulser, page 4-3.)                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | <b>Autorange (enable/disable):</b> Enables/disables autoranging, applies only to 1875As. Overrides the range selected via Range.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              | <b>Range (high/low):</b> Selects range only if autoranging is disabled (applies only to 1875As).                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              | <b>CAT COM (enable/disable):</b> Enables/disables COM by LeCroy 1810 CAT module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Pulsed Bits  | Pulsed bits initiate an action in the unit whenever a "1" is written to the appropriate bit. All but the internal COM are "write only"; the action occurs entirely within the write cycle. The internal COM is long enough that a fast Master may be able to discern its duration. It has a position in CSR0 that will read a "1" for its duration.                                                                                                                                                                                                                       |

|              | <b>Reread:</b> Resets FIFO (FASTBUS side) to Channel 0. Does not affect event counters or TDC circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              | Internal COM: Causes unit to generate its own COM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|              | <b>Increment Event Counter:</b> Advance the Readout Event Counter to next event and reset the Data memory pointer (FIFO) to the beginning of that event (F-Mode only).                                                                                                                                                                                                                                                                                                                                                                                                    |

|              | <b>Clear:</b> This bit has the same function as a hardware front-panel clear which clears the analog front end of the module.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | <b>Reset:</b> Resets the 1872A/75A to a state identical with the power-up condition. Specifically, it resets CSR0 back to its default power-up condition, sets the number of active channels to 64, resets data memory (FIFO) pointer to beginning of event, and marks data as invalid.                                                                                                                                                                                                                                                                                   |

|              | <b>Digital Clear:</b> Resets data acquisition associated controls, but leaves the setup parameters alone. Specifically, it resets event counters, resets data memory (FIFO) pointer to beginning of event, marks data as invalid and issues CLEAR (see above).                                                                                                                                                                                                                                                                                                            |

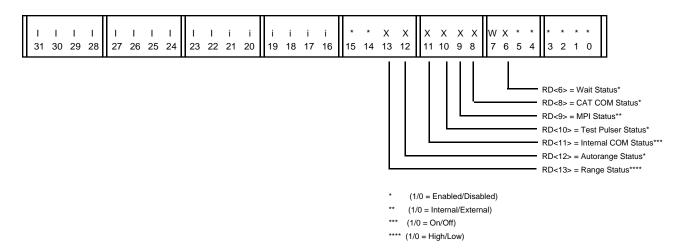

#### CONTROL AND STATUS REGISTER, CSR0 READ

CSR0 After Rest or Power-up 1872A 1036 0200 1875A 1037 3200

\* front panel input status is the complement of the CAT status.

#### **OUTPUT DATA WORD**

**Data Word:** The digitized time interval which may range between 0 and 4095. The pedestal should be less than 15% of full scale for a particular range.

TDC Channel Number: Channels are numbered 0 to 63.

**Range:** A single bit which denotes the range used to digitize the current integral for that channel and event (1 = High Range).

**Event Number:** The value of a circular 3-bit counter indicating the location in the module's internal data buffer from which data was read. This value is useful only in readout schemes which use the internal buffering feature of the module.

**TDC Geographical Address:** The physical slot number of the FASTBUS crate in which the module is located.

#### N MODE OPERATION

#### N Mode

Both the N and F mode operation of the 1872A/75A are identical to the 1882/85F modes. The N mode is provided just as in the 1882/85F ADCs to aid compatibility with the older 1880N ADCs. This compatibility extends only so far as acquiring data and reading the 1872A/75A. Certain features of the 1880N, such as generating an invalid response when addressing CSR1 are not implemented.

Particular points to consider include:

- 1. If the user's software depends on the module ID number to locate units, it will have to be updated to allow for the new ID number.

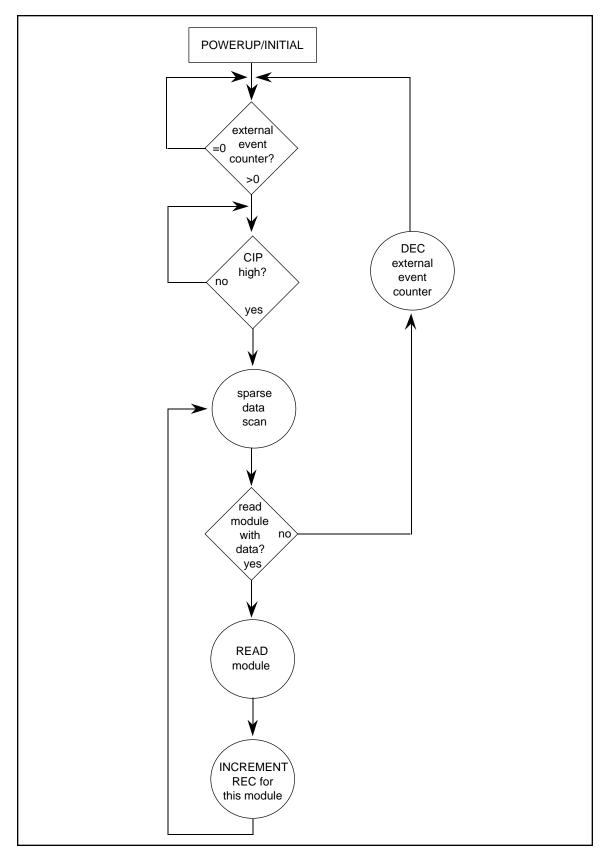

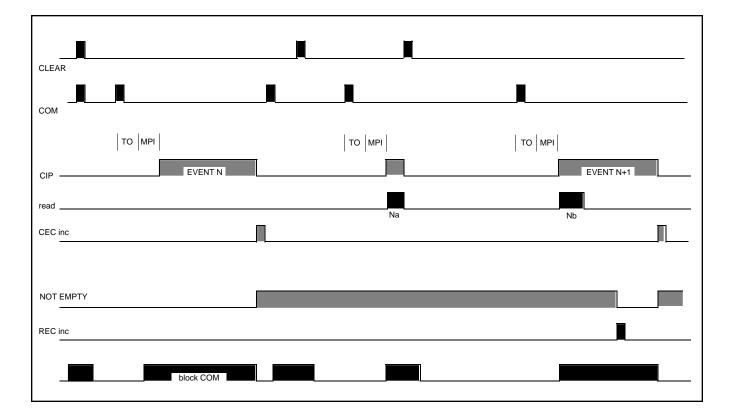

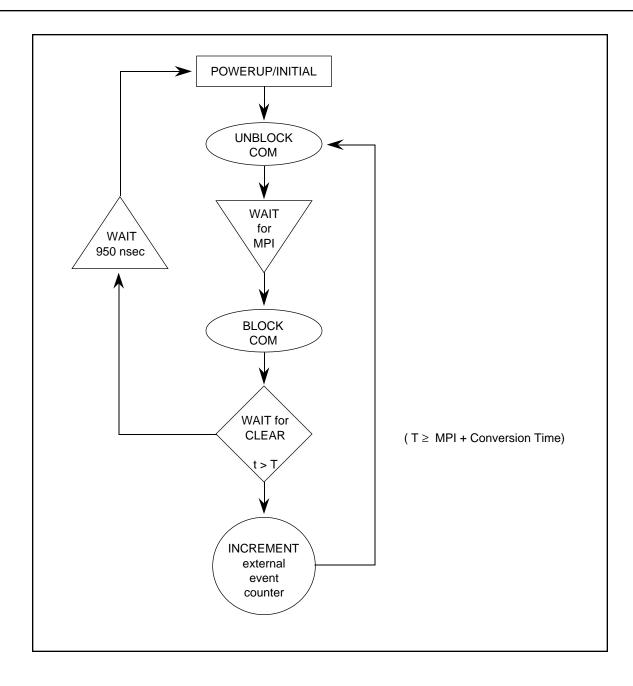

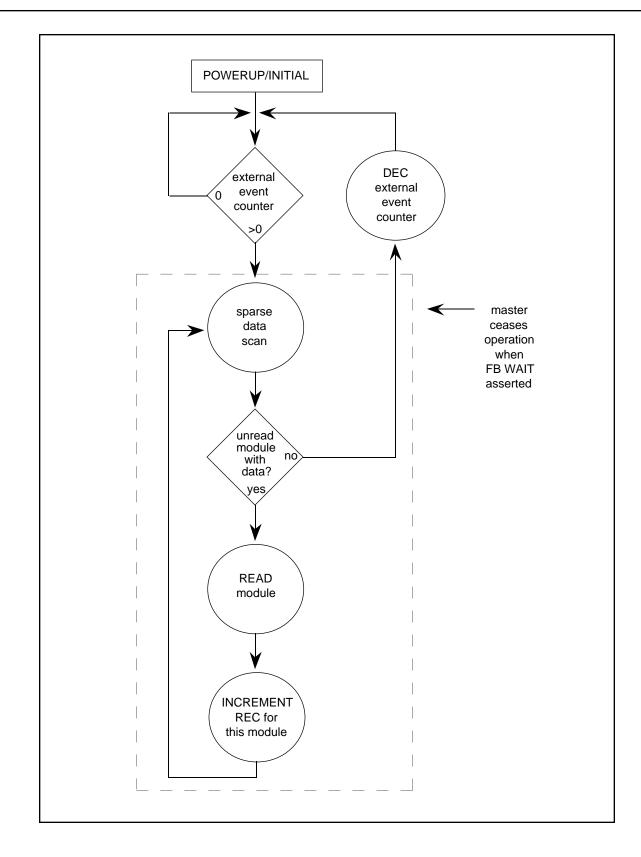

- 2. To assure complete initialization after power-up, the 1872A/75A should be internally CLEARed, and RESET. This should be done once after the crate has been turned on.