## **OPERATOR'S MANUAL**

## **MODEL 3304**

### FERA SYSTEM MANAGER

PRELIMINARY

#### **Corporate Headquarters**

700 Chestnut Ridge Road Chestnut Ridge, NY 10977-6499 Tel: (914) 578-6013 Fax: (914) 578-5984

#### **European Headquarters**

2, rue du Pre-de-la-Fontaine P.O. Box 341 CH-1217 Meyrin 1 Geneva Switzerland Tel: (022) 719 2228 Fax: (022) 719 2230

Copyright© July 1995. LeCroy™ is a registered trademark of LeCroy Corporation. All rights reserved. Information in this publication supersedes all earlier versions.

# TABLE OF CONTENTS

| 1. | General Information               |    |

|----|-----------------------------------|----|

|    | Purpose                           | 5  |

|    | Unpacking & Inspection            | 5  |

|    | Warranty                          | 5  |

|    | Product Assistance                | 5  |

|    | Maintenance Agreements            | 5  |

|    | Documentation Discrepancies       | 6  |

|    | Software Licensing Agreement      | 6  |

|    | Service Procedure                 | 6  |

| 2. | Operating Instruction             |    |

|    | General                           | 7  |

|    | Gate Management                   | 8  |

|    | Counting Rates                    | 8  |

|    | FERA Clear                        | 8  |

|    | Readout Delay                     | 8  |

|    | System Integration                |    |

|    | Cabling                           | 10 |

|    | Signal Description                | 11 |

|    | LED Indicators                    | 12 |

|    | CAMAC Commands and Function Codes | 12 |

# **GENERAL INFORMATION**

| PURPOSE                     | This manual is intended to provide instruction regarding the setup and operation of the covered instruments. In addition, it describes the theory of operation and presents other information regarding its functioning and application.                                                                                                                                                                                                                                                                                                                  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UNPACKING AND<br>INSPECTION | It is recommended that the shipment be thoroughly inspected immedi-<br>ately upon delivery. All material in the container should be checked<br>against the enclosed Packing List and shortages reported promptly.<br>If the shipment is damaged in any way, please notify the Customer<br>Service Department or the local field service office. If the damage is<br>due to mishandling during shipment, you may be requested to assist in<br>contacting the carrier in filing a damage claim.                                                             |

| WARRANTY                    | LeCroy warrants its instrument products to operate within specifications<br>under normal use and service for a period of one year from the date of<br>shipment. Component products, replacement parts, and repairs are<br>warranted for 90 days. This warranty extends only to the original pur-<br>chaser. Software is thoroughly tested, but is supplied "as is" with no<br>warranty of any kind covering detailed performance. Accessory products<br>not manufactured by LeCroy are covered by the original equipment<br>manufacturers' warranty only. |

|                             | In exercising this warranty, LeCroy will repair or, at its option, replace any product returned to the Customer Service Department or an authorized service facility within the warranty period, provided that the warrantor's examination discloses that the product is defective due to workmanship or materials and has not been caused by misuse, neglect, accident or abnormal conditions or operations.                                                                                                                                             |

|                             | The purchaser is responsible for the transportation and insurance charges arising from the return of products to the servicing facility. LeCroy will return all in-warranty products with transportation prepaid.                                                                                                                                                                                                                                                                                                                                         |

|                             | This warranty is in lieu of all other warranties, express or implied, includ-<br>ing but not limited to any implied warranty of merchantability, fitness, or<br>adequacy for any particular purpose or use. LeCroy shall not be liable<br>for any special, incidental, or consequential damages, whether in con-<br>tract, or otherwise.                                                                                                                                                                                                                  |

| PRODUCT ASSISTANCE          | Answers to questions concerning installation, calibration, and use of LeCroy equipment are available from the Customer Service Department, 700 Chestnut Ridge Road, Chestnut Ridge, New York, 10977-6499, (914) 578-6030.                                                                                                                                                                                                                                                                                                                                 |

| MAINTENANCE<br>AGREEMENTS   | LeCroy offers a selection of customer support services. For example,<br>Maintenance Agreements provide extended warranty that allows the<br>customer to budget maintenance costs after the initial warranty has<br>expired. Other services such as installation, training, on-site repair, and<br>addition of engineering improvements are available through specific<br>Supplemental Support Agreements. Please contact the Customer<br>Service Department for more information.                                                                         |

| DOCUMENTATION<br>DISCREPANCIES  | LeCroy is committed to providing state-of-the-art instrumentation and is<br>continually refining and improving the performance of its products. While<br>physical modifications can be implemented quite rapidly, the corrected<br>documentation frequently requires more time to produce. Consequently,<br>this manual may not agree in every detail with the accompanying product<br>and the schematics in the Service Documentation. There may be small<br>discrepancies in the values of components for the purposes of pulse<br>shape, timing, offset, etc., and, occasionally, minor logic changes.<br>Where any such inconsistencies exist, please be assured that the unit is<br>correct and incorporates the most up-to-date circuitry.                                                                                                                                                                                                                                                  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOFTWARE LICENSING<br>AGREEMENT | Software products are licensed for a single machine. Under this license you may:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                 | Copy the software for backup or modification purposes in support of<br>your use of the software on a single machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                 | Modify the software and/or merge it into another program for your use on a single machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                 | Transfer the software and the license to another party if the other<br>party accepts the terms of this agreement and you relinquish all<br>copies, whether in printed or machine readable form, including all<br>modified or merged versions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SERVICE PROCEDURE               | Products requiring maintenance should be returned to the Customer<br>Service Department or authorized service facility. If under warranty,<br>LeCroy will repair or replace the product at no charge. The purchaser is<br>only responsible for the transportation charges arising from return of the<br>goods to the service facility. For all LeCroy products in need of repair<br>after the warranty period, the customer must provide a Purchase Order<br>Number before any inoperative equipment can be repaired or replaced.<br>The customer will be billed for the parts and labor for the repair as well<br>as for shipping. All products returned for repair should be identified by<br>the model and serial numbers and include a description of the defect or<br>failure, name and phone number of the user. In the case of products<br>returned, a Return Authorization Number is required and may be<br>obtained by contacting the Customer Service Department at (914) 578-<br>6030. |

### **OPERATING INSTRUCTIONS**

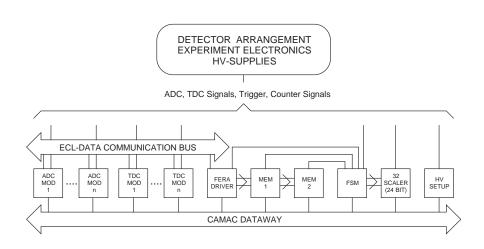

| GENERAL |    | RA™ is a data acquisition sy<br>nsists of the following module                                                       | stem for medium sized experiments. It                                                                                                                          |

|---------|----|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |    | Model 4300B<br>Model 4303+4300B                                                                                      | ADC (charge)<br>TDC                                                                                                                                            |

|         |    | Model 4301                                                                                                           | Driver                                                                                                                                                         |

|         |    | Model 4302                                                                                                           | Memory                                                                                                                                                         |

|         |    | Model 3304                                                                                                           | System Manager                                                                                                                                                 |

|         |    | detailed description of the sys<br>n Note AN-4004A.                                                                  | tem architecture can be found in Applica-                                                                                                                      |

|         |    | System Manager (FSM) provides all<br>automatic operation of the FERA system.<br>Figure 1. In particular, it manages: |                                                                                                                                                                |

|         | 1. | The handling of Gate and S conversion and readout.                                                                   | tart signals by a Busy signal during                                                                                                                           |

|         | 2. |                                                                                                                      | n normal operation mode as well as after<br>erval to avoid hang-ups of the system.                                                                             |

|         | 3. | conversion and transfer tim<br>LeCroy Model 3341 Spectro                                                             | e ECLbus readout to allow different<br>es of FERA-compatible units (e.g.,<br>oscopy Grade Charge Integrating ADC,<br>Grade Peak Sensing ADC and Model<br>FDC). |

|         | 4. | The generation of 4 event reexperiment.                                                                              | ates to monitor and control the                                                                                                                                |

|         |    |                                                                                                                      |                                                                                                                                                                |

- 5. The hardware-driven, memory-switching mode with two memory modules, Model 4302, working alternately to minimize deadtime.

- 6. The event-by-event mode for memory readout after each event.

Figure 1

| Gate Management                                                                                                                                                                                                                                                                                                                                                      | In general, the experiment:                                                                                                                                                           | following signals have                                                                                                                                      | e to be supplied as inputs from the                                                                                                                       |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                      | Master Gate<br>Gate 1<br>Gate 2                                                                                                                                                       | (M-GATE INP)<br>(GATE1 INP)<br>(GATE2 INP)                                                                                                                  | start event cycle<br>Gate ADC or<br>Start TDC                                                                                                             |  |

| 1 and 2 and starts the timeout coun                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                       |                                                                                                                                                             | r Gate signal enables the inputs Gate<br>er. An incoming Gate signal is fed<br>and at the same time, the Gate input                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                       | hat a minimum delay<br>ate and Gate 1 or 2.                                                                                                                 | of 40 nsec is required between                                                                                                                            |  |

|                                                                                                                                                                                                                                                                                                                                                                      | The inhibit of the gate inputs is removed when an ECLbus data transfer is completed or when a timeout occurred. Only then a new cycle can be started via the Master Gate input.       |                                                                                                                                                             |                                                                                                                                                           |  |

| Counting Rates                                                                                                                                                                                                                                                                                                                                                       | From the Gate signal management, the following information is derived to generate different counting rates:                                                                           |                                                                                                                                                             |                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                      | <b>Total Events (TEV):</b> total number of events offered by the experiment (corresponds to number of Master Gate signals).                                                           |                                                                                                                                                             |                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                      | <b>Accepted Events (AEV):</b> number of registered events with competed ECLbus transfer (number of PASS signals).                                                                     |                                                                                                                                                             |                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                      | <b>Rejected Events (REV):</b> number of events during module BUSY, i.e.,<br>Gate inputs Inhibit (from Master Gate to data transfer completed or<br>during overflow of both memories). |                                                                                                                                                             |                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                      | <b>Timeout Detected (TIO):</b> number of Clear signals generated by the FSM after timeouts.                                                                                           |                                                                                                                                                             |                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                      | •                                                                                                                                                                                     | end of a measureme                                                                                                                                          | LeCroy Model 4434 Scaler and be<br>nt run for statistical and normaliza-                                                                                  |  |

| FERA Clear                                                                                                                                                                                                                                                                                                                                                           | signal of the la<br>(PAI input). Ad<br>PASS does no                                                                                                                                   | st ADC, which reports ditionally, the FSM itse                                                                                                              | iated in Buffer mode by the PASS<br>data transfer complete to the FSM<br>elf produces a Clear signal, if a<br>grammed timeout interval. Therefore,<br>ed. |  |

|                                                                                                                                                                                                                                                                                                                                                                      | Following conversion and/or zero suppression times, there is a fixed delay of 2 $\mu sec$ between system Clear and remove Inhibit of the FSM Gate inputs.                             |                                                                                                                                                             |                                                                                                                                                           |  |

| <b>Readout Delay</b> The ECL-commandbus signal REQ reports that data are ready for ECL port readout. This signal is the logical OR ADC requests; timing differences are compensated by a the Driver Model 4301, which can be manually adjusted 500 nsec. This interval may not be sufficient if additional ible units from other manufacturers with considerably lor |                                                                                                                                                                                       | nal is the logical OR of the individual<br>e compensated by a delay interval in<br>e manually adjusted between 150-<br>ufficient if additional FERA compat- |                                                                                                                                                           |  |

|                          | times, are added to the system (e.g., LeCroy Model 3351 with up to 25 $\mu sec).$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | To handle this configuration, it is possible to delay the Readout Request signal in the FSM, in programmable steps of 100 nsec. Only after this period does the RQO signal from the FSM to the first ADC start the transfer of the data via ECLbus.                                                                                                                                                                                                                                                                                                                                                                                        |

| Memory Switching<br>Mode | By using the Overflow and Veto signals of two memories Model 4302, the FSM completely controls a hardware driven automatic and continuous double buffer operation. In this mode, data are written into one memory, while the other is read out via CAMAC block transfer or is ready to take data. No software control is necessary, thus dead time is minimized. The selection and switching of the memories is organized by bits 1, 2, and 3 of the status register. A further 2 bits only readable, indicate the memory, which is currently active. The LAM on Overflow finally allows data readout without any special software effort. |

|                          | At high data rates, both memories may report an overflow, because<br>CAMAC readout of one unit has not yet completed, whereas the second<br>one has already filled again with data. In such a case, the FSM internally<br>generates a Memory Full signal and inhibits the Gate 1 and 2 inputs, until<br>one memory becomes available again.                                                                                                                                                                                                                                                                                                |

|                          | In cases where FERA is part of a more complex data acquisition system,<br>which has to be read out after each event, it is possible to switch on the<br>event-by-event mode by setting status register bit 6 equal to 1.                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### SYSTEM INTEGRATION

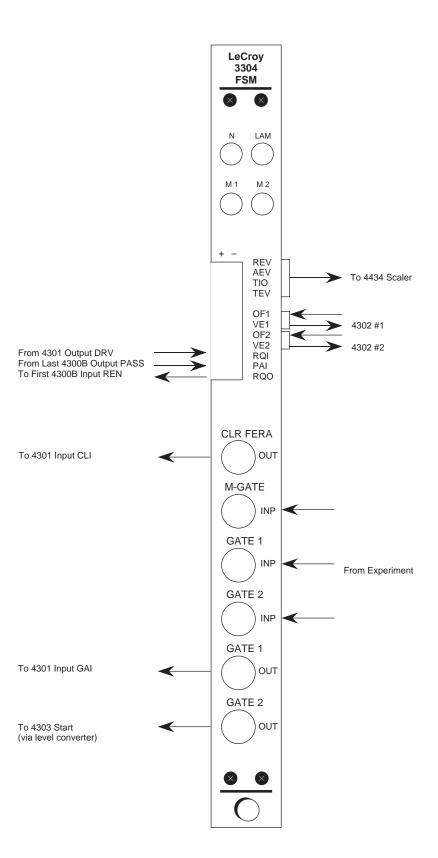

Cabling

| Signal Description | <b>Master Gate (M-GATE):</b> Input, Lemo type connector accepting NIM signals (50 Ohm). Typically Master Trigger from the experiment.     |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|                    | <b>Gate 1 (GATE1 INP):</b> Input, Lemo type connector accepting NIM signal (50 Ohm), e.g., ADC gate input.                                |

|                    | <b>Gate 2 (GATE2 INP):</b> Input, Lemo type connector accepting NIM signals (50 Ohm), e.g., TDC start input.                              |

|                    | <b>Gate 1 (GATE1 OUT):</b> Output, Lemo type connector; produces NIM signals, e.g., gate for 4300B.                                       |

|                    | <b>Gate 2 (GATE2 OUT):</b> Output, Lemo type connector; produces NIM signals, e.g., gate for 4303.                                        |

|                    | <b>Clear (CLR FERA):</b> Output, Lemo type connector; produces NIM signals. Connect to CLI input of 4301.                                 |

|                    | <b>Readout Request Input (RQI):</b> Input, 2-pin connector accepting diff. ECL signals (100 Ohms). Connect to REQ output of 4301.         |

|                    | <b>Pass Input (PAI):</b> Input, 2 pin connector accepting diff. ECL signals (100 Ohms). Connect to PASS output of last 4300B.             |

|                    | <b>Readout Request Output (RQO):</b> Output, 2-pin connector accepting diff. ECL signals (100 Ohms). Connect to REN input of first 4300B. |

|                    | <b>Overflow Memory #1 (OF1):</b> Input, 2-pin connector accepting diff. ECL signals (100 Ohm). Connect to OVF output of 4302 #1.          |

|                    | <b>Overflow Memory #2 (OF2):</b> Input, 2-pin connector accepting diff. ECL signals (100 Ohm). Connect to OVF output of 4302 #2.          |

|                    | <b>Veto Memory #1 (VE1):</b> Output, 2-pin connector producing diff. ECL signals (100 Ohm). Connect to VETO input of 4302 #1.             |

|                    | <b>Veto Memory #2 (VE2):</b> Output, 2-pin connector producing diff. ECL signals (100 Ohm). Connect to VETO input of 4302 #2.             |

|                    | <b>Total Events (TEV):</b> Output, 2-pin connector producing diff. ECL signals (100 Ohm). Connect to 4434 input.                          |

|                    | <b>Accepted Events (AEV):</b> Output, 2-pin connector producing diff. ECL signals (100 Ohm). Connect to 4434 input.                       |

|                    | <b>Rejected Events (REV):</b> Output, 2-pin connector producing diff. ECL signals (100 Ohm). Connect to 4434 input.                       |

|                    | <b>Timeout Detected (TIO):</b> Output, 2-pin connector producing diff. ECL signals (100 Ohm). Connect to 4434 input.                      |

| LED Indicators                       | N: Module addressed.  |                                                                                                                                              |  |

|--------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                      | LAM: LAM from         | Memory #1 or #2 (if enabled).                                                                                                                |  |

|                                      | M1: Memory #1 active. |                                                                                                                                              |  |

|                                      | M2: Memory #2 active. |                                                                                                                                              |  |

| CAMAC COMMANDS<br>AND FUNCTION CODES | F(0)•A(0):            | Read Status Register; X=1, Q=1.                                                                                                              |  |

|                                      |                       | R1 - acquisition started<br>R2 - memory #1 ready<br>R3 - memory #2 ready                                                                     |  |

|                                      |                       | R4 - memory #1 active                                                                                                                        |  |

|                                      |                       | R5 - memory #2 active<br>R6 - single event mode on, off                                                                                      |  |

|                                      | F(16)•A(0):           | Write Status Register; X=1, Q=1.<br>W1 - start acquisition, enable memory #1, free<br>master gate                                            |  |

|                                      |                       | W2 - set memory #1 ready<br>W3 - set memory #2 ready                                                                                         |  |

|                                      |                       | W6 - enable single event mode                                                                                                                |  |

|                                      | F(16)•A(1):           | Set Timeout-Counter; X=1, Q=1. W1W16<br>(timeout=value*100 nsec).                                                                            |  |

|                                      | F(16)•A(2):           | Set Readout-Delay-Counter; X=1, Q=1. W1W16<br>(delay=value*100 nsec).                                                                        |  |

|                                      | F(8)•A(0):            | Test LAM #1; X=1, Q=1 if L=1.                                                                                                                |  |

|                                      | F(8)•A(1):            | Test LAM #2; X=1, Q=1 if L=1.                                                                                                                |  |

|                                      | F(10)•A(0):           | Test and Clear LAM #1; X=1, Q=1 if L=1.                                                                                                      |  |

|                                      | F(10)•A(1):           | Test and Clear LAM #2; X=1, Q=1 if L=1.                                                                                                      |  |

|                                      | F(24)•A(0):           | Disable LAM; X=1, Q=1.                                                                                                                       |  |

|                                      | F(26)•A(0):           | Enable LAM; X=1, Q=1.                                                                                                                        |  |

|                                      | F(9)•A(0):            | Reset Module; X=1, Q=1.<br>- memory #1, #2 ready<br>- acquisition stop<br>- single event mode off<br>- clear LAM #1, LAM #2<br>- disable LAM |  |

|                                      | l:                    | Inhibit Acquisition                                                                                                                          |  |

|                                      | C or Z:               | Reset Module.                                                                                                                                |  |

|                                      | L:                    | Buffer Mode: on overflow of memory #1 or #2. Single event mode: following each ECL port readout.                                             |  |