## **OPERATOR'S MANUAL**

# MODEL 3371 CAMAC 8-INPUT TDC

#### **Corporate Headquarters**

700 Chestnut Ridge Road Chestnut Ridge, NY 10977-6499

Tel: (914) 578-6013 Fax: (914) 578-5984

E-mail: lrs\_support@lecroy.com WWW: http://www.lecroy.com

#### **European Headquarters**

27 Blacklands Way Abingdon Business Park Abingdon Oxon OX14 1DY United Kingdom

Tel: (1235) 533114 Fax: (1235) 528796

E-mail: lrs\_europe@lecroy.com

## **CAUTION**

**POWER**

**REQUIREMENTS** The Model 3371 requires both +12 V and -12 V in addition to +6 V, -6 V,

+24 V and -24 V supplies for proper operation.

**SPECIFICATIONS** The information contained in this manual is subject to change without

notice. The reference for product specification is the Technical Data

Sheet effective at the time of purchase.

## TABLE OF CONTENTS

|    | 1.  | General Information Purpose Unpacking & Inspection Warranty Product Assistance Maintenance Agreements Documentation Discrepancies | 7<br>7<br>7<br>7<br>7<br>8<br>8 |

|----|-----|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|    |     | Software Licensing Agreement<br>Service Procedure                                                                                 | 8                               |

|    | 2.  | Operating Instructions                                                                                                            |                                 |

|    |     | General                                                                                                                           | 9                               |

|    |     | Analog Inputs (STOPS)                                                                                                             | 10                              |

|    |     | CLEAR Function                                                                                                                    | 10                              |

|    |     | External START Input                                                                                                              | 10                              |

|    |     | ADC Thresholds and Offset Memory                                                                                                  | 10                              |

|    |     | Test Function                                                                                                                     | 12                              |

|    |     | Overflow                                                                                                                          | 12                              |

|    |     | Status Register                                                                                                                   | 12                              |

|    |     | ECL Data Bus                                                                                                                      | 13                              |

|    |     | ECL BUS - REN/Pass                                                                                                                | 14                              |

|    |     | ECL Port Enable/Pass                                                                                                              | 15                              |

|    |     | ECL Bus Readout Interrupt                                                                                                         | 16                              |

|    |     | ECL Data Structures                                                                                                               | 16                              |

|    |     | CAMAC Commands and Functions                                                                                                      | 17                              |

|    |     | CAMAC Readout                                                                                                                     | 19                              |

|    |     | LAM Handling                                                                                                                      | 19                              |

|    |     | CAMAC Data Structures                                                                                                             | 20                              |

|    |     | Readout Timing Diagram                                                                                                            | 21                              |

| 3. | Tec | hnical Information                                                                                                                |                                 |

|    |     | General                                                                                                                           | 25                              |

|    |     | Description                                                                                                                       | 25                              |

|    |     | Analog Inputs Impedance                                                                                                           | 26                              |

#### **GENERAL INFORMATION**

#### **PURPOSE**

This manual is intended to provide instruction regarding the setup and operation of the covered instruments. In addition, it describes the theory of operation and presents other information regarding its functioning and application.

## UNPACKING AND INSPECTION

It is recommended that the shipment be thoroughly inspected immediately upon delivery. All material in the container should be checked against the enclosed Packing List and shortages reported promptly. If the shipment is damaged in any way, please notify the Customer Service Department or the local field service office. If the damage is due to mishandling during shipment, you may be requested to assist in contacting the carrier in filing a damage claim.

#### WARRANTY

LeCroy warrants its instrument products to operate within specifications under normal use and service for a period of one year from the date of shipment. Component products, replacement parts, and repairs are warranted for 90 days. This warranty extends only to the original purchaser. Software is thoroughly tested, but is supplied "as is" with no warranty of any kind covering detailed performance. Accessory products not manufactured by LeCroy are covered by the original equipment manufacturers' warranty only.

In exercising this warranty, LeCroy will repair or, at its option, replace any product returned to the Customer Service Department or an authorized service facility within the warranty period, provided that the warrantor's examination discloses that the product is defective due to workmanship or materials and has not been caused by misuse, neglect, accident or abnormal conditions or operations.

The purchaser is responsible for the transportation and insurance charges arising from the return of products to the servicing facility. LeCroy will return all in-warranty products with transportation prepaid.

This warranty is in lieu of all other warranties, express or implied, including but not limited to any implied warranty of merchantability, fitness, or adequacy for any particular purpose or use. LeCroy shall not be liable for any special, incidental, or consequential damages, whether in contract, or otherwise.

#### **PRODUCT ASSISTANCE**

Answers to questions concerning installation, calibration, and use of LeCroy equipment are available from the Customer Service Department, 700 Chestnut Ridge Road, Chestnut Ridge, New York, 10977-6499, (914) 578-6030.

#### MAINTENANCE AGREEMENTS

LeCroy offers a selection of customer support services. For example, Maintenance Agreements provide extended warranty that allows the customer to budget maintenance costs after the initial warranty has expired. Other services such as installation, training, on-site repair, and addition of engineering improvements are available through specific Supplemental Support Agreements. Please contact the Customer Service Department for more information.

## DOCUMENTATION DISCREPANCIES

LeCroy is committed to providing state-of-the-art instrumentation and is continually refining and improving the performance of its products. While physical modifications can be implemented quite rapidly, the corrected documentation frequently requires more time to produce. Consequently, this manual may not agree in every detail with the accompanying product and the schematics in the Service Documentation. There may be small discrepancies in the values of components for the purposes of pulse shape, timing, offset, etc., and, occasionally, minor logic changes. Where any such inconsistencies exist, please be assured that the unit is correct and incorporates the most up-to-date circuitry.

## SOFTWARE LICENSING AGREEMENT

Software products are licensed for a single machine. Under this license you may:

- Copy the software for backup or modification purposes in support of your use of the software on a single machine.

- Modify the software and/or merge it into another program for your use on a single machine.

- Transfer the software and the license to another party if the other party accepts the terms of this agreement and you relinquish all copies, whether in printed or machine readable form, including all modified or merged versions.

#### **SERVICE PROCEDURE**

Products requiring maintenance should be returned to the Customer Service Department or authorized service facility. If under warranty, LeCroy will repair or replace the product at no charge. The purchaser is only responsible for the transportation charges arising from return of the goods to the service facility. For all LeCroy products in need of repair after the warranty period, the customer must provide a Purchase Order Number before any inoperative equipment can be repaired or replaced. The customer will be billed for the parts and labor for the repair as well as for shipping. All products returned for repair should be identified by the model and serial numbers and include a description of the defect or failure, name and phone number of the user. In the case of products returned, a Return Authorization Number is required and may be obtained by contacting the Customer Service Department at (914) 578-6030.

### **OPERATING INSTRUCTIONS**

#### **GENERAL**

The Model 3371 ADC incorporates 8 analog memories with common START and separate STOP signals. The analog memories outputs are routed, through an analog multiplexer, to a fast analog-to-digital converter (3  $\mu sec$ ) featuring offset control and two thresholds: a lower (LLD) and an upper (ULD) threshold. This makes it possible to assign different threshold and offset (zero time intercept) values to each measuring channel. A "Parameters Memory" contains the LLD, ULD and OFFSET values of each single channel.

A 6-bit register (STATUS REGISTER) allows different data acquisition and readout modes of the 8 channels. Data may be readout either via CAMAC or via the ECL Data Bus, depending upon the Status Register state. Both the Status Register and Parameters Memory must be previously loaded via CAMAC. If enabled, the ECL Data Bus, located on the front-panel, sends analog-to-digital conversion data sequentially in words of 16 bits with differential ECL levels (the first 12 bits are data bits plus 3 subaddress bits, plus the "Overflow" bit, if it exists). A REQ output signal is generated when the ECL Data Bus is ready to deliver data.

In CAMAC mode, data is always read in 16 bit words in either sequential (Q stop mode) or addressed mode. When data is ready, a LAM signal may be generated and there is Q=1 with the readout function N.F(0) or N.F(2). The instrument includes provisions for testing the 8 input modules of the 3371 ADC via a CAMAC-controlled TEST signal with function N.F(25).A(0). This signal simulates a START command and applies a STOP signal corresponding to about 1/2 of the dynamics to the input of each channel.

The ADC may be in any of two states: "Idle" or "Busy", depending on the START, CLEAR and internal CLEAR signals. (Internal CLEAR is applied after a conversion if there is no valid data or when data readout is performed in a sequential mode.) START and CLEAR may be sent either via front-panel (ECL Command Bus) or via CAMAC.

After a CLEAR signal, the ADC is in the "Idle" state, that is it is ready to receive a START signal (front-panel or test). The Status Register and the Parameters Memory may be loaded only when the module is in the "Idle" state. The START signal (front-panel or test) causes the ADC to go to the "Busy" state, during which no further START signal is allowed. Data conversion is enabled approximately 1 µsec after the end of the Full Scale Time Monostable triggered by START signal, and at the end of the conversion time data readout is initiated. At this point, depending on the state of the Status Register and the data converted by the ADC, any of three conditions may occur:

- 1. Data readout via ECL Port only (EEN=1, see Status Register).

- Data readout via CAMAC only (EEN=0).

- 3. No data to be read. In this case, no data readout is performed.

To disable the ongoing data conversion or to accept further START signals during the "Busy" state, it is necessary to apply a CLEAR signal. The ADC is ready to perform a new data acquisition 1.2  $\mu$ sec after the CLEAR signal.

#### **Analog Inputs (STOPS)**

The 8 analog inputs are designed to accept either differential or single-ended ECL signals, depending upon the input stage setting. In the standard version the input is preset for differential ECL connection via twisted-pair connecting cables. The input impedance is 100 ohms. On request, the instrument can also be supplied in the single-ended version for connection via coaxial cables with input impedance of 50 ohm.

#### **CLEAR Function**

The CLEAR function may be enabled either by an ECL CLEAR command via the front-panel ECL Bus or by CAMAC functions Z, C, and N.F(9).A(0). It is strobed by S2 or by an internal command generated after completion of sequential data readout or at the end of conversion, if no valid data is present.

After a CLEAR signal, the ADC changes to the "Idle" state and is held in this state until the next START signal is applied. During the CLEAR signal (duration of about 1.2  $\mu$ sec) the input START is inhibited.

It is recommended to avoid sending new START commands in coincidence with the end of the CLEAR signal. This will prevent generation of sliced START commands.

#### **External START Input**

The START command should be sent only when the module is in the "Idle" state. It should never be sent in coincidence with the CLEAR signal (at least 1.2  $\mu$ sec after the CLEAR function has been initialized). The START input may be inhibited by line I (CAMAC inhibit). A START signal activates the following functions:

- 1. Enable the T modules.

- 2. Apply "START" signals to the modules.

- 3. Inhibit the "START" input (Common START).

- 4. Trigger the "Full Scale Monostable" (200 ns in the standard version).

After a 1  $\mu$ sec time delay it starts conversion, causing the ADC to change to the "Busy" state. To overcome any "crosstalk" problem between the end of the "START" pulse and "STOP" pulses, the use of a START pulse having a duration higher than the TAC (Time-to-Amplitude Converter) dynamics is strongly recommended.

## ADC Threshold and Offset Memory

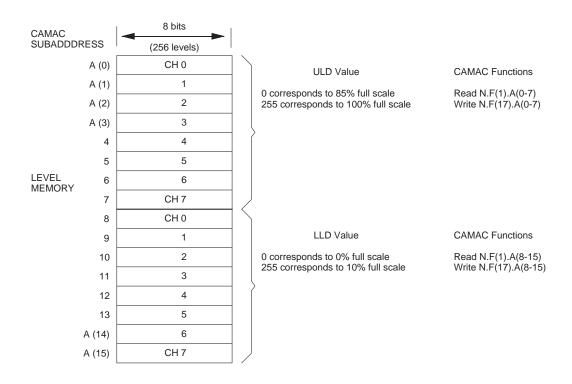

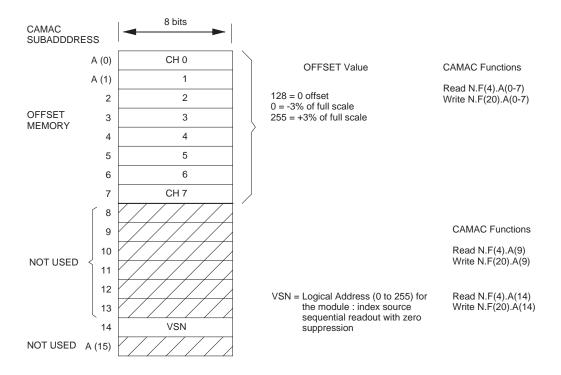

The 3371 TDC includes a Parameters Memory made up of two 16x8 words groups. With the module in the "Idle" state, the threshold values (Low Level Discriminator-LLD; Upper Level Discriminator ULD), as well as the Offset and VSN (Virtual Station Number) values can be loaded into the Parameters Memory. Different threshold (ULD and LLD) and offset values may be assigned to each input.

A schematic diagram of the TDC Parameters Memory is illustrated in the following drawing.

#### **Test Function**

The TEST function is initiated by the CAMAC command N.F(25).A(0) strobed by S2. If accepted, Q is equal to 1. This function is accepted only when the TDC is in the "Idle" state. This function performs the following operations:

- Applies a START command.

- 2. Generates a "STOP" command common to all the 8 modules. This command determines a time equal to about a half of the TAC dynamics. During the entire duration of this pulse no signal is allowed on any of the inputs, even if the interconnecting cable may remain connected. The START command (front panel) must not be sent while the Test function is in progress.

#### Overflow

The TDC actual dynamics is 3840 channels (4096 - 256); 256 channels are reserved for the Sliding Circuit. Data having a content greater than or equal to 3840 is not considered to be valid for measurement. If this data is present, an Overflow indication is generated by the ADC control circuit. Via the Status Register bit (R12) (See Status Register) it is possible to enable the Data Memory to associate the Overflow information with the conversion data and store it into the DATA WORD at position R16 (see ECL or CAMAC Data Structures).

#### **Status Register**

The Status Register is a memory into which the Status Word is loaded. The Status Register is made up of two distinct sections.

The first (low order 8-bit) consists of a word of the Parameters Memory and contains the address number of the module (VSN, or Virtual Station Number). This is used to identify the data source during sequential readout with zero suppression mode.

The other section contains the information that determines the data acquisition and readout modes. The Status Register is written by the CAMAC function N.F(20).A(14) strobed by S1 and is readout by-function N.F(4).A(14).

These two functions are accepted only when the module is in the "Idle" state; there is Q response when the functions are accepted. After switching on the module, the content of the Status Register is undefined. The CAMAC initialization function (Z) sets the 6 Status Register bits (R10 through R16) to the "1" state, but will not affect the VSN register, whose content remains undefined. The other CLEAR signals will not reset the Status Register.

| R16 |     |     |     |     |     |     |   | R8  | R1 |

|-----|-----|-----|-----|-----|-----|-----|---|-----|----|

| 0   | CLE | CSR | CCE | OVF | EEN | SUB | 0 | VSN |    |

The six functions of the Status Register are as follows:

#### SUB (W10-R10) Channel Subaddress Enable

If enabled (SUB = 0), in addition to the ADC data, the binary addresses of the 8 analog memories (0 for the 0 channel, etc.) are loaded into the Data Memory at position R13, R14, R15. If SUB = 1, the value of R13-R14-R15 in the Data Word is always "zero".

#### EEN (W11-R11) ECL Bus Enable

If EEN = 1, only the ECL port readout is enabled. If EEN = 0, only CAMAC readout is enabled.

#### **OVF (W12-R12) Overflow Indication Enable**

If OVF = 0, the Overflow indication, if it exists, is loaded into the Data Memory at position R16. If OVF = 1, the value of R16 in the Data Memory is always "zero".

#### CCE (W13-R13) Zero Suppression Enable

#### CSR (W14-R14) Sequential Readout Enable

These two bits allow 3 different data acquisition and readout modes to be performed.

- With Zero Suppression CSR = 1 and CCE = 1

Data conversion takes place only in valid channels (i.e. channels with pulses falling within the LLD-ULD window). These valid channels are read out in sequential mode either via the ECL bus or CAMAC.

- Without Zero Suppression CSR = 1 and CCE = 0

All the 8 input channels are converted and read sequentially.

Readout may be either via the ECL BUS or CAMAC.

- Addressed Readout CSR = 0 and CCE = Indifferent

All the 8 channels are converted and the ADC data is read by

CAMAC only in addressed mode with any of two functions

N.F(0).A(0-7) or N.F(2).A(0-7). The readout channel is identified

by Subaddress A: A(0) = channel 0 etc.

#### CLE (W15-R15) CAMAC LAM Enable

If CLE = 1, the LAM output is enabled to indicate that there is valid data to be read by CAMAC; in the Zero Suppression mode, if no valid data is present, LAM will not be enabled. If CLE = 0, the LAM output will be disabled.

**Note:** After the CAMAC initialization (Z) the 6 bits of the Status Register are set to "1". This means With Zero Suppression mode, ECL readout, SUB and OVF disabled.

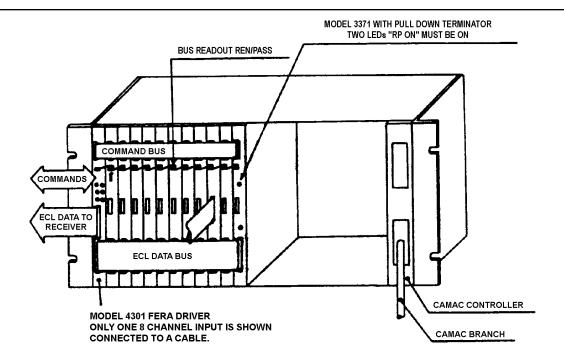

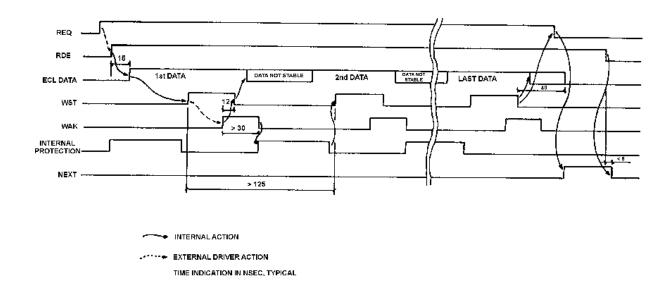

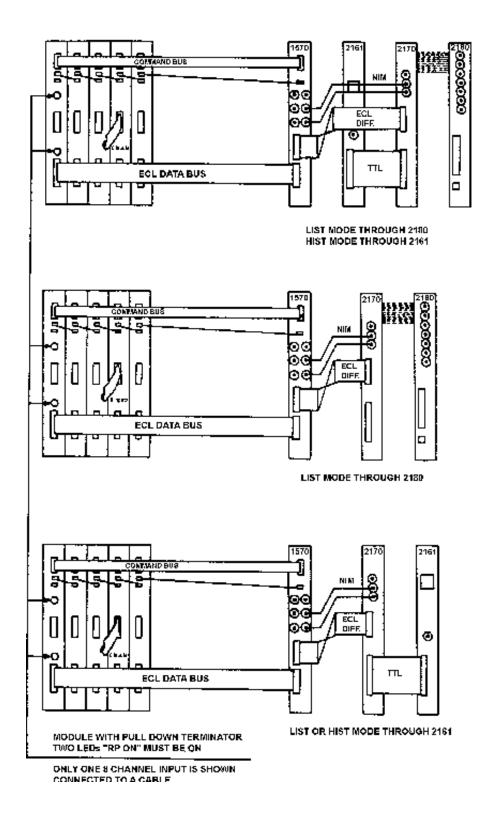

**ECL Data Bus**

The module delivers 16-bit data words with complementary ECL Outputs at the ECL Data Bus connector. The maximum readout frequency is 8 MHz. If several modules are connected, the pull-down resistors must be removed in all modules, except for the last module (see Figure 1). When these resistors are mounted, the associated LED indicator is lighted. If several modules are connected, only the positive ECL output is used; the negative output should be connected to ground.

Figure 1: FERA System Connections

#### **ECL BUS - REN/PASS**

In addition to the ECL CLEAR and GATE signals, all those signals with ECL levels that control and allow use of the ECL DATA Readout are present at the ECL Bus and REN/PASS connectors.

These signals include:

#### 1. Busy Output (BUSY)

This output is set to the "1" state 1  $\mu$ sec after the end of the Full Scale Time Monostable triggered by START signal and is held to this state until after the end of the readout cycle (ECL Readout or CAMAC Readout). The BUSY state may be reset only by sending a CLEAR signal via CAMAC or via ECL Bus (CLR). The ADC is ready to start a new conversion 1.2  $\mu$ sec after the end of the BUSY state.

#### 2. Write Strobe Output (WST)

Indicates the time period during which the data word present on the ECL Data Bus can be stored in the external memory. WST is generated a minimum of 10 ns after the data is ready. Its width is higher than 40 ns. The ECL Data Bus data is maintained stable as long as the WST pulse lasts.

#### 3. Request Output (REQ)

Indicates that the module is ready to send data to the ECL Data Bus. The REQ signal is generated at the end of conversion if the bit related to ECL Readout in the Status Register has been set. The REQ signal remains until after the last data word has been read or a CLEAR command has been given.

#### 4. Write Acknowledge Input (WAK)

This input receives the acknowledge signal indicating that the data present on the ECL Bus has been loaded into memory and the next data word may be sent. The next WST signal is generated at least 50 ns after the WAK signal. Minimum WAK width must be 30 ns.

#### **ECL PORT ENABLE/PASS**

#### 1. Readout Enable Input (REN)

The REN signal indicates to the module that it can take control of the ECL Data Bus; REN must be maintained during the entire readout time. The signal enables the ECL Data Bus, WST Output and WAK input if the module is ready for data transfer (REQ output ON). If there is no data present (REQ=OFF) the REN signal automatically generates the PASS signal, which becomes REN for the next module.

#### 2. PASS Output (PASS)

Indicates that the module is not ready to transfer data present on the ECL Data Bus or it has completed data transfer. The PASS output signal is generated by the REN line in the absence of the REQ internal command or, if this command is present, at the end of data readout. The transit time between the REN and PASS output is typically 3 ns (6 ns maximum) if the module does not include data readout capabilities.

As previously mentioned for the ECL Data Bus, if several modules are connected, it is necessary to remove the pull-down resistors in all modules, except for the last one. The LED indicator is lighted when the resistors are mounted (see Figure 1). The timing sequence of ECL Data transfer is the following:

- After data conversion, the ADC module sends the REQ signal and waits for the REN Readout Enable.

- 2. An external driver provides the REN line.

- 3. The REN signal clocks the internal flip-flop in the requesting ADC module and inhibits the PASS output. The non-requesting ADCs closer to the driver are disabled by the same REN signal. The non-requesting ADCs far away from the driver do not receive the REN signal because it is stopped in the requesting module (no PASS signal). Moreover, the REN signal sets the WST line high and enables the first data word to transit through the ECL Data Bus. The module remains in this state waiting for the WAK signal. As soon as the WAK signal is received, the WST signal is released and is held to this position for at least 60 ns by an internal protection. During this time the module makes available the next data word Which is loaded into the ECL Data Bus with the leading edge of the next WST signal.

- 4. After the last data word from an ADC has been read, the request REQ signal is removed and the REN signal is routed to the PASS output, thus enabling readout of the next ADC module.

- 5. If a far off ADC has sent in a request, the common REQ line remains high and data readout from this module is initiated.

6. If a module closer to the driver has data ready, it waits until the REN signal goes low and as soon as this occurs it sends its own REQ signal. (This module was disabled by the REN signal).

#### **ECL Bus Readout Interrupt**

An ongoing ECL Bus readout may be momentarily interrupted in two different ways.

- By not sending a WAK signal after a WST signal. In this case, the data word on the ECL Data Bus remains until the WAK signal is received.

- By interrupting the WAK signal, stopping it after the first transition. If this occurs, the WST command is terminated and the next data word is placed on the ECL Data Bus, but it is only upon release of the WAK signal that the next WST will be activated again.

#### **ECL Data Structures**

Note: EEN, CSR, and CCE are STATUS WORD bits.

1. EEN = 1, CSR = 1, CCE = 1

Zero suppression is on. Up to 8 data words is to be read. Sequential readout only is possible on ECL BUS. Bit 16 = OVF (overflow) is enabled when OVF-bit in Status Register is 0. Subaddress bits are enabled when SUB bit in Status Register is 0.

| R16 | R15 R13 | R12 R1 | Offset |

|-----|---------|--------|--------|

| OVF | SUB     | 0-DATA | 1      |

| OVF | SUB     | 1-DATA | 2      |

| OVF | SUB     | 2-DATA | 3      |

| OVF | SUB     | 3-DATA | 4      |

| OVF | SUB     | 4-DATA | 5      |

| OVF | SUB     | 5-DATA | 6      |

| OVF | SUB     | 6-DATA | 7      |

| OVF | SUB     | 7-DATA | 8      |

Always 8 data words are to be readout. Sequential readout only is possible on ECL BUS. Bit 16 = OVF (overflow) is enabled when OVF-bit in Status Register is 0. Subaddress bits are enabled when SUB bit in Status Register is 0.

## **CAMAC Commands** and Functions

Note: If the module is in BUSY Status (BUSY LED on), only data readout and clear functions can be executed. Busy is released after clear and when all data is readout. The BUSY line is connected on the Common ECL Bus.

**F(0)•A(0):** Reads the data memory sequential (CSR=1). Memory

address is incremented with S2. Q-response is 1 if there

is the data to be readout.

F(0)•A(0-7): Reads data addressed (CSR=0). Q-response is 1 if

there is the data to be readout.

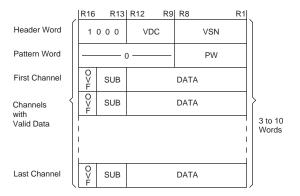

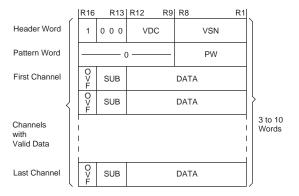

**F(0)•A(14):** Reads Header Word (Q=1 if module is in BUSY status).

#### **HEADER WORD**

| R16 |   | R12 | R8  | R1 |

|-----|---|-----|-----|----|

| 1   | 0 | VDC | VSN |    |

Header Word contains an information about the logical address of the module (VSN virtual station number bit 1-8) loaded to STATUS REGISTER, and an information about a number of valid data (VDC valid data counter). Q-response is 1 if there is the data to be readout.

**F(0)•A(15):** Reads Pattern word (Q=1 if module is in BUSY Status).

#### **PATTERN WORD**

| R16 | R12 | R8 |              | R1 |

|-----|-----|----|--------------|----|

| 0   | 0   |    | PATTERN WORD |    |

Pattern Word contains a bit muster that shows which channel has valid data. Bit R1 corresponds to ch. 0.

**F(1)•A(0-7):** Reads threshold Memory (upper threshold).

Q=1 if BUSY=0.

**F(1)•A(8-15):** Reads threshold Memory (lower threshold).

Q=1 if BUSY=0.

**F(2)•A(0):** Reads the data memory sequential (CSR=1). Memory

address is incremented with S2. Q =1 if there is the data

to be read out.

F(2)•A(0-7): Reads data addressed (CSR=0) and clears with

F(2)•A(7) strobed on S2. Q=1 if there is the data to be

read out.

**F(2)•A(14):** Reads Header Word in data addressed mode (CSR=0)

(Q=1 if module is in BUSY status).

F(2)•A(15): Reads Pattern Word and clears LAM (Q=1 if module is

in BUSY status).

**F(4)•A(0-7):** Reads offset memory (Q=1 if module is not in BUSY

status).

**F(4)•A(9):** Reserved for 3341 and 3351 ADCs.

**F(4)•A(14):** Reads Status Word Register (Q=1 if module isn't in

BUSY status).

F(8)•A(0): Tests LAM. Q=1 if LAM is set.

**F(9)•A(0):** Clears ADC and control logic. Does not clear memories

and status register.

**F(10)•A(0):** Clears LAM. Q=1.

**F(16)•A(0-7):** Reserved for ADC Model 3341.

**F(17)•A(0-7):** Writes threshold memory (upper threshold) 8 bits

(0-255) correspond to 85-100% full scale. (Q=1 if

module isn't in BUSY status).

**F(17)•A(8-15):** Writes threshold memory (lower threshold) 8 bits (0-255)

correspond to 0-10% full scale. (Q=1 if module isn't in

BUSY status).

**F(20)•A(0-7):** Writes offset memory 8 bits (0-255) correspond to  $\pm 3\%$

of full scale, 128 correspond to 0 V. (Q=1 if module isn't

in BUSY status).

**F(20)•A(9):** Reserved for 3341 and 3351 ADCs.

F(20)•A(14): Writes Status Word Register (Q=1 if module isn't in

BUSY status).

#### **STATUS WORD**

| R16 |     |     |     | R12 |     |     |   | R8  | R1 |

|-----|-----|-----|-----|-----|-----|-----|---|-----|----|

| 0   | CLE | CSR | CCE | OVF | EEN | SUB | 0 | VSN |    |

R1-R8 (VSN) Logical address of the module.

R10 (SUB) when SUB=0, subaddress enabled (see data structure).

R11 (EEN) when EEN=1, ECL readout enabled; EEN=0 CAMAC

enabled.

R12 (OVF) when OVF=0, the overflow bit enabled (see data structure).

R13 (CCE) when CCE=1, zero suppression enabled, only if CSR=1.

R14 (CSR) when CSR=1, CAMAC sequential readout enabled.

R15 (CLE) when CLE=1, CAMAC LAM enabled.

Note: The all bits of S.W.R. are set to 1 by CAMAC Z=init. function.

**F(25)•A(0):** Test function (Q=1 if module isn't in BUSY status).

**Z**: Initialize; clears the module and sets the Status Register

bits 9-16 to 1. Does not clear the memory.

**C:** Clears the Module. Does not clear the Status Register

and memory.

**I:** Inhibits the GATE input.

**X:** X response is generated for all valid functions.

**Q:** Q response is generated when the function can be

executed.

L: LAM set, if enabled, after the end of conversion and if

there is valid Data to be read.

The Status Word Register CLE, CSR, CCE, OVF, EEN, SUB bits, VSN - Virtual Station Number and Parameters Memory must be written before acquisition begins.

#### **CAMAC Readout**

CAMAC Readout may be performed in either "sequential" mode or "addressed" mode, depending upon the state of the CSR bit of the Status Register.

**CSR = 1:** Enables "Sequential Readout": at the end of the conversion cycle the first data word is available on the CAMAC Dataway. The Q response is given as long as there is data to be read. After the last data word has been read, the internal CLEAR signal causes the ADC to go to the "Idle" state. Data is read with functions N.F(0).A(0) or N.F(2).A(0). On completion of the readout of each single data word (at the end of S2) the address of the ADC Data Memory is incremented and the next data word is sent.

**CSR = 0:** Enables "Addressed Readout": at the end of the conversion cycle, the various channels can be read by addressing the channel to be read via CAMAC with Subaddress A. Readout functions are N.F(0).A(0-7) or N.F.(2).A(0-7). With function N.F(0).A(0-7) the Q response is given each time a data word is read and the module is maintained enabled to send the requested data until a CLEAR function is released. With function N.F(2).A(0-7) the Q response is given each time a data word is read but the CLEAR function is automatically generated by Subaddress 7 [N.F(2).A(7)] strobed by S2.

#### **LAM Handling**

The LAM (Look-at-me) is activated when the related bit of the Status Register is set to "1". It is activated as soon as data is ready for CAMAC

readout. During "Sequential Readout" the LAM is reset after the last data word has been read. Function N.F(8).A(0) is used to test the state of the LAM. Q = 1 if the LAM is present. The LAM may also be cleared by the following functions ECL CLEAR front panel, Z, C, N.F(9).A(0) strobed by S2.

#### **CAMAC Data Structures**

Note: EEN, CSR and CCE are Status Word bits.

1. Read Data F(0).A(0), F(2).A(0), EEN = 0, CSR = 1, CCE = 1

Zero suppression is on. Up to 8 data words are to be read. Sequential readout is on. Bit 16=OVF (overflow) is enabled when OVF-bit in Status Register is 0. Subaddress bits are enabled when SUB bit in Status Register is 0.

2. Read Data F(0)A(0), F(2)A(0), EEN = 0, CSR = 1, CCE = 0

| R16 | R15 R13    | R12 R1     | Offset |  |  |

|-----|------------|------------|--------|--|--|

| OVF | SUB        | 1-DATA     | 1      |  |  |

| OVF | SUB        | SUB 2-DATA |        |  |  |

| OVF | SUB        | 3-DATA     | 3      |  |  |

| OVF | SUB 4-DATA |            | 4      |  |  |

| OVF | SUB        | 5-DATA     | 5      |  |  |

| OVF | SUB        | 6-DATA     | 6      |  |  |

| OVF | SUB        | 7-DATA     | 7      |  |  |

| OVF | SUB        | 8-DATA     | 8      |  |  |

Always 8 data words are to be readout. Sequential readout is on. Header Word can be read with  $F(0) \cdot A(14)$  or  $F(2) \cdot A(14)$ . Pattern Word can be read with  $F(0) \cdot A(15)$  or  $F(2) \cdot A(15)$ .

Bit 16=OVF (overflow) is enabled when OVF bit in Status Register is 0. Subaddress bits are enabled when SUB bit in Status Register is 0.

3. Read data F(0).A(0-7), F(2).A(0-7), EEN = 0, CSR = 0, CCE = X

| R16 | R15 R13 | R12 R1    | Offset |

|-----|---------|-----------|--------|

| OVF | SUB     | A(0)+DATA | 1      |

| OVF | SUB     | A(1)-DATA | 2      |

| OVF | SUB     | A(2)-DATA | 3      |

| OVF | SUB     | A(3)-DATA | 4      |

| OVF | SUB     | A(4)-DATA | 5      |

| OVF | SUB     | A(5)-DATA | 6      |

| OVF | SUB     | A(6)-DATA | 7      |

| OVF | SUB     | A(7)-DATA | 8      |

CAMAC Addressed (random) readout. Bit 16=OVF (overflow) is enabled when OVF bit in Status Register is 0. Subaddress bits are enabled when SUB bit in Status Register is 0.

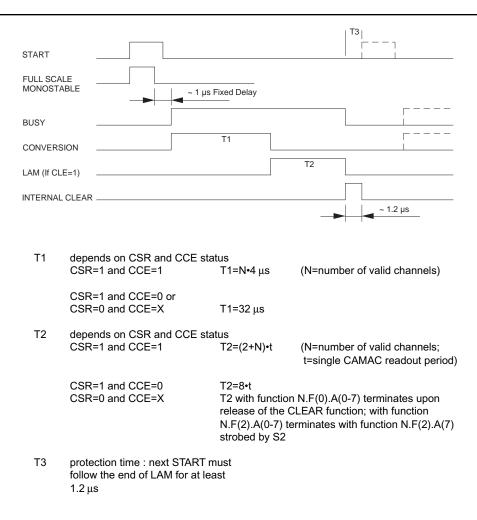

### **Readout Timing Diagram**

Figures 2 and 3 show the readout timing sequence via CAMAC and via ECL BUS.

Figure 2: Acquisition and CAMAC Readout Timing. Note: this diagram does not define the logic state of the signals: Low = FALSE, High = TRUE

Figure 3: ECL BUS Timing. Note: this diagram does not define the logic state of the signals: Low = FALSE, High = TRUE

Figure 4: CES System Connection

#### TECHNICAL INFORMATION

#### General

The 3371 module consists of three different printed cards including:

- A Mother Board containing the START, TEST and ECL logic circuit and the TTL → ECL adapting circuitry related to the front-panel Bus. It also accommodates the 8 analog modules.

- 2. Eight analog modules (analog memories).

- 3. A card accommodating the Analog-to-Digital Converter, Thresholds, DACs and the entire logic circuitry of the module.

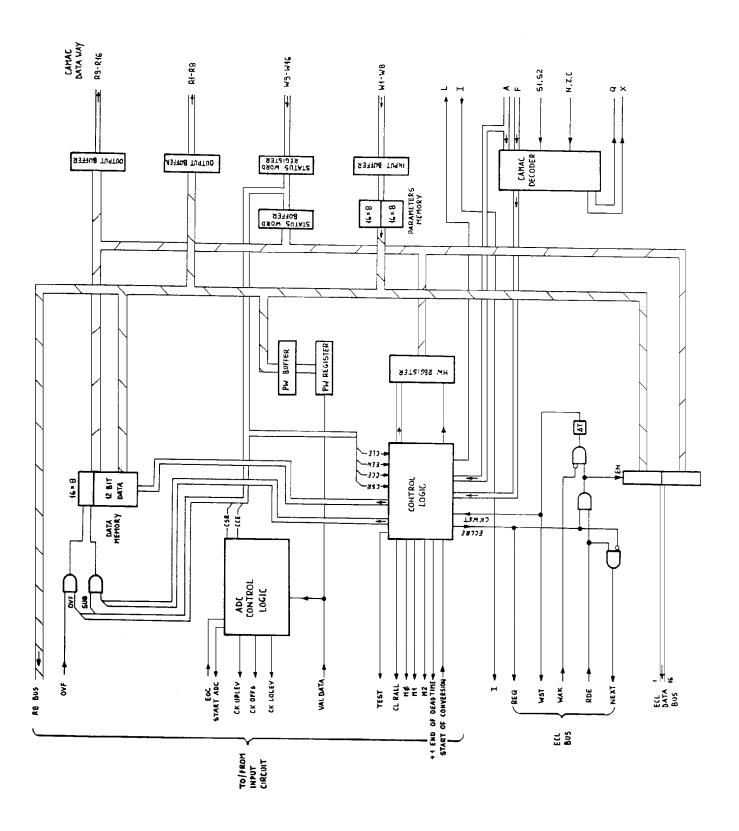

## Description (see Figure 5)

A "START" input signal or a monostable triggered by the TEST function N.F(25).A(0) - S2 initiates the following sequence:

- 1. Enables the "T" modules.

- 2. Sends START commands to the "T" modules.

- 3. Inhibits further "START" signals (Common Start).

- 4. Triggers the "Full Scale Monostable" (200 ns in the standard version).

- The end of the "Full Scale Monostable" triggers the "ΔT" monostable (waiting time for the multiplexer settling time and LLD-ULD and Offset preset).

- 6. The end of the " $\Delta T$ " monostable sets "Busy" state and starts conversion.

As long as the module is in the "Busy" state all functions of the CAMAC decoder are disabled, except the readout and CLEAR functions. The measurement of the time interval between START and STOP is individually performed for each single channel by a module using SMT (Surface Mounting Technology) techniques. The circuit operating principle is based on the integration of a constant current injected in capacity C for the time period between a START pulse and a STOP pulse with further memorization. The START pulse sets flip-flop FF1, whose output wired-OR with the START input inhibits the input. The START line common to all 8 modules sets flip-flops FFa and FFb. FFa opens switch S2 and FFb closes S1. Current I passing through the fast operational amplifier Aa is injected into capacity C and generates a voltage V proportional to the time during which switch S1 remains closed.

On occurrence of the STOP signal, FFb is reset and switch S1 is opened, with the result that current I is interrupted. The condition present at the output of the amplifier is given by the following relation:

$$V_{out} = \frac{I \cdot t}{C}$$

(for example t = full scale = 200 ns  $V_{out} = 1 \text{ V}$ )

Application of the START signal generates a time delay of 200 ns corresponding to the full scale in the standard version of the module. On expiration of this time delay a STOP signal is simulated for all the 8 modules (Overflow).

To eliminate "crosstalk" problems between the end of the START and STOP signal, use of a START signal having a length higher than the TAC (Time-to-Amplitude Converter) dynamic range is strongly recommended. The analog outputs of the 8 modules are connected to an analog multiplexer. Three lines (M0, M1 and M2) sequentially select the input of the analog multiplexer, whose output is amplified in cascade by 10 (GA1.GA2 = 10) and then routed to the ADC. The ADC used is a successive approximation (SAR) type using the differential linearity correction method (Sliding Scale) devised by Prof. Emilio Gatti. The values of the Upper Threshold (ULD), Offset and Lower Threshold (LLD) levels of the 8 measurement inputs are stored in the Parameters Memory while the module is in the "Idle" state by the following functions:

N.F(17).A(0-7) ULD N.F(17).A(8-15) LLD N.F(20).A(0-7) OFFSET

The values are loaded into the associated registers before each single conversion by the following commands:

CKUPLEV = loads the value in the upper level register; 0 corresponds to 85%, 255 corresponds to 100%.

CKOFFS = Loads the value in the offset register; 0 corresponds to -3%, 128 corresponds to 0, 255 corresponds to +3%.

CKLOLEV = loads the value in the lower level register; 0 corresponds to 0%, 255 corresponds to 10%.

If the module is set for operation in the "Zero Suppression Mode" data conversion takes place only in the measuring channels whose value is higher than the set LLD level and lower than the ULD level. If the module is set for operation in the "Without Zero Suppression Mode" or "Addressed Readout Mode", data conversion is performed on all the 8 inputs independently of the threshold values.

#### **Analog Inputs Impedance**

The Model 3371 usually is supplied in the "Dual Ended Input" version using twisted-pair connecting cables. The input impedance is 100 ohms.

On request, the module can be supplied in the "Single Ended Input" version for connection via coaxial cables and with an in put impedance of 50 ohms.

Figure 5: Logic Circuit Block Diagram