# **ADM1224F**

24-Channel, 12-Bit, ±10 Volt Differential-ended-input, Multiplexed Analog-to-Digital Converter IPack

Document No. B-T-MU-ADM1224F-A-0-A1

# PRELIMINARY DOCUMENT

|  |  |  |  | · |  |

|--|--|--|--|---|--|

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

# **FOREWORD**

The information in this document has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. SYSTRAN reserves the right to make changes without notice.

SYSTRAN makes no warranty of any kind with regard to this printed material including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

The schematic diagrams contained in this publication are included for reference only. The information was current at the time the printed circuit board was last revised. This information is not necessarily current or complete manufacturing data, nor is it part of the product specification. Schematics may not be reproduced without the express permission of SYSTRAN Corp.

Copyright 1996 SYSTRAN Corporation. All rights reserved.

ALTERA® and Altera® are registered trademarks of Altera Corporation

HP™ is a trademark of the Hewlett-Packard Corporation

IndustryPack® is a registered trademark of GreenSpring Computers, Inc.

Motorola® is a registered trademark of the Motorola Corporation.

NuBus™ is a trademark of Texas Instruments, Inc.

OS-9® is a registered trademark of Microware Systems Corporation

TRI-STATE® is a registered trademark of National Semiconductor Corporation

VIEWlogic® is a registered trademark of Viewlogic Systems, Inc.

Revised: July 24, 1996

SYSTRAN Corporation 4126 Linden Avenue Dayton, OH 45432-3068 (513) 252-5601

# **TABLE OF CONTENTS**

| 1.0 INTRODUCTION                                       |       |

|--------------------------------------------------------|-------|

| 1.1 Purpose                                            | 1-1   |

| 1.2 Scope                                              | .1-1  |

| 1.3 Overview                                           | .1-1  |

| 1.3.1 The Name                                         |       |

| 1.3.2 Features                                         |       |

| 1.4 Specifications                                     | . 1-3 |

| 1.5 Related Products                                   | .1-6  |

| 1.6 Related Publications                               | . 1-6 |

| 1.7 Ordering Process                                   | .1-6  |

| 1.8 Technical Support                                  | .1-6  |

| 1.9 Reliability                                        | .1-7  |

| 2. 0 DESCRIPTION                                       |       |

| 2.1 Simplified Block Diagram                           | .2-1  |

| 2.1.1 Simplified Block Descriptions                    | .2-1  |

| 2.2 Middle Block Diagram                               | .2-4  |

| 2.2.1 Middle Block Descriptions                        | .2-4  |

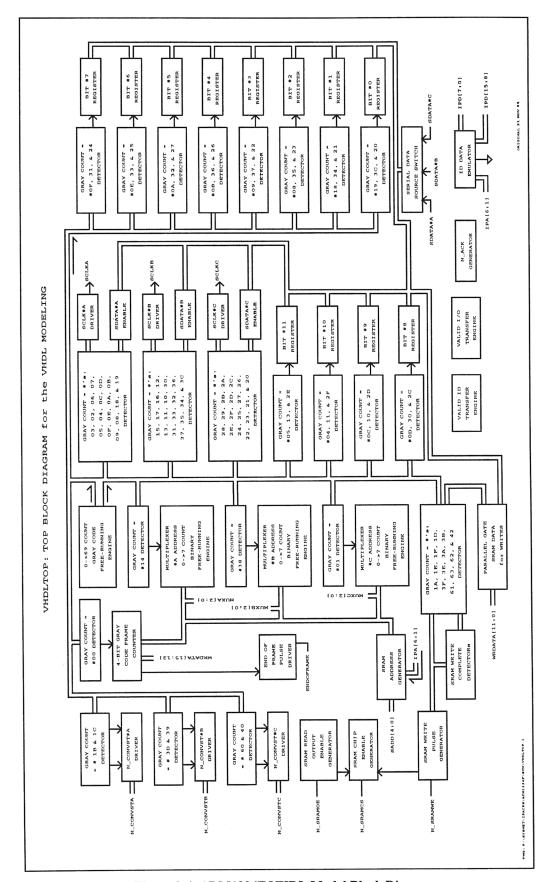

| 2.3 Detailed Block Diagram                             | .2-6  |

| 2.3.1 Detailed Block Descriptions                      | .2-6  |

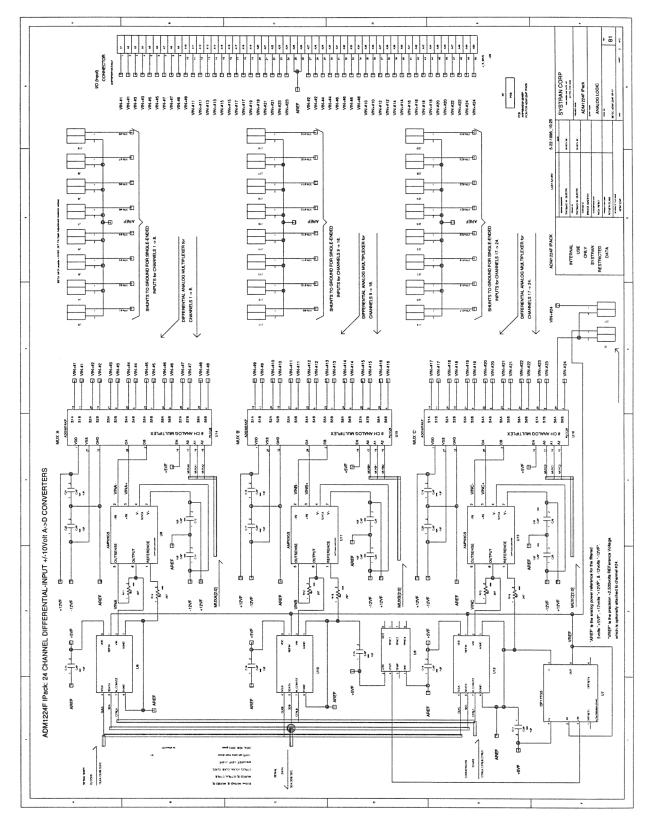

| 2.4 ADM1224F SCHEMATICs                                | .2-8  |

| 2.4.1 SCHEMATICS - SHEET 1 - COMPONENTS                | .2-8  |

| 2.4.2 SCHEMATICS - SHEET 2 - COMPONENTS                | .2-9  |

| 2.5 SAMPLING DETAILS                                   | 2-11  |

| 2.5.1 SAMPLING ORDER                                   | 2-11  |

| 2.5.2 SAMPLING RATE                                    | 2-11  |

| 2.5.3 SAMPLING TIMING                                  | 2-12  |

| 2.5.4 DETERMINISTIC SAMPLING                           | 2-13  |

| 2.6 GRAY CODE ENGINE DETAILS                           | 2-14  |

| 2.7 PERFORMANCE EFFICIENCY                             | 2-14  |

| 2.8 VHDL-BASED ACTIVITY                                |       |

| 3. 0 HARDWARE INSTALLATION                             | 3-1   |

| 3.1 Unpacking the ADM1224F                             | 3-1   |

| 3.2 Visual Inspection                                  | 3-1   |

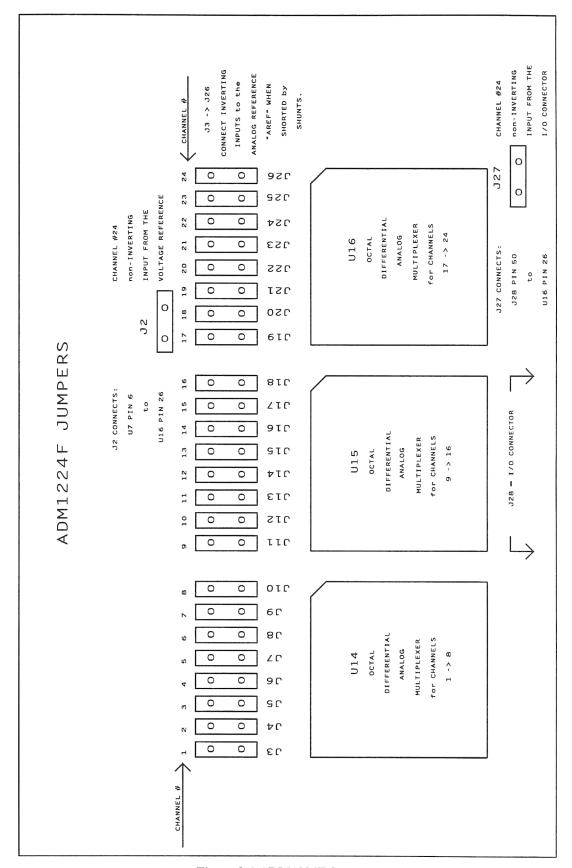

| 3.3 Jumper Shunts                                      | 3-1   |

| 3.4 Wiring and Jumpering                               | 3-3   |

| 3.4.1 Single-ended, Non-inverting Input Channels       | 3-3   |

| 3.4.2 Single-ended, Inverting Input Channels           | 3-3   |

| 3.4.3 Differential-ended, Non-Inverting Input Channels | 3-3   |

| 3.4.4 Differential-ended, Inverting Input Channels     | 3-4   |

| 3.4.5 Unused Inputs                                    | 3-4   |

| 3.4.6 VREF Connections                                 | 3-5   |

| 3.4.7 High Shock/Vibration applications                | 3-5   |

| 3.5 ADM1224F Installation                              | 3-6   |

| 4.0  | PROGRAMMING GUIDE                                                     | 4-1 |

|------|-----------------------------------------------------------------------|-----|

|      | 4.1 Overview                                                          | 4-1 |

|      | 4.2 Description                                                       | 4-1 |

|      | 4.3 IPack ID PROM Listing                                             | 4-1 |

|      | 4.4 IPack I/O Address Map                                             |     |

|      | 4.5 Word Access Address Translation                                   |     |

|      | 4.6 Byte Access Address Translation                                   |     |

|      | 4.7 Data Registers Bit Description (IPA=00 → 17 hex)                  | 4-6 |

|      | 4.7.1 Data Registers 0 to 17 (IPA = $00 \rightarrow 17 \text{ hex}$ ) | 4-6 |

|      | 4.8 Programming Example                                               | 4-6 |

|      | 4.9 Integer Register Value to Floating Point Voltage Conversion       | 4-6 |

| 5. 0 | PERFORMANCE                                                           | 5-1 |

|      | 5.1 Purpose                                                           | 5-1 |

| 6. 0 | TYPICAL APPLICATIONS                                                  | 6-1 |

|      | 6.1 Purpose                                                           | 6-1 |

| 7. 0 | WARRANTY AND REPAIR                                                   | 7-1 |

|      | 7.1 Warranty Coverage                                                 | 7-1 |

|      | 7.1.1 Hardware Warranty Service                                       |     |

|      | 7.1.2 Software Warranty Service                                       |     |

|      | 7.1.3 Other Services                                                  |     |

|      | 7.2 Additional Paid Services                                          | 7-2 |

|      | 7.3 Term                                                              | 7-2 |

|      | 7.4 Conditions                                                        | 7-2 |

|      | 7.5 Identification of Covered Products                                |     |

|      | 7.6 Shipping                                                          | 7-2 |

|      | 7.7 Life Support and Nuclear Policy                                   |     |

|      | 7.8 Communication                                                     | 7-3 |

# **APPENDICES**

APPENDIX A - SYSTRAN's IndustryPack Logic Interface Specification Synopsis APPENDIX B - ADM1224F Schematics

# **FIGURES**

| Figure 1-1 | ADM1224F Board                             | 1-1 |

|------------|--------------------------------------------|-----|

|            | ADM1224F Simplified Block Diagram          |     |

| Figure 2-2 | ADM1224F Middle Block Diagram              | 2-3 |

| Figure 2-3 | ADM1224F Detailed Block Diagram            | 2-5 |

|            | ADM1224F VHDL Model Block Diagram          |     |

| Figure 3-1 | ADM1224F Jumpers                           | 3-2 |

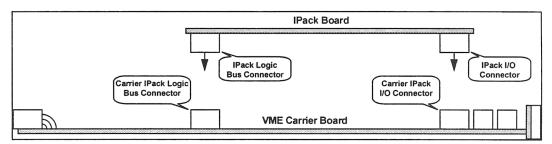

| Figure 3-1 | ADM1224F Installed on a VME IPack Carrier  | 3-6 |

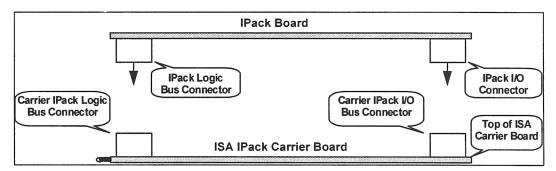

| Figure 3-2 | ADM1224F Installed on an ISA IPack Carrier | 3-6 |

|            |                                            |     |

# **TABLES**

| Table 2-1 | GRAY CODE Sequence Engine Activities   | 2-15 |

|-----------|----------------------------------------|------|

| Table 3-1 | Contents of ADM1224F Shipping Packages | 3-1  |

| Table 3-7 | ADM1224F Installation Tools            | 3-6  |

| Table 3-3 | IPack Logic Bus Pin Assignments        | 3-8  |

| Table 3-4 | IPack I/O Connector Pin Assignments    | 3-9  |

| Table 4-1 | ADM1224 ID Address Space Listing       | 4-1  |

| Table 4-2 | ADM1224 I/O Address Space Listing      | 4-2  |

| Table 4-3 | Word Access Address Translation Table  | 4-3  |

| Table 4-4 | Byte Access Address Translation Table  | 4-4  |

| Table 4-5 | Data Register Description              | 4-6  |

|           | •                                      |      |

# **GLOSSARY**

[x:y] Bit-range designation (in descending decimal), where "x" is the most significant bit

down to "y", the least significant bit. (e.g. IPD[15:0] refers to the IPD bus where bit 15

is the most significant bit, bit 0 is the least significant bit, and there are 16 bits).

**Accuracy** ABSOLUTE: The error of an ADC at a given output code is the difference between the

theoretical and actual analog input voltages required to produce that code.

RELATIVE. The deviation of the analog value at any code from its theoretical value

after the full-scale range has been calibrated.

acquire The process of selecting and capturing an analog signal for the process of developing

its digital representation. The capturing operation is usually performed by a

sample/hold or track/hold amplifier.

active filter A signal filter that uses an amplifier with conventional passive filter elements to

provide a desired fixed or tunable pass or rejection characteristic.

Analog-to-Digital Converter; a device which translates continuous analog signals into

proportional discrete digital signals.

aliasing error (over-simplified) The unrecoverable error in converted data that occurs when sampling

an analog signal whose bandwidth is not limited (by a low-pass filter) to less than half of the sampling frequency to an amplitude of at least -72dB for a twelve bit ADC.

analog mux

Also known as an analog multiplexer, it provides switching of analog input signals to

allow use of a common analog-digital converter.

analog signal A nominally continuous electrical signal that varies in amplitude or frequency in

response to changes in physical phenomenon, such as sound, light, heat, position, or

pressure.

AREF Analog REFerence, common, or ground.

bipolar mode A configuration that an ADC uses to handle signal spans containing both positive and

negative signals. Usually it means offsetting half-scale to become analog zero, and accepting the resulting offset binary code or changing it to two's complement coding.

buffer amp

An operational amplifier used after a critical stage to isolate it from the effects of load

impedance variations in subsequent stages.

byte 8 contiguous bits on octal boundaries. (e.g. IPD[15:8], and IPD[7:0]).

byte-lane Byte position description. (e.g. IPD[15:8] is the "high" byte-lane, also defined as

"byte-lane ONE"; whereas IPD[7:0] is the "low" byte-lane, also defined as "byte-lane

ZERO").

**CAD** Computer-Aided Design.

**CAE** Computer Aided Engineering.

clipper-limiter A device whose output is a function of the instantaneous input amplitude for a range of

values lying between two predetermined limits but is approximately constant, at

another level, for input values above the range.

CMR Common-Mode Rejection. The ability of an amplifier to cancel a common-mode

signal while responding to an out-of-phase signal, often through variation of a ground

level.

CMRR Common-Mode Rejection Ratio is the ratio of gain for the differential or normal-mode,

signal to the gain for the common-mode signal.

CMS Common-Mode Signal. A signal applied equally to both ungrounded inputs of a

balanced amplifier stage or other differential device.

**conversion rate** The number of complete conversions an analog-to-digital converter can perform per

unit time, usually specified in conversions per second per channel.

**CRC** Cyclic Redundancy Check.

CVT Current Value Table consisting of twenty-four current value registers.

differential as in input; a circuit that rejects voltages that are the same at both (+ & -) input

terminals and amplifies the voltage difference between the two input terminals.

**DNL** Differential Nonlinearity (see nonlinearity).

**doublewide** An IPack module that is physically and electrically two side-by-side singlewide IPacks.

**EPLD** Erasable Programmable Logic Device.

**endoframe** Short pulse driven out the N STROBE logic signal line to the host carrier indicating

when channel #24 has just had its ADC and frame count information written to the

CVT; also internally increments the frame counter.

**ENOB** Effective Number Of Bits. For a sine wave, the signal-to-noise ratio can be expressed

in terms of the number of bits.

$ENOB = (SNR - 1.76) \div 6.02.$

**frame** One complete pass through all twenty-four channels.

frame time Time per frame =  $70 \mu s$ . The reciprocal of this is the sampling-rate per channel.

gain error The deviation of the actual difference between the first and last code transitions from

the ideal difference between the first and last code transitions.

**GRAYbus** Gray Code Engine bus (testpoints) designated as: GRAY[6:0].

**IAMP** Instrumentation Amplifier; differential-input, single-ended output. Usually is a closed-

loop fixed-gain amplifier, with very high input impedance, low drift, and high

common-mode rejection over a wide range of frequencies.

Id Drain current of MUX; usually in context with ON and OFF leakage current

specifications.

**Idiff** Differential, OFF-state output leakage current for differential multiplexers, where the

first channel experiences plus-full-scale on the non-inverting input and minus-full-scale on the inverting input, and the adjacent channel is driven with plus-full-scale on the

inverting input and minus-full-scale on the non-inverting input.

**ID PROM** Identification Programmable Read Only Memory, emulated within the EPLD providing

the required identification information about the IPack.

INL Integral Nonlinearity (see nonlinearity)

IndustryPack see IPack.

I/O Input/Output.

**IPAbus** IPack Address bus designated as: IPA[6:1].

**IPack** Business-card size mezzanine-type boards that provide general and special-purpose

input and output functions to and from their host carriers. An open industry standard defines the mechanical and electrical interface to the carrier board, which can be a bus

converter or a standalone, embedded host.

**IPDbus** IPack Data bus designated as: IPD[15:0].

Is Source current of MUX; usually in context with ON and OFF leakage current

specifications.

KHz KiloHertz, thousands of cycles per second.

LSB Least Significant Bit =  $20 \text{ Volts} \div 4096 = 4.8828 \text{ mVolts}$ .

lowpass filter A passive or active filter that transmits alternating current below a given cutoff

frequency and substantially attenuates all other currents.

monotonic a specification that guarantees no missing codes such that every code combination

appears in an increasing sequence as the analog input level is increased.

MTBF Mean Time Between Failures.

multiplexer see Analog Mux.

MUXAbus MUltipleXer 'A' (address) bus, designated as: MUXA[2:0]. These three signals

provide the address that define which of the eight channels, from  $1 \rightarrow 8$ , that are

presented to its subsequent differential amplifier and ADC.

MUXBbus MultipleXer 'B' (address) bus, designated as: MUXB[2:0]. These three signals

provide the address that define which of the eight channels, from  $9 \rightarrow 16$ , that are

presented to its subsequent differential amplifier and ADC.

MUXCbus MUltipleXer 'C'(address) bus, designated as: MUXC[2:0]. These three signals provide

the address that define which of the eight channels, from  $17 \rightarrow 24$ , that are presented to

its subsequent differential amplifier and ADC.

**nA** nanoamperes, or  $10^n$  Amps, where "n" = -9.

**nonlinearity** DIFFERENTIAL: An ideal ADC provides code transitions that are 1LSB apart.

Differential nonlinearity is the maximum deviation, expressed in LSBs, from this ideal

value.

INTEGRAL: The worst case deviation of a code from a best-fit straight line between

"zero" and "full scale".

**ns** nanoseconds, or  $10^n$  Seconds, where "n" = -9.

offset error The deviation of the actual MSB code change to the ideal of ½LSB below analog

common. See "2's complement", below.

$\rho$ C picoCoulombs, or  $10^n$  Coulombs, where "n" = -12, unit of electrical charge

PSRR Power Supply Rejection Ratio. Often referred to in amplifier specifications, it is the

equivalent change at the input due to variations in the power supply. For an amplifier with a gain of 1, a PSRR of 10mV/V will provide 10mVolts of change on the output

for every volt of change on the power supply.

Qinj Charge Injection; also charge transfer. In multiplexers, this is the transfer of charge

(energy) from the switch driver to the output capacitance after a switch turns off.

**QSOP** Quarter-sized Small Outline (surface mount) Packages.

**RDSon** A Multiplexer's series ON-channel resistance measured between the source ("S") input

and the drain ("D") output terminals under specified conditions.

**SADDbus** SRAM's ADDress bus, designated as: SADD[4:0]. These five address lines provide the

proper location addressing function for reads from and writes to the SRAM, which is

the CVT.

**SAR** Successive Approximation (shift) Register type of ADC.

SNR The measured Signal-to-Noise Ratio at the output of the ADC, usually including

harmonic distortions, logarithmically expressed in decibels. The ideal is:

SNR = (6.02N - 1.76) dB, where N = bits of resolution.

settling time Also known as the transient response time, the settling time of an ADC is the time

required for the ADC to settle to rated accuracy after the application of a full-scale step

input in either direction.

single-ended as in input; unbalanced and not differential, and one side of the transmission line or

circuit is usually referenced to analog common or ground.

singlewide The most common size (and smallest) physical IPack size (3.9" by 1.8").

span The full scale analog input ranged; =  $\pm 10.000$  Volts.

**SRAMDbus** Static Random Access Memory Data bus designated as: SRAMD[15:0]. The nibble

consisting of SRAMD[15:12] contains the frame count information while the 1½ bytes

consisting of SRAMD[11:0] contains the ADC information.

**switching time** The time required for a multiplexer to switch and slew from one analog input channel

to another analog input with a full-scale differential between inputs with a high

impedance output load.

2's complement Output coding:  $800hex @ -10.000 \text{ Volts input} \rightarrow \text{FFF}hex @ \approx -0.005 \text{ Volts input};$

$000hex @ 0.000 \text{ Volts input} \rightarrow 7FFhex @ +9.995 \text{ Volts input}.$

$\mu$ S microseconds, or  $10^n$  where "n" = -6.

VHDL Very High speed integrated circuit Hardware Description Language, used, with

synthesis, for EPLD logic development.

VIN+# The non-inverting input for differential inputs applied to the ADM1224F IPack; also

the only input for single-ended inputs.  $\# \equiv 1 \rightarrow 24$  channel numbers.

VIN-# The inverting input for differential inputs; or ground (optionally on-board jumpered)

for single-ended inputs.  $\# \equiv 1 \rightarrow 24$  channel numbers.

# 1.0 INTRODUCTION

# 1.1 Purpose

This is a reference manual for SYSTRAN's 24-channel, 12-bit, ±10 Volt differential-ended-input, Multiplexed Analog→Digital Converter IndustryPack (also called IPack) board, referred to in this manual as the ADM1224F (part number BHAS-ADM1224F).

Figure 1-1 ADM1224F Board

# 1.2 Scope

This reference manual covers the physical and operational description of the ADM1224F, both from hardware and software perspectives. This manual also contains detailed technical information about the ADM1224F's performance characteristics, and some typical applications. The reader should have a general understanding of computer processing, software and/or hardware applications experience, and a working knowledge of using IPacks on their carrier(s) of choice. Citation of equipment from other vendors within this document does not constitute an endorsement of their product(s).

#### 1.3 Overview

The ADM1224F is a singlewide IPack board, conforming both mechanically and electrically to the *IndustryPack Logic Interface Specification, revision 0.7.1*. For a typical (non-SYSTRAN) IPack carrier that holds four IPacks, the ADM1224F can provide up to 96 channels of high-performance ADCs in a single slot on a computer bus backplane, or be mixed with other IPacks for a more customized, modular I/O system solution. Using SYSTRAN's carriers, up to 120 channels of ADCs may be installed in a single VME slot, or (still more) 144 in a single ISA slot.

The ADM1224F is designed to maintain the highest possible accuracy and performance characteristics by minimizing analog errors in the design by using the best (yet, reasonably affordable) components for the tasks to be accomplished. The board level accuracy is also maximized by the inclusion of good ground plane and power filtering design, and by the exclusion of on-board range selectors, gain blocks, offset circuits, anti-aliasing filters, and other special-purpose circuits, thereby providing the user more accuracy for the 12-bits of resolution in the captured and converted data.

#### 1.3.1 The Name

The product name of ADM1224F consists of several descriptive components. The "AD" portion indicates its primary function of performing analog—digital conversions. The "M" indicates that this board has a multiplexed, analog front-end design. This means that several channels share an analog—digital converter, with their channel-switching function being implemented with an analog multiplexer. If there had been dedicated converters per channel, the leading characters would have been "ADC", as they are on the ADC128F1 IPack. The next "12" field indicates the number of bits of resolution (not accuracy). The next "24" indicates how many analog input channels are available. The last "F" indicates that the input range is fixed and that the span is ±10 Volts. There is no embedded designator for the significant feature of differential-ended-inputs.

#### 1.3.2 Features

- Twenty-four multiplexed channels of switched capacitor SAR-based ADCs with all channels sampling and converting at a free-run and completely determinsitic rate of over 14,285 samples/second/channel, with a board total of over 342,857 samples/second.

- All samples provide 12-bits of resolution, and the ADC used has an impressive 11.33 Effective Number Of Bits (not accuracy).

- All twenty-four channels feature true, differential-ended-inputs spanning ±10volts full scale, feeding (gain = 1) instrumentation amplifiers.

- Automatic power-up of all channels sampling and updating the current value table (CVT).

- The CVT provides no-wait, read-on-the-fly IPack accesses to the latest ADC data.

- 4-bit Frame counter data on top of ADC data in CVT, incremented per pass of 24 channels.

- End-of-frame pulse provided via "N\_STROBE" signal on Logic Connector per pass of 24 channels.

- Three sets of multiplexers, instrumentation amplifiers, and ADCs time staggered; 1 per 8 channels.

- The ADCs' relative and differential nonlinearities are guaranteed to ±1 LSB (max.).

- Precision +2.500 Volt ADCs' sampling reference optionally sampled as channel #24.

- Analog (ground) reference jumpers to "inverting" inputs on-board for singleended inputs for all channels.

- All (on-board filtered) power is obtained from the host carrier.

- Gray Code sequence engines used (where possible) for minimum on-board generated digital noise.

- Embedded analog ground plane for "quiet" operations.

• Theoretical output data coding is two's complement: 800 hex @ -10.000 Volts input → FFF hex @ ≈-0.005 Volts input; 000 hex @ 0.000volts input → 7FF hex @ +9.995 Volts input.

# 1.4 Specifications

#### **MECHANICAL: SINGLEWIDE IPACK**

- Measurements: 1.800" x 3.900" x 0.303" (connectors, above board)

4.572 x 9.906 x 0.770 cm

- NOTE: 0.234" (0.595 cm) maximum component (non-connector) height

- Weight: 1.104 oz., 31.3 grams

- Board thickness: 0.062" (0.157 cm) nominally, (4 layer)

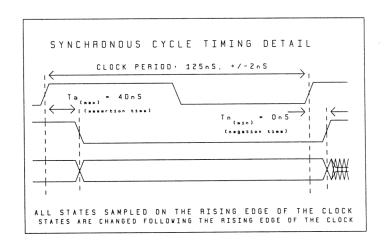

# PROTOCOL: SINGLEWIDE IPACK TRANSFERS

- 8 MHz clock rate

- No WAIT cycles inserted on any valid transfer types

- HOLD cycles supported on all valid transfer types supported

- Complete (no partial) address decoding

- Twenty-four I/O locations:

- · 16-bit read-only, byte lane selects ignored

- No writes

- ADC data = IPD[11:0]

- Frame Counter data = IPD[15:12]

- Maximum read rate: 4 MTransfers/second, sustained

- No Acknowledgement for IPA≥18 hex or for any write attempts

- Twelve ID locations:

- 16-bit read-only, byte lane selects ignored

- No writes

- · ID data = IPD[7:0]

- $\cdot$  Zero-fill = IPD[15:8]

- SYSTRAN's manufacturer's ID = 45  $hex = \mathbb{E} ASCII$

- ADM1224F's model number = 6F hex = o ASCII

- · Cyclic Redundancy Check value =  $\mathbf{CD}$  hex

- Maximum read rate: 4 MTransfers/second, sustained

- No Acknowledgement for IPA≥0C hex or for any write attempts

- Memory transfers: not supported; no acknowledgements

- Interrupt Vector transfers: not supported; no acknowledgements

- Interrupt requests: none generated

- DMA activity: none supported

- End-of-frame: ≈63 ns pulse every 70 µs at N\_STROBE on Logic Connector

#### POWER-UP DEFAULT CONDITION

- No accesses permitted or acknowledged during RESET

- All control logic frozen and all counters zeroed during RESET

- Data is not accurate to specification until after ≈25 ms following application of power

- First ADC data entries for channels #1, #9 and #17 following the negation of RESET are indeterminant; valid entries for these channels completed 78.750 μs after the negation of RESET.

#### **AS-SHIPPED CONDITION**

- All 24 channels configured as single-ended inputs

- Channel #24 connected to the I/O Connnector; not to the voltage reference

#### POWER REQUIREMENTS

- Carrier power:

- +5 Vdc @ 114 mA (all inputs grounded)

- +12 Vdc @ 9.10 mA (all inputs grounded)

- -12 Vdc @ 7.79 mA (all inputs grounded)

- · Total: 204 mW

- I/O Connector:

- Analog (ground) reference common to all analog circuitry; tied to the digital ground on the carrier side of the Logic Connector only (pins 25 and 50)

- No other I/O Connector power requirements exist

#### PERFORMANCE CHARACTERISTICS

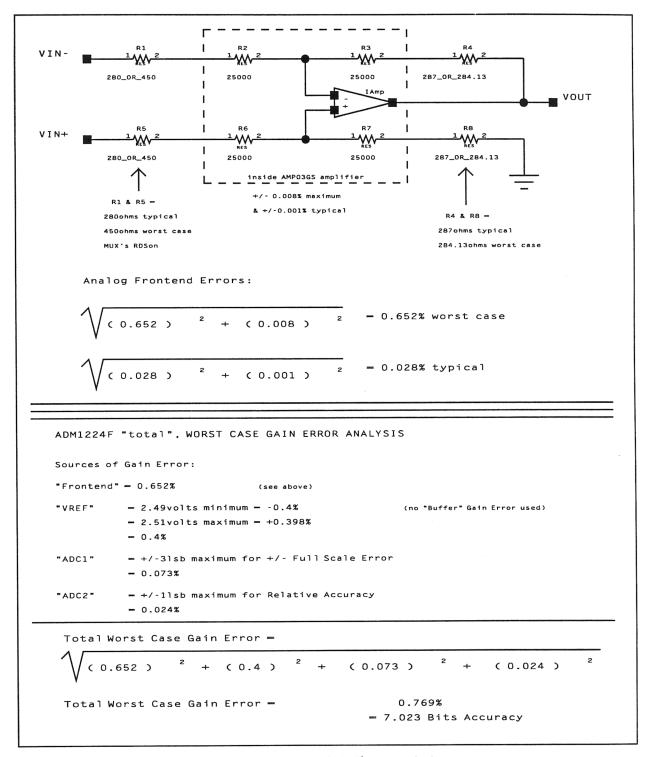

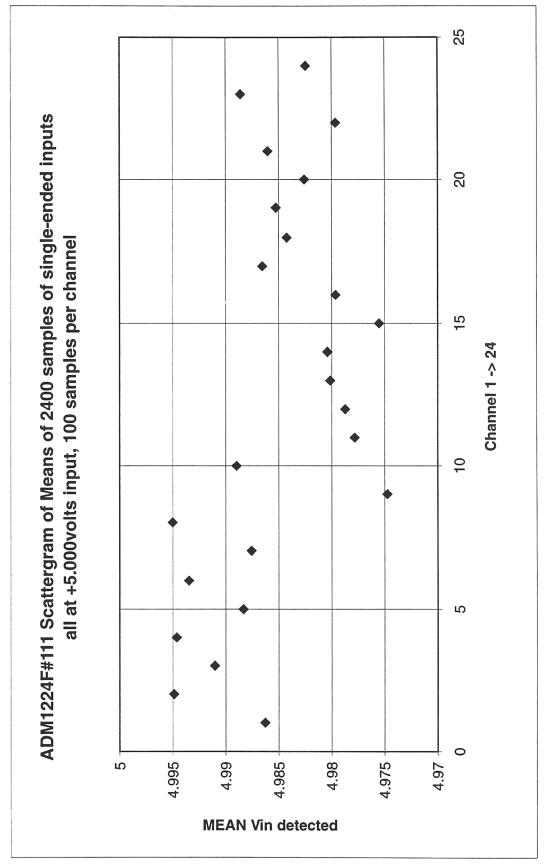

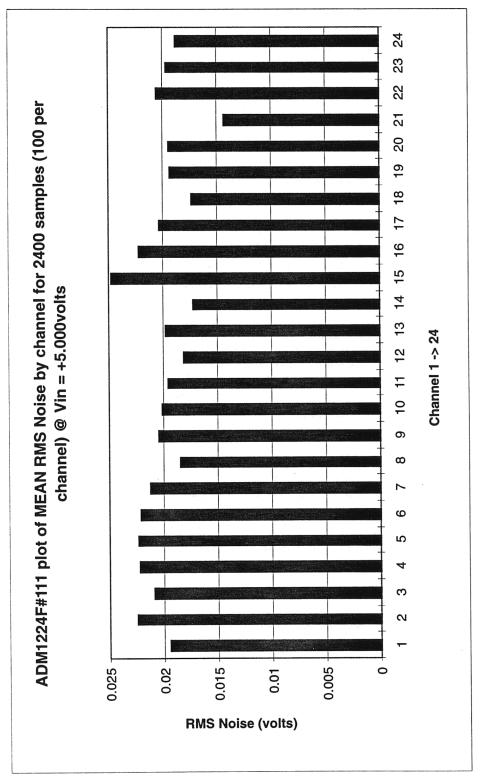

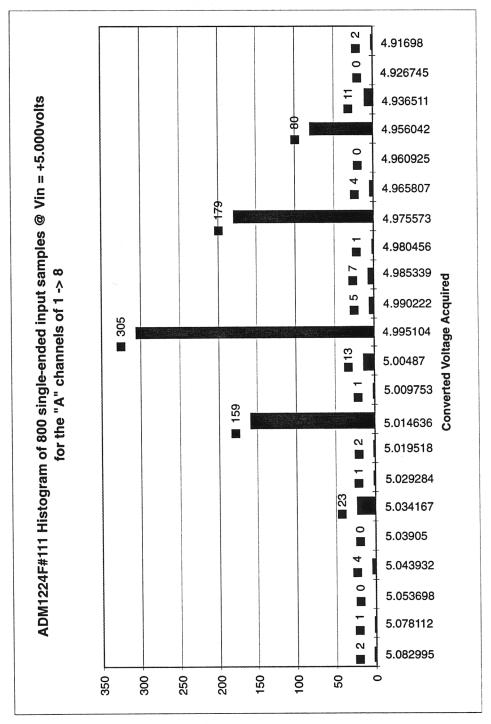

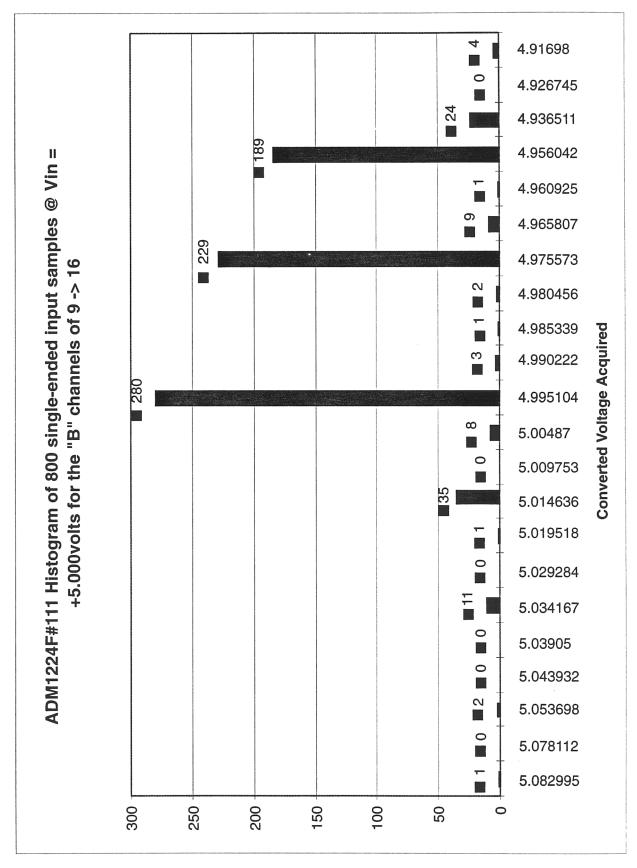

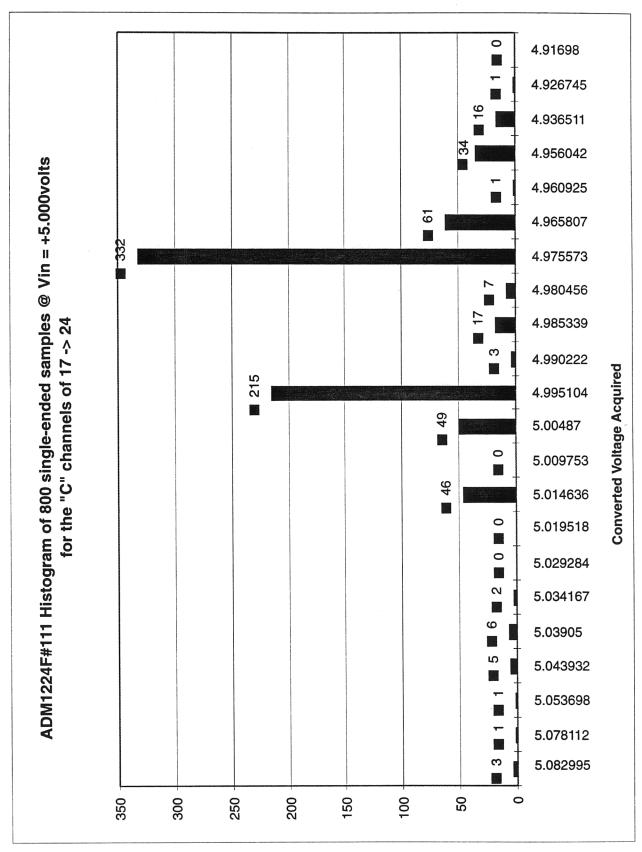

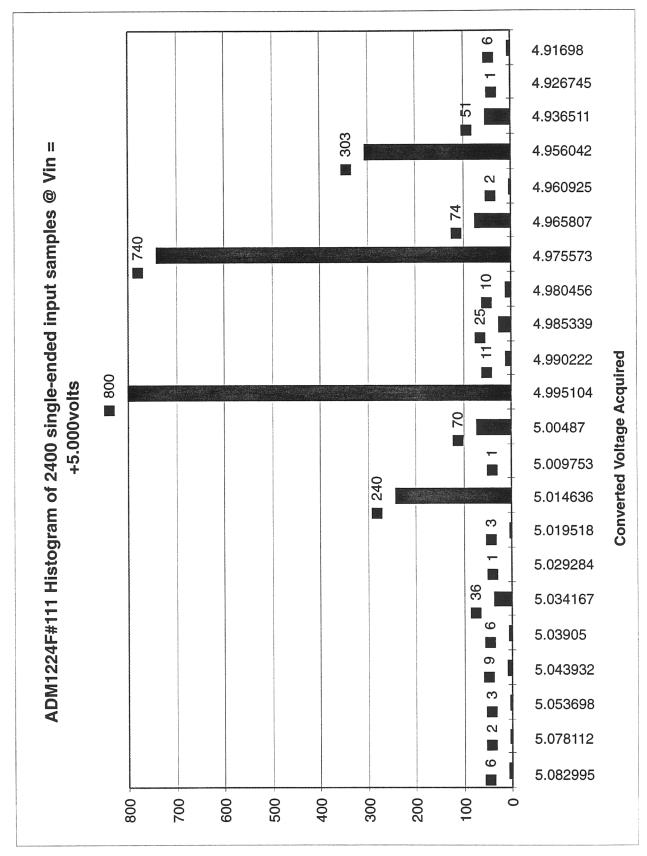

- Accuracy: Refer to section 5.0 on Performance (histograms & scattergrams)

- Timing: Refer to section 5.0 on Performance (analyzer figures)

- Input Impedance (per channel):

- Vin+ (Vin- grounded): 50594  $\Omega$ , nominal (single-ended configuration)

- · Vin- (Vin+ grounded): 25297  $\Omega$ , nominal (inverting single-ended configuration)

- Differential-ended: 50594  $\Omega$ , nominal

- MUX (analog):

- · Analog signal range ±12.000 Volts

- RDSon = 280  $\Omega$  (typical @ 25°C), 400  $\Omega$  (maximum, over temperature)

- · RDSon match = 5% (typical)

- $L_S = 0.02 \text{ nA (OFF, typical input leakage)}, 50 \text{ nA (maximum, over temperature)}$

- ID = 0.04 nA (OFF, typical input leakage), 100 nA (maximum, over temperature)

- $I_D = 0.04 \text{ nA}$  (ON, typical input leakage), 100 nA (maximum, over temperature)

- ·  $I_{DIFF} = 25 \text{ nA (maximum, over temperature)}$

- · QINJ =  $4\rho C$  (typical @  $25^{\circ}C$ )

- Maximum continuous current, source or drain, = 20 mA (must be externally limited if overvoltage conditions are possible)

- IAMP (analog):

- Offset voltage = 25  $\mu$ V (typical @ 25°C),  $\pm$ 2000  $\mu$ V (maximum, over temperature)

- Gain error = 0.001% (typical, full scale, @ 25°C), 0.02% (maximum, full scale, over temperature)

- · CMR = 80dB (minimum @ 25°C), 90dB (typical, over temperature)

- Slew Rate = 6 V/ $\mu$ s (minimum @ 25°C), 9.5V/ $\mu$ s (typical, over temperature)

- PSRR =  $0.7\mu\text{V/V}$  (typical @ 25°C), 15  $\mu\text{V/V}$  (maximum, over temperature)

- ADCs (analog):

- · Signal-to-noise (distortion) Ratio = 70 dB minimum for 10 KHz Sine wave input

- Effective Number of Bits = 11.33

- Total Harmonic Distortion = -80 dB maximum for 10 KHz Sine wave input

- Peak Harmonic Distortion = -80 dB maximum for 10 KHz Sine wave input

- Intermodulation Distortion = -80 dB maximum for both 2nd and 3rd order terms (Fa=9 KHz and Fb=9.5 KHz)

- · Minimum resolution = 12 bits with no missing codes, guaranteed

- Relative accuracy =  $\pm \frac{1}{2}$  LSB (typical),  $\pm 1$  LSB (maximum)

- Differential nonlinearity =  $\pm 1$  LSB (typical and maximum)

- Positive full-scale error =  $\pm 1\frac{1}{2}$  LSB (typical),  $\pm 3$  LSB (maximum)

- Bipolar zero (offset) error =  $\pm 2$  LSB (typical),  $\pm 4$  LSB (maximum)

- Negative full-scale error =  $\pm 1\frac{1}{2}$  LSB (typical),  $\pm 3$  LSB (maximum)

- Input voltage range =  $\pm 10$  Volts referenced to "AREF"

- Input resistance = 33 K $\Omega$  (typical), 16 K $\Omega$  (minimum)

- · 1 LSB = 20 Volts  $\div$  4096  $\approx$  4.88 mV

- REFERENCE (analog):

- Output voltage =  $\pm 2.500$ ,  $\pm 0.010$  Volts (maximum, over temperature)

- Output voltage drift = 10 ppm/°C (typical), 25 ppm/°C (maximum) = 1.75 mV (typical), 4.375 mV (maximum, over temperature)

- Output settling time = 25 ms to within 250  $\mu$ V of final value after application of power

# **ABSOLUTE MAXIMUM VOLTAGES ‡:**

- Carrier power supplies:

- +5 Volt supply with respect to ground: -0.3 Volts (minimum), +7.0 Volts (maximum)

- +12 Volt supply with respect to ground:  $\leq$  +18.0 Volts

- -12 Volt supply with respect to ground:  $\geq$  -18.0 Volts

- VIN± input range: ±17 Volts (maximum if ±18.0 Volts is supplied by the carrier) ±12 Volts (maximum if ±12.0 Volts is supplied by the carrier)

- CMS =  $\pm 10$ volts (maximum, over temperature)

- \$\pm\$ Stresses above those listed may cause permanent damage to the components on the ADM1224F. Operating the ADM1224F beyond the recommended ratings for extended periods of time may affect reliability.

#### **MAXIMUM INPUT BANDWIDTH:**

- No signal energy  $\geq$  -72 dB in amplitude at frequencies  $\geq$  7142 Hz to prevent aliasing errors (for single sampling per frame)

- Signals can be supercommutated using even "time" spacing techniques to acquire higher bandwidth signals, to a limit of a maximum frequency of 171.428 KHz (all 24 channels sampling a single signal source; input impedance ≈ 16,865 Ω)

#### RECOMMENDED OPERATING CONDITIONS:

- Carrier Supply Voltages:

- +5.00, +0.25/-0.125 Volts, 50 mV maximum peak-to-peak ripple and noise

- +12.0, +0.60/-0.36 Volts, 50 mV maximum peak-to-peak ripple and noise

- -12.0, -0.60/+0.36 Volts, 50 mV maximum peak-to-peak ripple and noise

- Input Signals:

- ±10.000 Volts

- · 7142 Hz (maximum frequency, fundamental and harmonics)

- Recommended carriers: (for "quiet" operations)

- SYSTRAN's VME3SC2 for VME-3U

- SYSTRAN's VMESC5 for VME-6U

- SYSTRAN's ISASC6 for ISA (P.C.'s)

#### **ENVIRONMENTAL SPECIFICATIONS:**

- Temperature:

- Operating:  $0^{\circ}\text{C} \rightarrow +70^{\circ}\text{C}$

- Storage (no bias):  $-40^{\circ}\text{C} \rightarrow +85^{\circ}\text{C}$

- Humidity (noncondensing):  $5\% \rightarrow 95\%$

- Vibration (operating): 10 G's RMS, 20 Hz → 2000 Hz, random (no jumper shunts installed)

- Shock (operating): 50 G's maximum, all axes (no jumper shunts installed)

- Altitude (operating): 10,000′, maximum

# **MEAN TIME BETWEEN FAILURE (MTBF):**

• 1,031,885 hours per MIL-HDBK-217F

#### 1.5 Related Products

Software: 'C' library and OS-9 device driver routines and documentation. ATE: Automatic Test Equipment Software/Hardware Package, with CASE based design/analysis.

#### 1.6 Related Publications

- *IndustryPack Logic Interface Specification Synopsis* published by SYSTRAN Corp.(This synopsis is included in this document as Appendix A).

- SYSTRAN I/O Products Technical Note #2001 entitled Programmed Transfer Rate Analysis of the IndustryPack Bus Onboard the Motorola MVME162 Controller (Doc. A-T-ST-IPAC2001-A-0-A1)

- IndustryPack Logic Interface Specification Revision 0.7.1 published by GreenSpring Computers, Inc. 1204 O'Brien Drive, Menlo Park, CA 94025.

### 1.7 Ordering Process

If you wish to learn more about SYSTRAN products or to place an order, the following contacts are available:

- Phone: (513) 252-5601

- E-mail address: info@systran.com

- World Wide Web address: http://www.systran.com/

#### 1.8 Technical Support

Technical documentation provided with the product discusses the technology, its performance characteristics, and some typical applications. It includes tutorial material, with comprehensive support information, designed to answer any technical questions that might arise concerning the use of this product. SYSTRAN also publishes and distributes technical briefs and application notes that cover a wide assortment of topics. The applications selected are derived from real scenarios, but do not cover all possible circumstances.

Direct any programming questions, any concerns about the functional-fit of this product for your particular application, or any questions not satisfactorily answered by this document, to the factory at (513)252-5601, or send an E-Mail message to **support@systran.com** for additional assistance. Our goal is to help solve your problem.

Refer to Section 7.0 for warranty and repair information.

### 1.9 Reliability

SYSTRAN Corporate policy is to provide the highest-quality products in support of a customer's needs. In addition to the physical product, the company provides documentation, sales and marketing support, hardware and software technical support, and timely product delivery. The SYSTRAN commitment to quality begins with product concept, and continues after receipt of the purchased product.

An integral part of SYSTRAN quality and reliability goals is customer feedback. Customers are encouraged to contact the factory with any questions or suggestions regarding unique quality requirements, or to obtain additional information about our programs. SYSTRAN's commitment to customers includes, but is not limited to:

- Professional and quick response to customer problems utilizing SYSTRAN's extensive resources.

- Incorporation of established procedures for product design, test, and production operations, with documented milestones. Procedures are constantly reviewed and improved, ensuring the highest possible quality.

SYSTRAN provides products and services that meet or exceed the best expectations of our customers.

- All products are tested using an Automatic Test Equipment system, with samplings for all product types taken through extended testing scenarios that include stress testing for voltage and temperature ranges beyond specifications.

- All products receive a predictive reliability rating based upon a calculated MTBF utilizing the MIL-HDBK-217F. Field failures are continuously logged and evaluated for potential failure modes and trends.

- Other environmental parameters are guaranteed by design, and not tested.

- Design reliability is ensured by methodology (top-down CAE design, VHDL, synthesis, extensive all-cases simulation, ALPHA build and test, and BETA testing if required) with full concurrent engineering practices throughout.

# 2.0 DESCRIPTION

**NOTE**: The IPack signal references, transfer and cycle types discussed in this document are explained in detail in the *IndustryPack Logic Interface Specification Synopsis* included as Appendix A.

# 2.1 Simplified Block Diagram

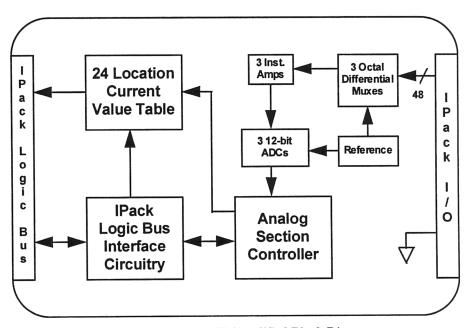

Figure 2-1 presents the first of three levels of block diagrams for the ADM1224F IPack.

Figure 2-1 ADM1224F Simplified Block Diagram

# 2.1.1 Simplified Block Descriptions

#### IPACK LOGIC BUS INTERFACE CIRCUITRY

On the left side of the diagram is the IPack Logic Bus connector through which all transfers between the IPack Carrier and the ADM1224F's registers and data sources are conducted. The block labeled "IPack Logic Bus Interface Circuitry" contains all of the board level access logic that descriminates between valid and invalid access attempts by the carrier, provides the ID PROM data for identification queries, develops the arbitration and access control logic for the SRAM-based current value table, coordinates activities with the analog section controller, and executes all of the IPack transfer sequence/control and data bus interface operations.

#### 24 LOCATION CURRENT VALUE TABLE

This block consists of a pair of Static Random Access Memory (SRAM) devices that function as the Current Value Table (CVT). This table consists of 24 consecutive, 16-bit wide locations that contain the latest (most current) conversion results for all 24 input

channels. From the IPack carrier's perspective, these are read-only, 16-bit only, I/O locations that present all ADC & Frame Count data requests with no wait cycles inserted. The analog section controller coordinates with the IPack Logic Bus Interface Circuitry to perform orderly, error-free deposition of ADC data into the CVT.

#### ANALOG SECTION CONTROLLER

This block consists of a free-running sequential state machine that controls all of the analog signal selection and conversion activities, data retrieval and serial-to-parallel conversion operations, as well as the writes to the CVT of the conversion results with their appended frame count information. Implied, but not explicitly shown, is a significant connection between the analog section controller and the analog multiplexers.

#### REFERENCE

The voltage reference is a high-accuracy, buffered source that is the ADCs' conversion analog reference point. This signal is also optionally available as a direct connection into channel #24 for system applications that require continuous monitoring of the voltage reference (hence the connection of the reference to the analog multiplexers box).

#### **3 OCTAL DIFFERENTIAL MUXES**

This block depicts the analog signal multiplexers that are configured as three separate eight-to-one-by-two analog signal multiplexers whose channel selections are controlled by the analog section controller's state machine. The input channels are grouped as channels  $1 \rightarrow 8$ ,  $9 \rightarrow 16$ , and  $17 \rightarrow 24$ .

#### 3 INST. AMPS

The differential outputs of the three analog multiplexers drive three separate instrumentation amplifiers that convert the inputs to single-ended, buffered signals for the ADCs. When inputs through the multiplexers are configured as differential-ended inputs, these instrumentation amplifiers remove common-mode (noise, offset errors, etc.) signals.

#### **3 12-BIT ADCS**

The single-ended outputs of the three instrumentation amplifiers drive the analog inputs to the three 12-bit ADCs. These converters, and their analog signal multiplexers, are time-stagger-controlled by the analog section controller to provide the highest throughput possible with maximum signal settling time (for the highest accuracy possible). The data is retrieved from the ADCs in serial format for eventual deposition of the data into the CVT.

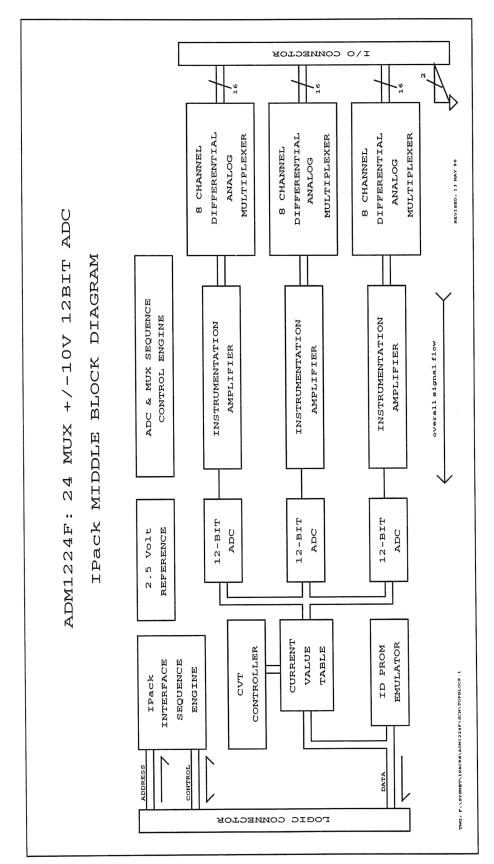

Figure 2-2 ADM1224F Middle Block Diagram

### 2.2 Middle Block Diagram

Figure 2-2 presents the second, mid-level block diagram of the ADM1224F IPack.

### 2.2.1 Middle Block Descriptions

#### LOGIC CONNECTOR

On the left side of the diagram is the IPack Logic Bus connection between the ADM1224F and its carrier. The three groups of information signals (not including power and grounds) perform the interface duties. There are six inbound address signals that provide descriminatory information beyond the select (control) signals, accessing both unique ID and I/O data from the ADM1224F's data sources. The normally bi-directional 16-bit data bus is a simplex read-only bus on the ADM1224F since there are only two types of read accesses possible. The normal control lines consist of four select signals, a read/write control line, reset, clock, and the one outbound acknowledgement signal.

#### ID PROM EMULATOR

This function, included in the IPack Logic Bus Interface Circuitry block of Figure 2-1, generates the necessary data patterns to emulate an ID PROM during Identification (ID) Transfers from the IPack to its carrier. Emulating the ID information within the EPLD, instead of providing the data from an actual PROM, is possible due to the never changing information presented by it. This technique saves board space, lowers costs, improves reliability, and enables this IPack to provide read accesses to this information without the insertion of wait cycles.

#### **CURRENT VALUE TABLE & CONTROLLER**

These two blocks, included in the 24-Location Current Value Table block of Figure 2-1, separate these functions into their respective physical components. The table, itself, is actually a pair of 32 KB SRAM devices configured as 32 KWord locations of write (from the ADCs) and read (to the carrier) locations. Only the first 24 locations are used. This registration technique is several orders of magnitude less expensive than any other technique for storing this much information in this small of area.

The CVT controller is contained within the EPLD. Not shown in figure 2-2 is the tight linkage between the CVT Controller and the ADC & MUX Sequence Control Engine, which requests to perform writes to the CVT, and the IPack Interface Sequence Engine, which requests to perform reads from the CVT. The CVT controller is basically the SRAM's read/write arbitor and timing controller.

#### **ADC & MUX SEQUENCE CONTROL ENGINE**

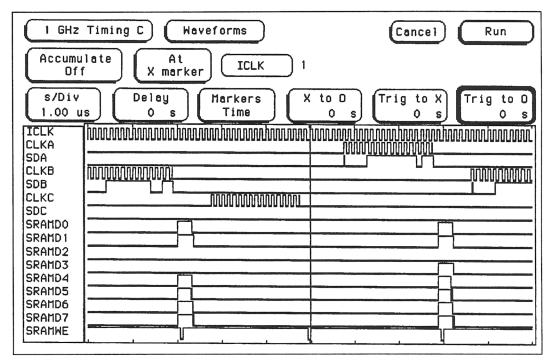

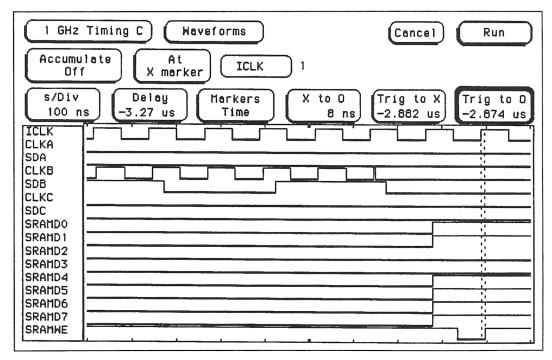

This block defines the primary functionality of that presented as the analog section controller of Figure 2-1. The core of this engine is a seventy state GRAY CODE counter that is continuously driven by the 8 MHz ICLK from the carrier. It provides orderly sequencing of signal selecting, signal tracking and holding, analog-to-digital converting, retrieving results, serial-to-parallel converting, and assistance in the eventual storing of results.

#### **ANALOG CIRCUITRY**

The remainder of Figure 2-2 presents the three sets of analog circuits. For each of eight channels there is a dedicated ADC, which is driven by a dedicated, gain = 1, instrumentation amplifier, which is fed signals from its own 8 channel, differential input and differential output full-scale analog multiplexer. This section of Figure 2-2 expands that which was presented in the upper right corner of Figure 2-1. This diagram still lacks

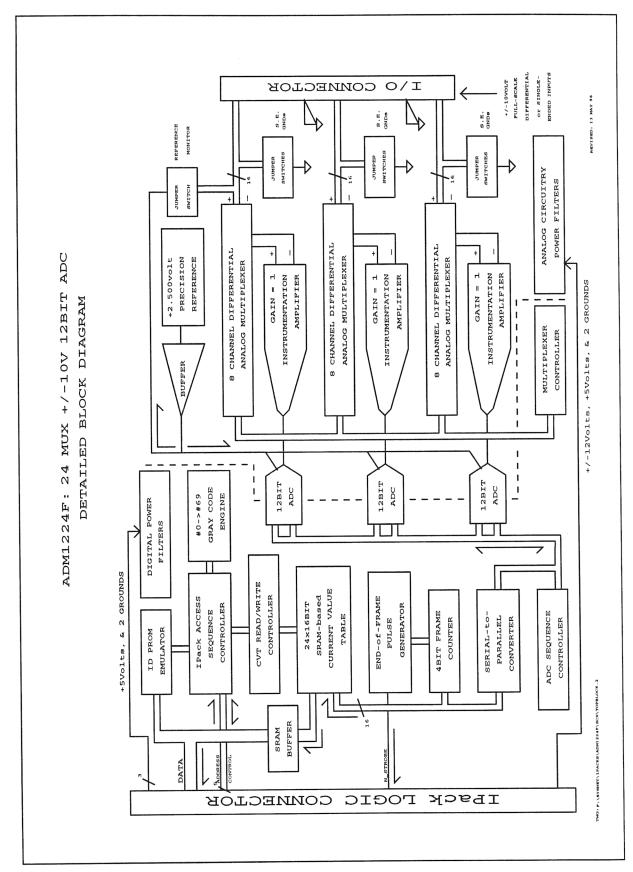

Figure 2-3 ADM1224F Detailed Block Diagram

the details necessary to understand all of the features and functions of the ADM1224F IPack.

### 2.3 Detailed Block Diagram

Figure 2-3 presents the detailed block diagram of the ADM1224F IPack.

### 2.3.1 Detailed Block Descriptions

### 2.3.1.1 Remaining Digital Blocks

Most of the digital logic (left half of Figure 2-3) has been discussed in the previous figures of this section. The following text provides additional information for a few blocks that Figure 2-3 presents.

#### SRAM BUFFER

This block presents a simple hexadecimal tristatable gate that couples the SRAM's data bus to the IPDbus during CVT read operations. It provides both isolation of buses and extra drive capabilities.

#### SERIAL-TO-PARALLEL CONVERTER

As mentioned previously, the three ADCs are serial interface devices. All three share a single, 12-bit, serial-to-parallel converter that captures the digitized data in round-robbin fashion. As will be seen in section 2.6, Table 2-1 (page 2-15) the data stream from the ADCs is actually 16-bits in length. The leading nibble of zeroes is discarded. Once the 12 bits of data is assembled in parallel format, the current frame-count value is appended at the highest nibble location, and the 16-bit result is deposited into the current value table by the CVT controller.

#### **4-BIT FRAME COUNTER**

A "frame" is defined, for this application, as one complete pass (channel #1 through channel #24) through all 24 channels. The frame counter is provided to enable the user to ascertain an accurate time relationship between the samplings of various channels in any order desired, including at rates slower than the rate at which new data is deposited into the CVT from the ADCs. As with most counters used on the ADM1224F, the frame counter is implemented as a free-running GRAY CODE sequencer, primarily to minimize board level noise (*only one bit changes at a time*). The "frame" count is incremented every 70.0000  $\mu$ s,  $\equiv$  once per pass through all 24 channels. The sequence, in hexadecimal, is:

The entire frame count sequence repeats itself every 1.12 ms (70  $\mu$ s per frame times 16 frames).

#### **END-OF-FRAME PULSE GENERATOR**

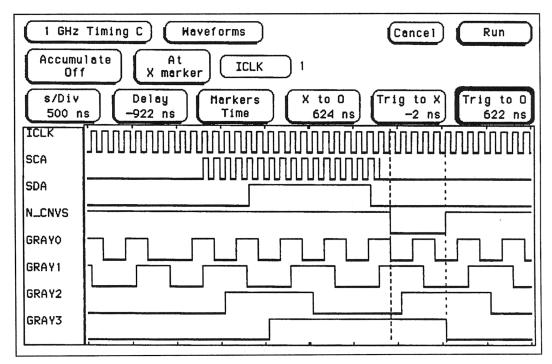

Every time the frame counter is incremented, a short, ½-ICLK-cycle-width pulse is generated. This low-going pulse occurs every 70 μs on the logic connector's N\_STROBE signal line. It can be used for system signalling and synchronization purposes via the carrier's "strobe" connections. One typical use is that of generating an interrupt with the resultant ISR fetching all 24 samples from the CVT.

**NOTE**: This signal is NOT buffered. Be careful about loading on this line if it is used.

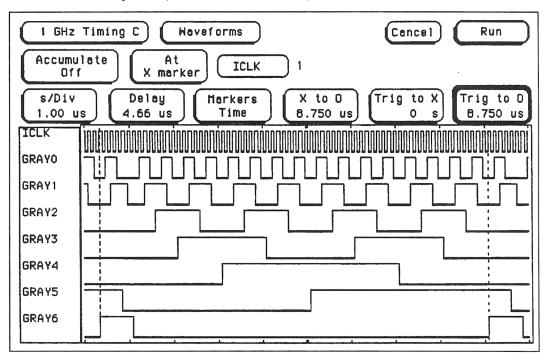

#### #0 $\rightarrow$ #69 GRAY CODE ENGINE

This particular counter is the core of all activity on the ADM1224F IPack. It is a modified GRAY CODE sequence engine. A minimum of 69 counts were necessary to accomplish all of the control and data retrieval activities. A full-sweep GRAY CODE engine would naturally include 128 counts to encompass the minimum count of 69. A modification in the single-bit changes near the end of the minimum of 69 counts, and the addition of one count to accomplish single-bit changes only, resulted in the 70-state machine design. The non-standard, hexadecimal sequence occurs during the sequence of:

$$62 \rightarrow 42 \rightarrow 40 \rightarrow 00$$

instead of  $62 \rightarrow 66 \rightarrow 67 \rightarrow 65 \rightarrow \dots 80 \rightarrow 00$ .

At one count per ICLK (125 ns per cycle), it takes 8.750 µs per pass through the engine, with eight passes through the engine per frame. Each pass through the engine controls the acquisition and data retrieval processes for one channel each for the three different analog and acquisition paths. The sequencing and associated activities will be covered in greater detail in sections 2.5 and 2.6. For now, it is sufficient to say that for any given pass through this engine, the same multiplexer value is applied to all three analog paths for the conversion process. If the first pass through the engine provides conversion processing for channels 1, 9, and 17; then the fourth pass will provide conversion processing for channels 4, 12, and 20; etc. This topic will be covered in greater detail in sections 2.5 and 2.6.

# 2.3.1.2 REMAINING ANALOG BLOCKS

Most of the analog circuitry (right half of Figure 2-3) has been discussed in the previous figures of this section. The Following text provides additional information for a few new blocks presented by Figure 2-3.

### **BUFFER (FOR THE REFERENCE)**

This particular (triangular) block is a voltage follower buffer used to provide sufficient drive capability for generating the +2.500 V reference for the three ADCs, and for driving the channel #24 input if that option is exercised.

### **JUMPER SWITCH (REFERENCE MONITOR)**

This is a shunt jumper switch that provides the option of monitoring the  $\pm 2.500$  V ADC reference voltage (defined as VREF = Voltage REFerence) for conversion purposes as channel #24 in place of that which would normally be supplied as channel #24 from the I/O connector. It is also possible to couple the buffered reference voltage as an output to the I/O connector if the need exists. This is slightly risky since the ADCs' reference will then be exposed to all noise sources that may exist at the I/O connector and beyond.

# **JUMPER SWITCHES (S.E. GNDS)**

These blocks represent three groups of eight shunt jumper switches, one group per multiplexer. Each switch provides the user the ability to short the inverting differential-ended input to the analog ground reference (AREF) on a per-channel basis for single-ended input applications. It is possible to convert inverted signals using the ADM1224F by driving the desired signal into the inverting input while grounding the non-inverting input. This application, of course, mandates the removal of these single-ended grounding

shunts for these channels. An example of this would be the case where an analog input swings from  $0.000 \text{ V} \rightarrow -10.000 \text{ V}$  but the application needs the data to be represented as if it were changing from  $0.000 \text{ V} \rightarrow +10.000 \text{ V}$ .

# 2.3.1.3 POWER FILTERS

As can be seen in Figure 2-3, the power distribution and filtering on the ADM1224F IPack is split between the digital system (upper left area of Figure 2-3) and the analog system (lower portion of Figure 2-3). The IPack's 50-pin logic connector has two pins reserved for +5volt power, four pins for ground return, and one each for  $\pm 12$  V. One +5 V line and two of the ground return lines are dedicated as digital power lines. The digital power filtering consists of eight decoupling  $(0.1\mu\text{F})$  capacitors. The other +5 V line,  $\pm 12$  V lines, and the remaining two ground return lines (separately defined as AREF  $\equiv$  Analog REFerence) are dedicated as analog power lines. The analog power filter consists of a 68  $\mu\text{F}$  bulk filter for the +5 V input, three T-type L-C-L filters for the +5 &  $\pm 12$  V sources, and seventeen decoupling  $(0.1\,\mu\text{F})$  capacitors. About two thirds of the board has a solid analog ground plane, under all of the analog circuitry and analog power filters, that connects to AREF (analog ground return). The analog and digital grounds are tied together on the carrier-side of the logic connector, as are the two different +5 V power source lines.

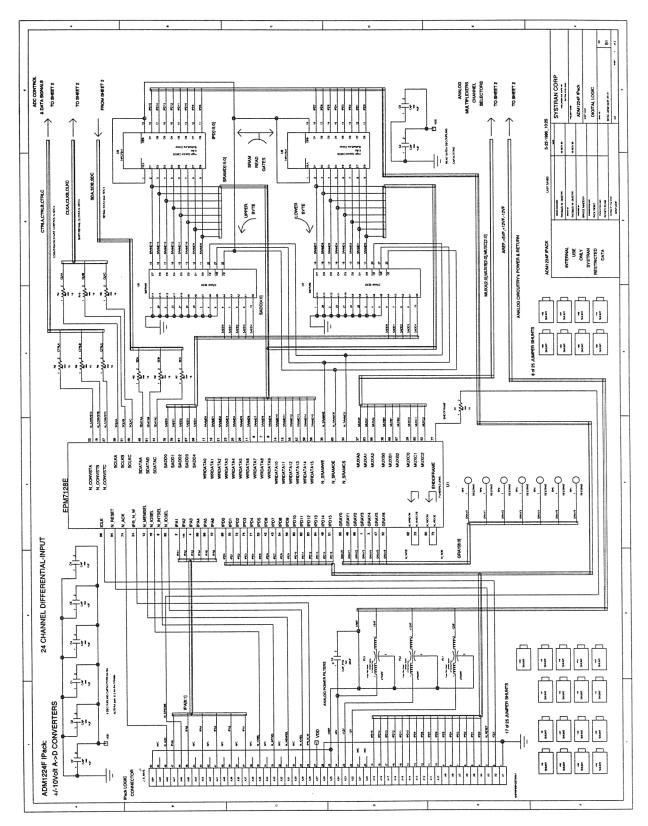

#### 2.4 ADM1224F SCHEMATICs

**NOTE**: Refer to the ADM1224F schematics located in Appendix B while reading this material since individual components are referred to by function name (SRAM, Buffer, ADC, MUX, Connector, etc.), component reference designators (U1, R3, C5, J2, etc.), industry-standard device part numbers (7128, AMP03, AD7893, 74FCT541, etc.), or physical location references. The physical location references are found along the borders of the schematics. The numbers  $1 \rightarrow 6$  are found along the top and bottom and go from left  $\rightarrow$  right, respectively. The letters  $A \rightarrow F$  are found along both sides and go from top  $\rightarrow$  bottom, respectively. Location A1 is the top left corner; C3 is slightly up and left of center; F6 is at the bottom right corner; etc.

The following is a short presentation on the schematics of the ADM1224F. There are two pages that comprise the schematic set. The first page presents all of the digital circuitry, combined with the IPack-logic connector, digital-logic filtering, analog-circuitry bulk filtering, and the 25 jumper switch shunts for the analog-input circuitry. The second page presents all of the analog circuitry, combined with the IPack I/O connector, and the remainder of the analog circuitry's filtering.

#### 2.4.1 SCHEMATICS - SHEET 1 - COMPONENTS

The active components on sheet 1 are:

- U1, located at A3 → E3, is an ALTERA 7128 EPLD that contains all of the digital-control logic that supports the carrier and analog-circuitry sequencing activities

- U4, at C4  $\rightarrow$  D5, is the low byte of the CVT

- U5, at B4  $\rightarrow$  C5, is the high byte of the CVT

- U2, at C5  $\rightarrow$  D6, is the lower byte of the SRAM Buffer (see figure 2-3)

- U3, at B5  $\rightarrow$  B6, is the upper byte SRAM Buffer.

The discrete components on sheet 1 are:

- J1, found at B1 → E1, is the IPack logic connector which interfaces with the host carrier.

- Capacitors C1, C2, C5 and C6, found at A1 → A2, are decoupling capacitors for U1.

- Capacitor C3, located at D6, is a decoupler for U2.

- Capacitor C4, located at A2, is a decoupler for U3.

- Capacitor C7, found at A1, is a decoupler for U4.

- Capacitor C8, located at D6, is a decoupler for U5.

- Resistor R1, located at E4, is a series termination resistor for the ENDOFRAME (end of frame) pulse output that is driven onto the N\_STROBE signal line of the logic connector J1.

- R2 → R10, located at A4 → B5, are series termination resistors for the digital interface lines between the 7128 controller EPLD and the three ADCs. Their function is to minimize noise normally generated by switching digital signals.

- H2  $\rightarrow$  H26, located at F1  $\rightarrow$  E2 and at F4, are the 25 shorting shunts for the jumper switches that are located on sheet 2 of the schematics.

- The 68 μF tantulum capacitor C9, located at D2, is the bulk power filter for the analog circuitry's +5 V power rail.

- FL1, FL2, and FL3, at D2 → E2, are the T-Type power filters for all three voltage sources for the analog circuitry.

The inventory of elements on sheet 1 of the schematics is complete except for seven non-components. These are the testpoints  $TP1 \rightarrow TP7$ , located at  $E3 \rightarrow F3$ . These "donuts" provide troubleshooting hooks that monitor the actual state of the core GRAY CODE engine.

# 2.4.2 SCHEMATICS - SHEET 2 - COMPONENTS

The active components on sheet 2 are:

- U14, U15, and U16, at A3 → F4, are the ADG507AKP devices that perform the input signals' selection (multiplexing) duties. MUX'A', referred to as U14, handles channels 1 → 8; MUX'B' = U15 controls channels 9 → 16; U16 selects channels 17 → 24.

- U9, U11, and U13, at A2 → E3, are the AMP03 differential amplifiers that buffer the outputs of the multiplexers and provide single-ended outputs to the ADCs

- U8, U10, and U12, at A1  $\rightarrow$  E2, are the AD7893 serial 12-bit ADCs that accomplish the analog $\rightarrow$ digital conversions.

- U6, at D2, is the AD680 precision +2.500 V reference (VREF generator). The output of U6 is buffered by U7, located at F1 → F2. U7 is an OP177 operational amplifier configured as a simple voltage follower. Its "VREF" output is directly connected to the REFIN (reference input) of all three ADCs and to a jumper switch for optional sampling as channel #24.

The discrete components on sheet 2 are:

There are five decoupling capacitors (0.1 μF) for the analog +5 V power. C13, at A2, provides decoupling for U8. C16, at C2, provides decoupling for U10. C10, at D2, provides decoupling for U6. C19, at D2 → E2, provides decoupling for U12. C11, at E1, provides decoupling for U7.

- There are six decoupling capacitors (0.1 μF) for the analog +12 V power. C21, at A3, provides decoupling for U14. C12, at B3, provides decoupling for U9. C15, at C3, provides decoupling for U15. C24, at D3, provides decoupling for U11. C18, at D3 → E3, provides decoupling for U16. C26, at F3, provides decoupling for U13.

- There are six decoupling capacitors (0.1 μF) for the analog -12 V power. C22, at A3, provides decoupling for U14. C14, at B2 → B3, provides decoupling for U9. C17, at C3, provides decoupling for U15. C23, at D2 → D3, provides decoupling for U11. C20, at D3 → E3, provides decoupling for U16. C25, at F2 → F3, provides decoupling for U13.

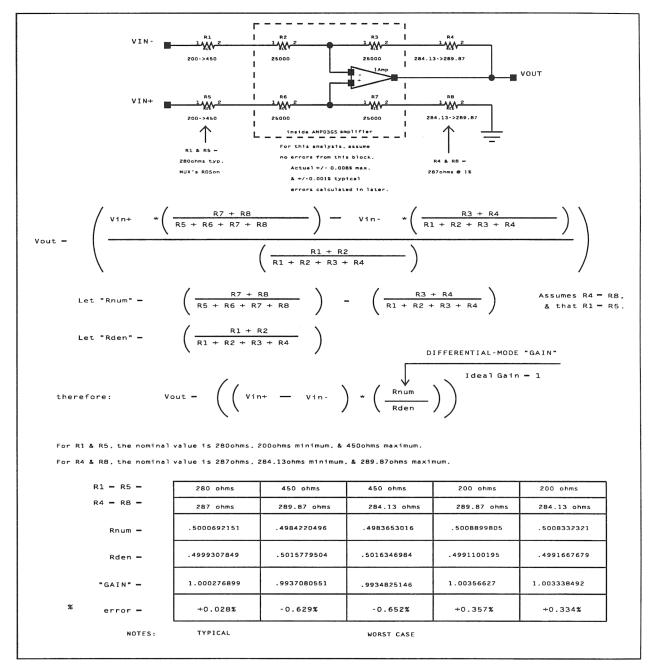

In the following description, the "A-side" circuitry of the differential-analog multiplexers allows the non-inverting signals to pass, and the "B-side" allows the inverting signals to pass.

- R11, a precision resistor at B2, provides additional inverting feedback resistance in U9's circuitry, compensating the overall gain for the additional inverting input resistance that occurs due to the typical "RDSon" value through the B-side circuitry of U14.

- R14, a precision resistor at B2, provides additional non-inverting feedback resistance in U9's circuitry, compensating the overall gain for the additional non-inverting input resistance that occurs due to the typical "RDSon" value through the A-side circuitry of U14.

- R12, a precision resistor at C2, provides additional inverting feedback resistance in U11's circuitry, compensating the overall gain for the additional inverting input resistance that occurs due to the typical "RDSon" value through the B-side circuitry of U15.

- R15, a precision resistor at D2, provides additional non-inverting feedback resistance in U11's circuitry, compensating the overall gain for the additional non-inverting input resistance that occurs due to the typical "RDSon" value through the A-side circuitry of U15.

- R13, a precision resistor at E2, provides additional inverting feedback resistance in U13's circuitry, compensating the overall gain for the additional inverting input resistance that occurs due to the typical "RDSon" value through the B-side circuitry of U16.

- R16, a precision resistor at E2, provides additional non-inverting feedback resistance in U13's circuitry, compensating the overall gain for the additional non-inverting input resistance that occurs due to the typical "RDSon" value through the A-side circuitry of U16.

There are twenty-six two-pin jumper switches on the ADM1224F IPack.

- J3 → J10, located at A4 → A6, provide inverting input shorts to AREF when

their respective shunts are installed for channels 1 → 8, respectively. Installing a

shunt (described as H2 → H26 above in Sheet 1 components) effectively

changes the input from a differential-ended input channel to a single-ended input

channel.

- J11  $\rightarrow$  J18, located at C4  $\rightarrow$  C6, provide inverting input shorts to AREF when their respective shunts are installed for channels 9  $\rightarrow$  16, respectively.

- J19  $\rightarrow$  J26, located at D4  $\rightarrow$  D6, provide inverting input shorts to AREF when their respective shunts are installed for channels 17  $\rightarrow$  24, respectively.

Channel #24 uses the other two jumper switches to select its signal source.

- When a single shorting shunt is installed on J2, at F4, and no shunt is installed on J27, also at F4, the input to channel #24 is the buffered on-board VREF (+2.500 V).

- When a single shorting shunt is installed on J27 and J2 is left open, the signal present on pin 50 of the I/O connector, the non-inverting input for channel #24, is applied as the input to channel #24.

- As mentioned previously in the discussion of Figure 2-3, it is possible (though, not advisable) to couple VREF as an output to the I/O connector. This is accomplished by placing a shorting shunt on both J2 and J27. When this is done, VREF will be sampled as channel #24 and be exposed to the I/O connector for monitoring purposes.

**NOTE**: Additional jumpering information is provided in Section 3.0 of this manual.

J28, located at A6  $\rightarrow$  E6, provides all of the I/O connections to the ADM1224F IPack. Pins #25 and #26 must be connected to the analog ground reference of the signals' source. Unused channels should have their non-inverting inputs tied to these pins, while the jumper shunts should be installed on the inverting inputs for the same unused channels.

The symbol designated as H1, located at E6, is for the printed circuit board itself. This is simply used for the generation of the bill-of-materials.

#### 2.5 SAMPLING DETAILS

The ADM1224F IPack is a fixed sequence, free-running sampling machine. As described previously, the channels are sectored into three groups of eight channels. Despite its initial appearance, the signal sampling and data conversion process is deterministic and, with the help of the appended frame count values, exact times between any samples can be calculated for samples obtained within a window of 1.12 ms. Channel—channel uncertainty is on the order of a few nanoseconds (based upon the stability of the ICLK supplied by the carrier).

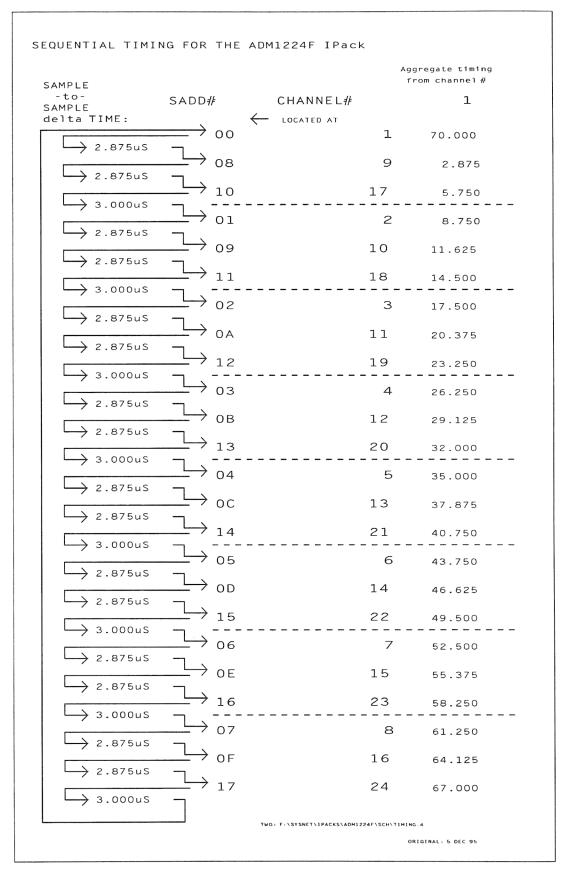

#### 2.5.1 SAMPLING ORDER

The channel number sampling order is: 1, 9, 17, 2, 10, 18, 3, 11, 19, 4, 12, 20, 5, 13, 21, 6, 14, 22, 7, 15, 23, 8, 16, and 24.

#### 2.5.2 SAMPLING RATE

All channels are tightly controlled in their timings for channel selection, settling times, and when the actual conversion process starts as defined by the transition from "track" mode to "hold" mode. Each channel is repetitively sampled at a fixed cycle time of  $70.000~\mu s$ , for a fixed sampling rate of  $1\div70~\mu s = 14,285.71429$  (over 14,285) samples per second per channel.

Due to the potential access contention to the CVT, the CVT controller will arbitrate the access for a no-WAIT read to the carrier while writes to the CVT of newly acquired data are delayed, as necessary. The window of opportunity for these writes to the CVT are four ICLK cycles long per sampling. This means that if the carrier starts a read of CVT

information at exactly the same time new ADC data is ready to be written into the CVT, the ADM1224F IPack can support up to a maximum of two carrier-inserted HOLD cycles and still accomplish the write to the CVT. If the carrier inserts more than two HOLD cycles, then the write to the CVT will not take place and the captured data is discarded. There are no built-in limits for the number of HOLD cycles that can be asserted by a carrier during any one transfer. This CVT write activity will be explored when the actual sequence of events is explored in greater detail in section 2.6. The "bottom line" of this immediate discussion is that while the sampling rate is fixed, the write-to-the-CVT rate is not necessarily fixed during times of contention for the usage of the CVT.

There may be applications where a sampling rate of 14,285 samples per second is insufficient for the bandwidth of the signal be captured. Supercommutation techniques solve this problem nicely. For instance, if a signal has a bandwidth of 5 KHz, then it is recommended that the signal be sampled at least at a 25 KHz rate, more if possible. Applying the same signal to both channels #1 and #5 (first and thirteenth channels to be sampled) will provide evenly spaced acquisitions 35 µs apart for an aggregate sampling rate of over 28,571 samples per second. Evenly spacing the supercommutation of multiple samplings for the same signal applied to three input channels could be accomplished by driving the signal into channels #1, #19, and #14 (first, ninth, and seventeenth channels to be sampled) for an aggregate sampling rate of over 42,857 samples per second. A four channel sampling applied to channels #1, #3, #5, and #7 (first, seventh, thirteenth, and nineteenth channels to be sampled) yields an aggregate sampling rate of over 57,142 samples per second. At the extreme, applying the same signal to all 24 channels provides an aggregate sampling rate of over 342,857 samples per second.

**NOTE**: The apparent input impedance drops (to a minimum of  $\approx 17 \, \text{K}\Omega$ ) as the number of channels is increased in this scheme, thus requiring more drive capability from the signal source.

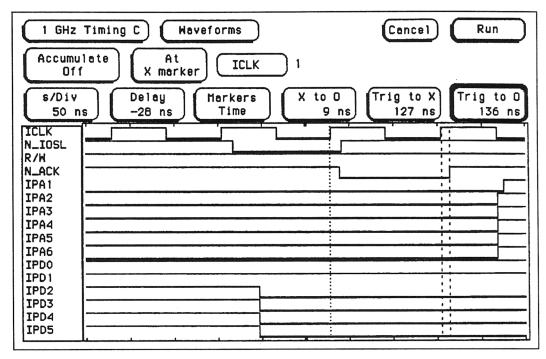

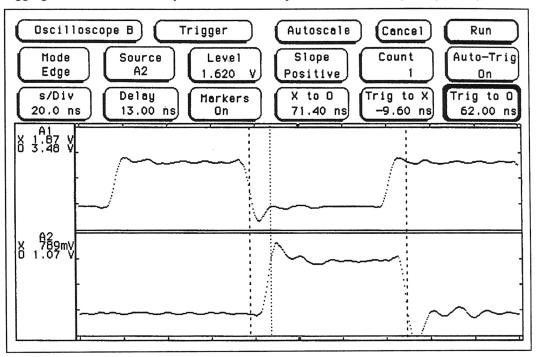

#### 2.5.3 SAMPLING TIMING

As discussed on page 2-7, three samplings occur per pass of the 70 states of the main GRAY CODE engine, with eight full passes required for a full frame of 24 channels of sampling. Also recall that while only 69 states were required to accomplish the necessary sampling tasks, a seventieth state was added to provide true single-bit transitions in the engine. Thus, every third sampling has an extra ICLK cycle added to its sampling time. The following is a complete list of the sampling time spacing between channels, in the order of sampling.

Using channel #1 as the start of the sampling process:

2.875 µs elapse from the sampling of channel #1 until the sampling of channel #9.

2.875 µs elapse from the sampling of channel #9 until the sampling of channel #17.

3.000 µs elapse from the sampling of channel #17 until the sampling of channel #2.

(Notice the extra 125 ns representing the seventieth state of the GRAY CODE engine.)

2.875 µs elapse from the sampling of channel #2 until the sampling of channel #10.

2.875 µs elapse from the sampling of channel #10 until the sampling of channel #18.

3.000 µs elapse from the sampling of channel #18 until the sampling of channel #3.

2.875 µs elapse from the sampling of channel #3 until the sampling of channel #11.

2.875 µs elapse from the sampling of channel #11 until the sampling of channel #19.

3.000 µs elapse from the sampling of channel #19 until the sampling of channel #4. 2.875 µs elapse from the sampling of channel #4 until the sampling of channel #12. 2.875 µs elapse from the sampling of channel #12 until the sampling of channel #20. 3.000 µs elapse from the sampling of channel #20 until the sampling of channel #5. 2.875 µs elapse from the sampling of channel #5 until the sampling of channel #13. 2.875 µs elapse from the sampling of channel #13 until the sampling of channel #21. 3.000 µs elapse from the sampling of channel #21 until the sampling of channel #6. 2.875 µs elapse from the sampling of channel #6 until the sampling of channel #14. 2.875 µs elapse from the sampling of channel #14 until the sampling of channel #22. 3.000 us elapse from the sampling of channel #22 until the sampling of channel #7. 2.875 µs elapse from the sampling of channel #7 until the sampling of channel #15. 2.875 µs elapse from the sampling of channel #15 until the sampling of channel #23. 3.000 µs elapse from the sampling of channel #23 until the sampling of channel #8. 2.875 µs elapse from the sampling of channel #8 until the sampling of channel #16. 2.875 µs elapse from the sampling of channel #16 until the sampling of channel #24; and 3.000 µs elapse from the sampling of channel #24 until the next sampling of channel #1 again.

Summarily, MUX'A'  $\rightarrow$  MUX'B' channels' samplings occur at a spacing of 2.875  $\mu$ s; MUX'B'  $\rightarrow$  MUX'C' take 2.875  $\mu$ s; while transitions from MUX'C'  $\rightarrow$  MUX'A' require 3.000  $\mu$ s.

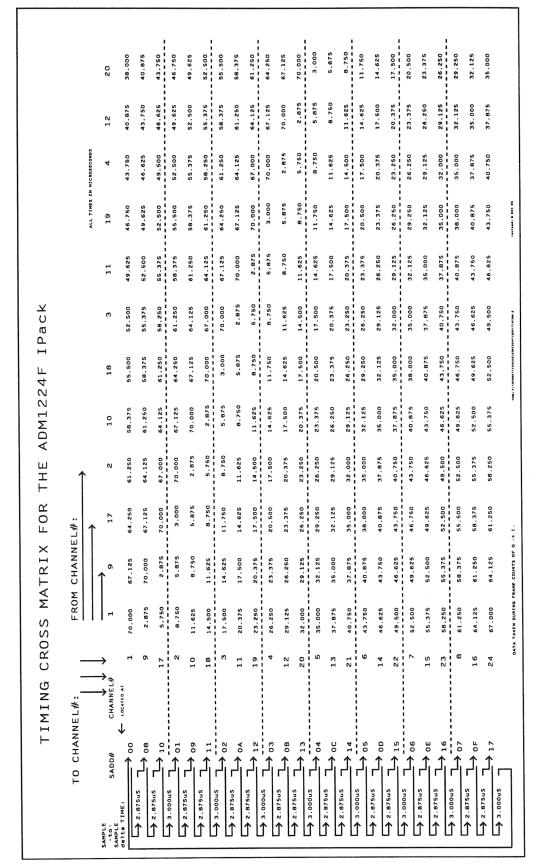

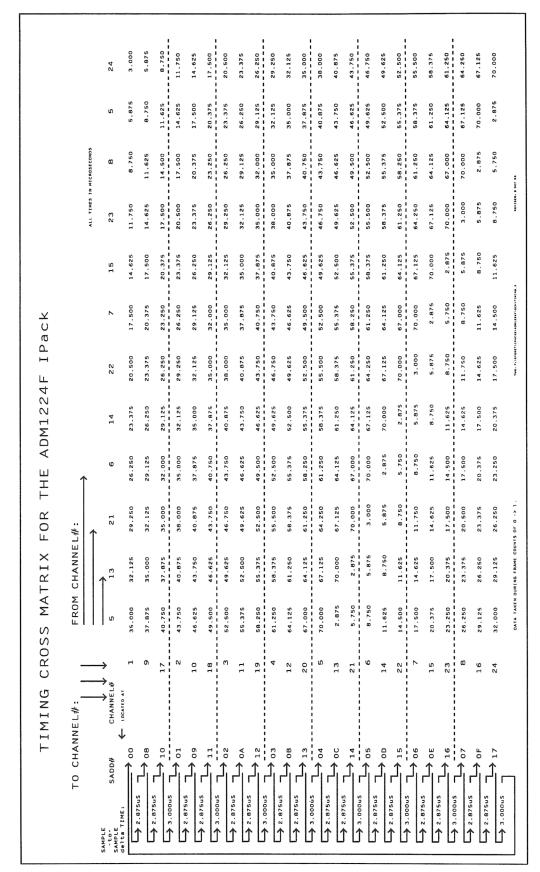

# 2.5.4 DETERMINISTIC SAMPLING

For any given period  $\leq 1.12$  ms, the exact timing relationship can be determined between any two samples to nanosecond-resolution ( $\pm$  ICLK uncertainty). This is accomplished by adding up the delta-time values between channel numbers as presented above in section 2.5.3, and adding to that value 70  $\mu$ s per frame count difference between the two samples, as discussed in section 2.3.1.1, "4-bit Frame Counter". A few examples should help clarify any outstanding uncertainties.

Assume that channel #1 is read from the CVT and its high nibble (frame count) value = Chex, and that channel #1 is subsequently read, in less than 1.12 ms, from the CVT with a new high nibble value = Ehex. Repeating that the frame count sequence is a true GRAY CODE sequence, which yields the path of: ..., 4, C, D, F, E, A, ..., it can be seen that the elapsed time from the first sampling to the second sampling =  $70 \mu \times 3 = 210.000 \mu s$ .

Assume that channel #12 is read and its frame count value = 1hex. Channel #16 is then read and its frame count value = 3hex. The within-frame delta time between channel #12 and channel #16 =  $35.000 \, \mu s$ . The frame count sequence encompassing both samples appears as: ..., 8, 0, 1, 3, 2, 6, .... Since the samples were in back-to-back frames, only  $70.000 \, \mu s$  needs to be added to the value of  $35.000 \, \mu s$  for a total time between samplings of  $105.000 \, \mu s$ .

Assume that channel #18 is read and its frame count value = 6hex. Then channel #14 is read and its frame count value is Bhex. The within-frame delta time between channels #18 and #14 adds up to 32.125  $\mu$ s. The frame count sequence that covers both of these samples is ..., 3, 2, 6, 7, 5, 4, C, D, F, E, A, B, 9, .... The difference in frame count values yields an additional  $70.000\mu$ S  $\times$  9 =  $630\mu$ S. The total time between these two samples =  $32.125 \mu$ s +  $630.000 \mu$ s =  $662.125 \mu$ s.

Assume that channel #8 is read and its frame count value = 7hex. Then channel #17 is read and its frame count value = 5hex. The frame count values are back-to-back as shown by the sequence of ..., 2, 6, 7, 5, 4, C, .... Channel #8 is the third-last sampling of frame #7 while channel #17 is the third sampling of the very next frame #5. Therefore, the total time between these two samples =  $14.500 \mu s$ .

Assume that channel #19 is read and its frame count value = 8hex. Then channel #4 is read and its frame count value = 0hex. The within-frame delta time between channels #19 and #4 is only 3.000 µs since they are consecutive samples. However, the frame counts were different. The frame count sequence that includes both samples is ..., B, 9, 8, 0, 1, 3, .... Since the frames are consecutive, only 70.000 µs has to be added for the frame count difference. This brings the time difference between these two samples to a total of 73.000 µs.

There is a timing cross matrix, 24 channels by 24 channels, presented in section 6.0 that provides all of the different possibilities for within-frame delta timings (some of which were used as examples above), with directions on how to use it.

#### 2.6 GRAY CODE ENGINE DETAILS

Table 2-1 provides a complete listing of all of the activities that take place for all seventy states of the primary sequence engine on the ADM1224F IPack. Every event is fully synchronous to the ICLK's 8 MHz clock; one event every 125  $\mu$ s. One full sweep through this core engine takes 8.750  $\mu$ s.

**NOTE**: States #63, 62, 42, and 40, while single-bit transitions, are not a normal GRAY CODE sequence.

Negating the most significant GRAY CODE bit from state #40 repeats the process back to state #00.

#### 2.7 PERFORMANCE EFFICIENCY

The maximum throughput for a single ADC used on the ADM1224F is limited by the minimum specification of 8.52 µs for the conversion and fastest data retrieval rates possible. This equates to 68.16 ICLK cyles; a minimum of 69 states; or a minimum of 70 GRAY CODE states. The efficiency rating of the core engine coupled with just one of the ADC's is therefore at 97.37%. The three different ADC's were time-staggered to utilize as much common circuitry as possible for the data retrieval and CVT storage processes, and to maximize the total data acquisition rate of the entire board.

Table 2-1 GRAY CODE Sequence Engine Activities

| STATEhex | SYNCHRONOUS EVENT:                                                                                         |

|----------|------------------------------------------------------------------------------------------------------------|

| 00       | idle                                                                                                       |

| 01       | Increment 3-bit counter that drives MUX#C signal selection                                                 |

| 03       | Retrieve ADC#A's leading 0 (bit 15) & discard                                                              |

| 02       | Retrieve ADC#A's leading 0 (bit 14) & discard                                                              |

| 06       | Retrieve ADC#A's leading 0 (bit 13) & discard                                                              |

| 07       | Retrieve ADC#A's leading 0 (bit 12) & discard                                                              |

| .05      | Retrieve ADC#A's bit 11 (msb) & register                                                                   |

| 04       | Retrieve ADC#A's bit 10 & register                                                                         |

| 0C       | Retrieve ADC#A's bit 9 & register                                                                          |

| 0D       | Retrieve ADC#A's bit 8 & register                                                                          |

| 0F       | Retrieve ADC#A's bit 7 & register                                                                          |

| 0E       | Retrieve ADC#A's bit 6 & register                                                                          |

| 0A       | Retrieve ADC#A's bit 5 & register                                                                          |

| 0B       | Retrieve ADC#A's bit 4 & register                                                                          |

| 09       | Retrieve ADC#A's bit 3 & register                                                                          |

| 08       | Retrieve ADC#A's bit 2 & register                                                                          |

| 18       | Retrieve ADC#A's bit 1 & register                                                                          |

| 19       | Retrieve ADC#A's bit 0 (lsb) & register                                                                    |

| 1B       | Drive ADC#A's N_CONVST ↓ low                                                                               |

| 1A       | Write ADC#A's data to CVT if carrier not reading CVT                                                       |

| 1E       | Write ADC#A's data to CVT if carrier not reading CVT                                                       |

| 1F       | Write ADC#A's data to CVT if carrier not reading CVT                                                       |

| 1D       | Write ADC#A's data to CVT if carrier not reading CVT                                                       |

| 1C       | Drive ADC#A's N_CONVST \(\hat{1}\) high (starts actual conversion)                                         |

| 14       | Increment 3-bit counter that drives MUX#A signal selection                                                 |

| 15       | Retrieve ADC#B's leading 0 (bit 15) & discard                                                              |

| 17       | Retrieve ADC#B's leading 0 (bit 14) & discard                                                              |

| 16       | Retrieve ADC#B's leading 0 (bit 13) & discard                                                              |

| 12       | Retrieve ADC#B's leading 0 (bit 12) & discard                                                              |

| 13       | Retrieve ADC#B's bit 11 (msb) & register                                                                   |

| 11       | Retrieve ADC#B's bit 10 & register                                                                         |

| 10       | Retrieve ADC#B's bit 9 & register                                                                          |

| 30       | Retrieve ADC#B's bit 8 & register                                                                          |

| 31       | Retrieve ADC#B's bit 7 & register                                                                          |

| 33       | Retrieve ADC#B's bit 6 & register                                                                          |

| 32       | Retrieve ADC#B's bit 5 & register                                                                          |

| 36       | Retrieve ADC#B's bit 4 & register                                                                          |

| 37       | Retrieve ADC#B's bit 3 & register                                                                          |

| 35       | Retrieve ADC#B's bit 2 & register                                                                          |

| 34       | Retrieve ADC#B's bit 1 & register                                                                          |

| 3C       | Retrieve ADC#B's bit 0 (lsb) & register                                                                    |

| 3D       | Drive ADC#B's N_CONVST ↓ low                                                                               |