# **TESTIP**

IPack Carrier

Performance Tester

User Manual

Document Nr. B-T-MU-TESTIP##-A-0-A1

## **FOREWORD**

The information in this document has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. SYSTRAN reserves the right to make changes without notice.

SYSTRAN makes no warranty of any kind with regard to this printed material including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

The schematic diagrams contained in this publication are included for reference only. The information was current at the time the printed circuit board was last revised. This information is not necessarily current or complete manufacturing data, nor is it part of the product specification. Schematics may not be reproduced without the express permission of SYSTRAN Corp.

Copyright 1995 SYSTRAN Corporation. All rights reserved.

IndustryPack<sup>®</sup> is a registered trademark of GreenSpring Computers, Inc. Motorola<sup>®</sup> is a registered trademark of the Motorola Corporation. NuBus<sup>™</sup> is a trademark of Texas Instruments, Inc. OS-9<sup>®</sup> is a registered trademark of Microware Systems Corporation

Revised: December 6, 1995

SYSTRAN Corporation 4126 Linden Avenue Dayton, OH 45432-3068 (513) 252-5601

# **TABLE OF CONTENTS**

| 1.0 INTRODUCTION                      | 1-1  |

|---------------------------------------|------|

| 1.1 Purpose                           | 1-1  |

| 1.2 Scope                             | 1-1  |

| 1.3 Overview                          | 1-2  |

| 1.4 Features                          | 1-2  |

| 1.5 Specifications                    | 1-2  |

| 1.6 Related Products                  | 1-5  |

| 1.7 Related Publications              | 1-5  |

| 1.8 Ordering Process                  | 1-5  |

| 1.9 Technical Support                 | 1-5  |

| 1.10 Reliability                      | 1-6  |

|                                       |      |

| 2.0 DESCRIPTION                       | 2-1  |

| 2.1 Overview                          | 2-1  |

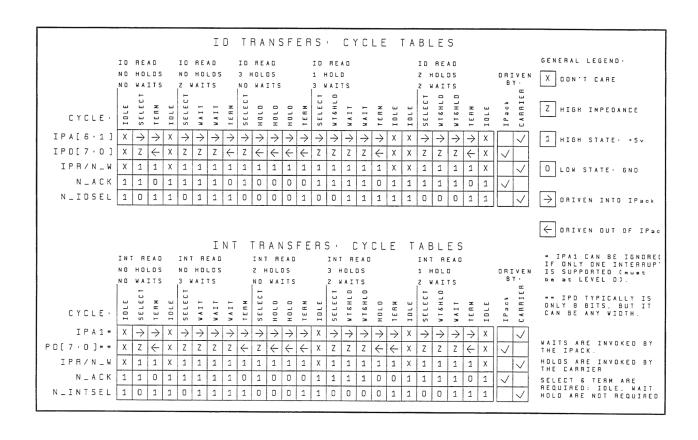

| 2.1.1 I/O Transfers                   | 2-1  |

| 2.1.2 ID Transfers                    | 2-1  |

| 2.1.3 Memory Transfers                | 2-1  |

| 2.1.4 Interrupt Transfer              | 2-2  |

| 2.1.5 Auxiliary Functions             | 2-2  |

| 2.1.6 Exceptions                      | 2-2  |

| 2.2 Block Diagram Description         | 2-2  |

| 2.2.1 IPack Sequence Controller       | 2-4  |

| 2.2.2 Wait Cycle Generator            | 2-4  |

| 2.2.3 I/O Address Controller          | 2-4  |

| 2.2.4 Error Generator                 | 2-4  |

| 2.2.5 Non-Zero IRQ Vector Detectors   | 2-4  |

| 2.2.6 ID PROM Emulator                | 2-5  |

| 2.2.7 Control/Status Registers        | 2-5  |

| 2.2.8 Extended Address Latches        | 2-5  |

| 2.2.9 Memory Address Remapper         | 2-6  |

| 2.2.10 32-KB SRAMs                    | 2-6  |

| 2.3 TESTIP Schematic                  | 2-6  |

| 2.4 I/O Accesses                      | 2-9  |

| 2.4.1 I/O Location #1                 | 2-9  |

| 2.4.2 I/O Location #2                 | 2-9  |

|                                       | 2-10 |

|                                       | 2-10 |

|                                       | 2-10 |

|                                       | 2-11 |

|                                       | 2-11 |

|                                       | 2-13 |

| ·                                     | 2-13 |

|                                       | 2-13 |

|                                       | 2-13 |

| · · · · · · · · · · · · · · · · · · · | 2-15 |

|                                       | 2-17 |

|                                       | 2-18 |

| 3.0 HARDWARE INSTALLATION                          | 3-1 |

|----------------------------------------------------|-----|

| 3.1 Unpacking the TESTIP                           |     |

| 3.2 Visual Inspection of the TESTIP                | 3-1 |

| 3.3 TESTIP Installation                            | 3-1 |

|                                                    | 3-1 |

| 4.0 PROGRAMMING GUIDE                              | 4 1 |

| 4.1 Description                                    | 4-1 |

| 4.2 ID PROM Addresses                              | 4-1 |

|                                                    | 4-1 |

| 4.3 IPack I/O Address Map                          | 4-2 |

| 4.4 Word Access Address Translation                | 4-3 |

| 4.5 Byte Access Address Translation                | 4-4 |

| 4.6 Register Descriptions                          | 4-5 |

| 4.7 Registers 00 → 38 Description                  | 4-5 |

| 4.8 1 MHz Timer Description                        | 4-5 |

| 4.9 Performance Timer Control Register Description | 4-5 |

| 4.10 Control/Status Register Description           | 4-5 |

| 4.11 Interrupt Status Register Description         | 4-6 |

| 4.12 Interrupt Control Register Description        | 4-6 |

| 4.13 Interrupt Vector 0 Register Description       | 4-7 |

| 4.14 Interrupt Vector 1 Register Description       | 4-7 |

| 4.15 Programming Examples                          | 4-7 |

| 4.15.1 Timer Example                               | 4-7 |

| 4.15.2 Interrupt Example                           |     |

| 4.15.3 Interrupt Service Routine Example           |     |

| 4.15.4 Error Example                               | 4-9 |

| 4.15.5 Wait Example                                | 4-9 |

| 4.13.5 wait Example                                | 4-9 |

| 5.0 PERFORMANCE                                    | - 1 |

| 5.1 Overview                                       | 5-1 |

|                                                    |     |

| 5.2 System Configuration                           | 5-1 |

| 5.3 I/O Transfers                                  | 5-2 |

| 5.4 ID Transfers                                   | 5-3 |

| 5.5 Memory Transfers                               | 5-5 |

| 5.6 Interrupts, Transfers and Waits                | 5-6 |

| 5.6.1 Requests                                     | 5-6 |

| 5.6.2 Vector READS                                 | 5-7 |

| 5.6.3 Wait Cycles                                  | 5-7 |

| 5.7 Performance Timer                              | 5-8 |

|                                                    |     |

| 6.0 TYPICAL APPLICATIONS                           | 6-1 |

| 6.1 Applications                                   | 6-1 |

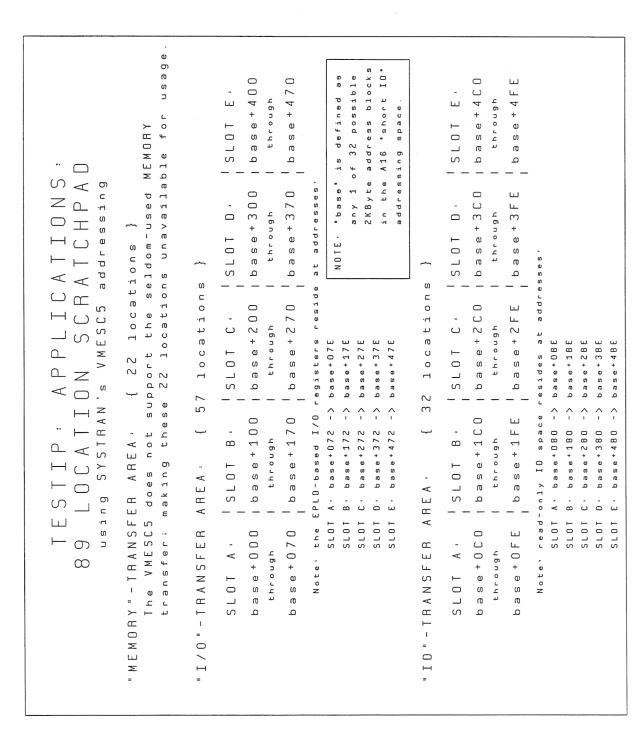

| 6.2 111 Location Scratchpad                        | 6-1 |

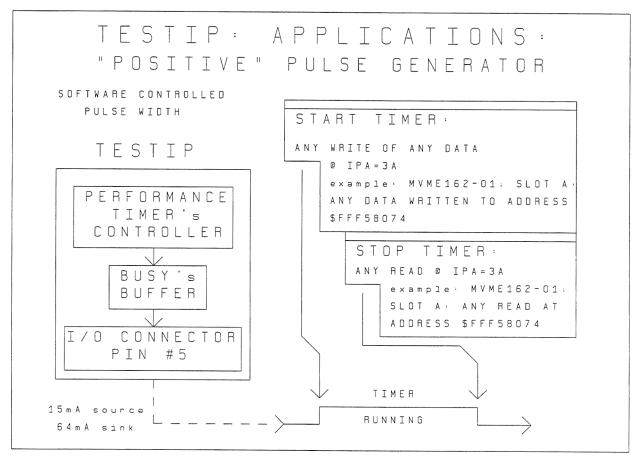

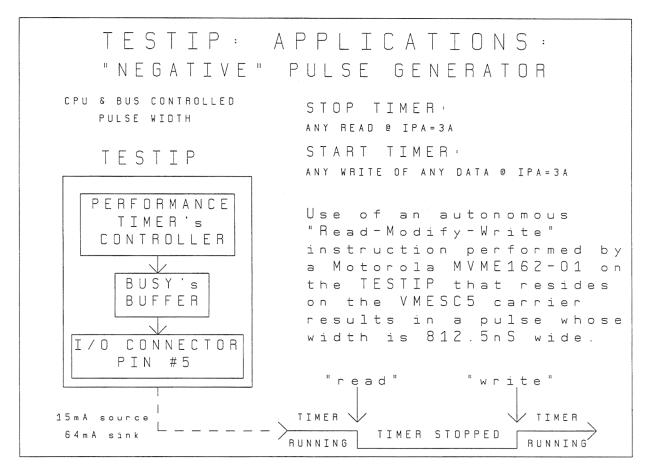

| 6.3 Bipolar Pulse Generation                       | 6-4 |

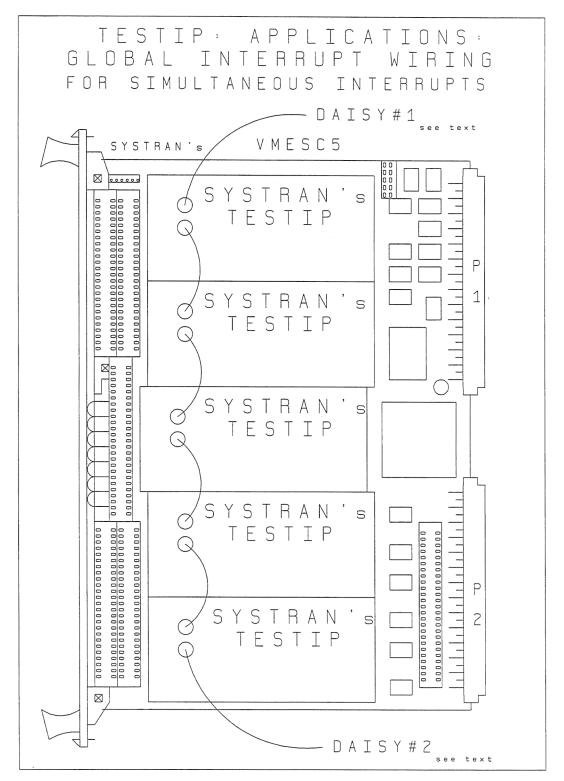

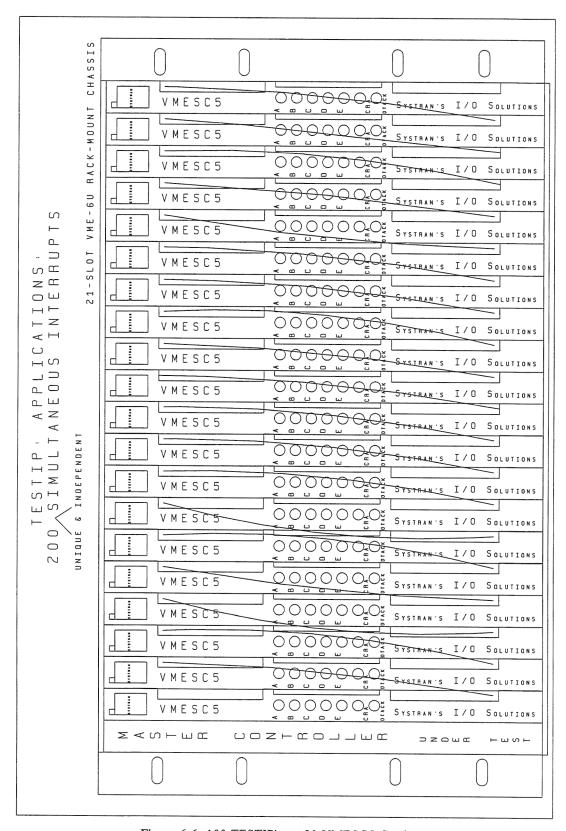

| 6.4 200 Simultaneous Interrupts                    | 6-6 |

|                                                    | -   |

| 7.0 WARRANTY AND REPAIR                            | 7-1 |

| 7.1 Warranty Coverage                              | 7-1 |

| 7.1.1 Hardware Warranty Service                    |     |

| 7.1.2 Software Warranty Service                    | 7-1 |

| 7.1.3 Other Services                   | 7-2 |

|----------------------------------------|-----|

| 7.2 Additional Paid Services           | 7-2 |

| 7.3 Term                               | 7-2 |

| 7.4 Conditions                         | 7-2 |

| 7.5 Identification of Covered Products | 7-2 |

| 7.6 Shipping                           | 7-2 |

| 7.7 Life Support and Nuclear Policy    | 7-3 |

| 7.8 Communication                      | 7-3 |

# **APPENDICES**

| Appendix A - SYSTRAN's IndustryPack Logic Interface Specification Synopsis | A-1 |

|----------------------------------------------------------------------------|-----|

| Appendix B - TESTIP Schematics                                             | B-1 |

# **FIGURES**

| Figure | 1-1  | TESTIP Board 1                                            | -1 |

|--------|------|-----------------------------------------------------------|----|

| Figure | 2-1  |                                                           | -3 |

| Figure | 2-2  | SADDGEN: SRAM's Address Generator Block Diagram 2         | -7 |

| Figure | 2-3  | TESTIP's Top Logic Diagram 2                              | -8 |

|        |      | I/O Accesses Summary 2-                                   |    |

| Figure |      | Memory Accesses Summary                                   |    |

| Figure | 2-6  | TESTIP: Test IPack SRAM's Address Map 2-                  | 16 |

|        |      | Board Number Jumpers 2-                                   | 17 |

| Figure | 2-8  | WAIT Cycles Timing Diagrams 2-                            | 19 |

| Figure | 2-9  | SRAM-based I/O Transfers Timing Diagrams 2-2              | 20 |

| Figure | 2-10 | Register-based I/O Transfers Timing Diagrams 2-2          | 21 |

| Figure | 2-11 | Interrupt Vector READ Transfers Timing Diagrams 2-2       | 22 |

| Figure | 2-12 | Memory Transfers Timing Diagrams 2-2                      | 23 |

| Figure | 2-13 | ID Transfers Timing Diagrams 2-2                          | 24 |

|        |      | Installation of the TESTIP on a VME IPack carrier board 3 | -2 |

| Figure | 3-2  | Installation of the TESTIP on a ISA IPack carrier board 3 | -2 |

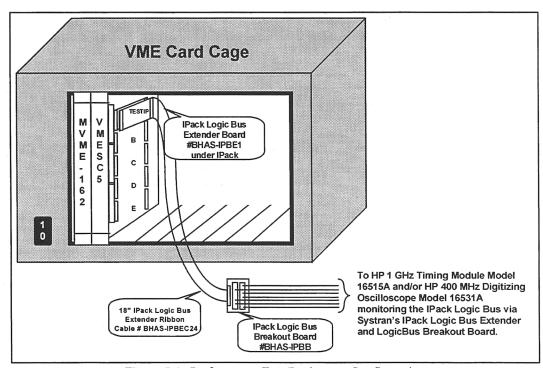

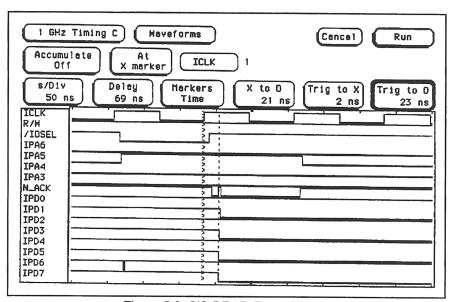

| Figure | 5-1  | Performance Test Equipment Configuration 5                | -1 |

|        |      |                                                           | -2 |

| Figure | 5-3  |                                                           | -3 |

|        |      |                                                           | -4 |

| Figure | 5-5  |                                                           | -5 |

| Figure | 5-6  | A A                                                       | -7 |

| Figure |      |                                                           | -8 |

| Figure | 6-1  | 79 Memory Locations on the MVEM162-xx                     | -2 |

| Figure |      |                                                           | -3 |

| Figure |      | "Positive" Pulse Generation                               | -4 |

| Figure |      | "Negative" Pulse Generation                               | -5 |

| Figure | 6-5  |                                                           | -7 |

| Figure | 6-6  | 100 TESTIP's on 20 VMESC5 Carriers 6                      | -8 |

# **TABLES**

| Table 2-1 | Performance Timer Functions and Access Types                   | 2-9 |

|-----------|----------------------------------------------------------------|-----|

| Table 3-1 | TESTIP Shipping Package Contents                               | 3-1 |

| Table 3-2 | TESTIP Installation Tools                                      | 3-2 |

| Table 3-3 | IPack Logic Bus Pin Assignments                                | 3-4 |

| Table 3-4 | IPack I/O Connector Pin Assignments                            | 3-5 |

| Table 4-1 | TESTIP ID Address Space Listing                                | 4-1 |

| Table 4-2 | TESTIP I/O Address Map                                         | 4-2 |

| Table 4-3 | Word Access Address Translation Table                          | 4-3 |

| Table 4-4 | Byte Access Address Translation Table                          | 4-4 |

| Table 4-5 | Interrupt Control Register Bit Descriptions - IP Address = 3B  | 4-5 |

| Table 4-6 | Interrupt Status Register Bit Descriptions - IP Address = 3C   | 4-6 |

| Table 4-7 | Interrupt Control Register Bit Descriptions - IP Address = 3D  | 4-6 |

| Table 4-8 | Interrupt Vector 0 Register Bit Descriptions - IP Address = 3E | 4-7 |

| Table 4-9 | Interrupt Vector 1 Register Bit Descriptions - IP Address = 3F | 4-7 |

| Table 5-1 | I/O READ From SRAM                                             | 5-2 |

| Table 5-2 | TESTIP Typical ID Access Times                                 | 5-3 |

|           | TESTIP Typical MEMORY Access Times                             |     |

| Table 5-4 | TESTIP Typical Interrupt Request Times                         | 5-6 |

| Table 5-5 | TESTIP Typical INTERRUPT VECTOR READ Times                     | 5-7 |

| Table 5-6 | TESTIP Typical TIMER Times                                     | 5-8 |

|           |                                                                |     |

## **GLOSSARY**

[x:y]. Nomenclature designating a bit-range, where "x" is the left-most bit and "y" is the right-most bit. (e.g. Data bus [7:0] refers to the Least Significant eight bits).

byte. 8 bits.

byte-lane. 8 bits of a data bus on octal boundaries.

CAE. Computer Aided Engineering.

doublewide. An IPack module that is twice the size of a standard IndustryPack module.

EPLD. Erasable Programmable Logic Device.

**ID PROM.** The circuitry that presents the proper data patterns to the low 8 bits of the IPDbus during the ID (read) transfers.

IndustryPack. Credit-card size mezzanine-type subsystems designed with a common digital interface known as the IP bus. An open industry standard defines the mechanical and electrical interface to the carrier board.

I/O. Input/Output.

IPack. Refers to the IndustryPack standard.

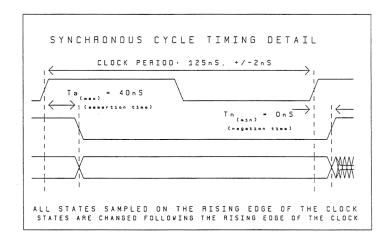

**Pack logic bus.** A synchronous, 4 M transfers/sec, 16- or 32-bit wide bus that includes I/O, memory, ID PROM, interrupts. The address bus is 6 bits wide, except in memory mode. Then the data bus is multiplexed for the upper portion of the address bus, resulting in 22 bits of address. This results in up to 4 M words of memory space per IPack module.

IPDbus. IPack Data Bus.

MTBF. Mean Time Between Failures.

ns, µs, ms Nanoseconds, microseconds, and milliseconds respectively.

PC. Personal Computer.

QSOP. Quarter-sized Small Outline Packages.

singlewide. An IPack printed circuit board (3.9" by 1.8"). Each module has two 50-pin connectors.

VHDL. Very high speed integrated circuit Hardware Description Language.

## 1.0 INTRODUCTION

## 1.1 Purpose

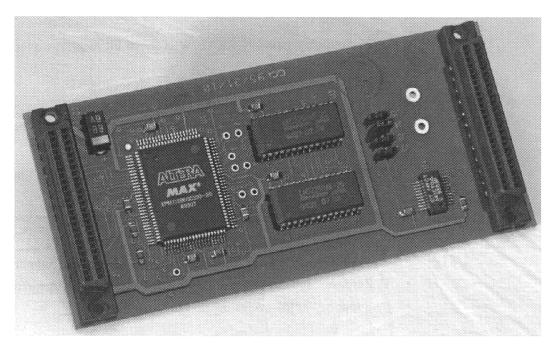

This is a reference manual for SYSTRAN's IndustryPack (IPack) Carrier performance tester, referred to as the TESTIP, part number BHAS-TESTIP. Figure 1-1 is a picture of the TESTIP board.

Figure 1-1 TESTIP Board

## 1.2 Scope

This reference manual covers the physical and operational description of the TESTIP, both from hardware and software perspectives. This manual also contains detailed technical information about the TESTIP's performance characteristics, and a few typical applications. It is assumed that the reader has a general understanding of computer processing, hardware and/or software applications experience, and a working knowledge of using IPacks on their carrier(s) of choice. The TESTIP is designed to enhance this carrier performance knowledge base. Citation of equipment from other vendors within this document does not constitute an endorsement of their products.

## 1.3 Overview

The TESTIP is a singlewide IPack board, conforming both mechanically and electrically to the Industry Pack Logic Interface Specification Revision 0.7.1. It can be used singly, or in combination with other TESTIP's to assist in the verification of both functional and performance characteristics of ALL IPack carriers. It can also be used as an operational IPack in systems needing powerful interrupt support, a system-wide time-synchronization scheme, a high-performance timer, a variable-width, softwareprogrammable pulse generator, or additional READ/WRITE (up to 111) "memory" locations for various applications.

#### 1.4 Features

- 22 "memory-transfer" READ/WRITE 16-bit locations over full 8 MByte range

- 57 "I/O-transfer" READ/WRITE 16-bit locations

- 32 "ID-transfer" READ/WRITE 16-bit locations

- 20 "Address-in-Address" READ locations in "ID" range

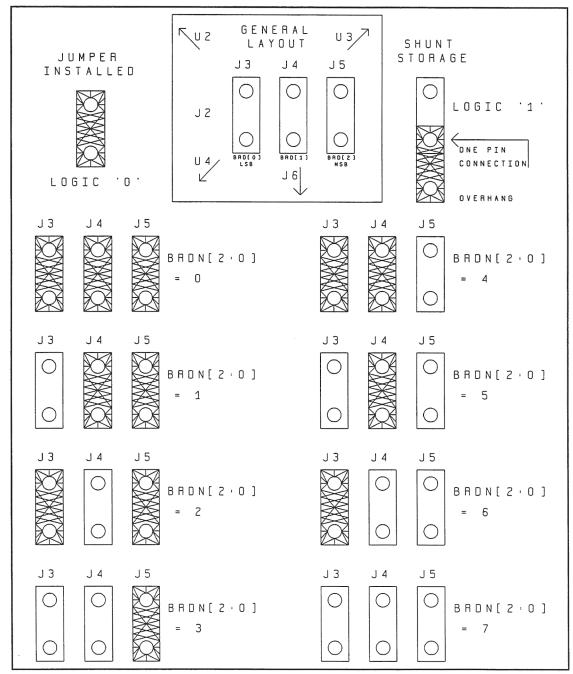

- 1-of-8 board number identification switches

- Software-controllable 16-bit 1 MHz (READ-on-the-fly) timer

- "N ERROR" signal generator

- "N STROBE" status monitor

- Two levels of local interrupt generation support

- System-wide "global" interrupt generation/reception support

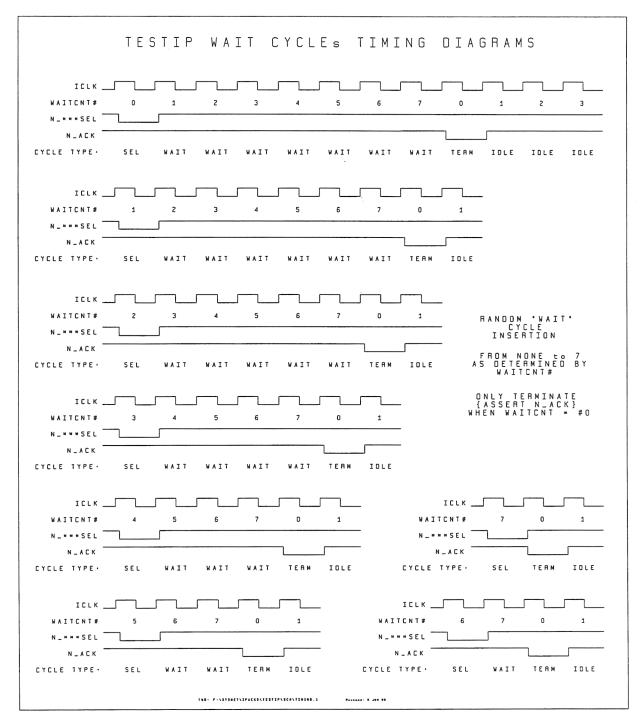

- Zero, or pseudo-random 0→7 "wait" cycle insertion generator

- Supports "hold" cycles on all valid transfers

## 1.5 Specifications

## MECHANICAL: Singlewide IPack

1.800" x 3.900" x 0.303" (above board), Measurements: 4.572 x 9.906 x 0.770 cm

Weight: 0.894 oz., 25.34 grams

Board thickness: 0.062", 0.157 cm, nominally, (4 layers)

## PROTOCOL: Overall

- Specification Revision = 0.7.1

- Singlewide IPack transfers

- 8 MHz only; no 32 MHz operations

- No "wait" cycles on any transfer types, normally

- Optionally insert  $0 \rightarrow 7$  "wait" cycles on all transfer types, randomly

- Supports carrier-asserted "hold" cycles

- Complete (no partial) address decoding

- No acknowledgement for unsupported transfer types and addresses:

- Interrupt WRITEs

- DMA activity (all forms)

- 4,194,282 of 4,194,304 possible memory "word" locations

- Maximum READ and WRITE transfer rate:

- 4 MTransfers/second, sustained

- Minimum READ and WRITE transfer rate:

- 889 KTransfers/second, 7 wait cycles inserted per transfer

## PROTOCOL: ID TRANSFERS

- READ 16-bit (byte-lanes ignored) from IPA = 00 → 1F hex Upper byte (IPD[15:8]) zero-filled WRITEs acknowledged with no data changes

- WRITE to and READ from last 32 locations, IPA =  $20 \rightarrow 3F$  hex Low byte, high byte, and full-word READs and WRITEs

## PROTOCOL: INTERRUPT TRANSFERS

• READ 16-bit (byte-lanes ignored) from IPA = 00 and 01 hex Upper byte (IPD[15:8]) zero-filled

## PROTOCOL: I/O TRANSFERS

- WRITE to and READ from first 57 locations, IPA =  $00 \rightarrow 38 \text{ hex}$ Low byte, high byte, and full-word READs and WRITEs

- READ (on-the-fly) 16-bit (byte-lanes ignored), 1 MHz timer from IPA = 39 hex

WRITE (any data, any width) to reset timer value to '0000'

- READ (any width) to stop timer from IPA = 3A hex (pseudo-register)

WRITE (any data, any width) to start timer

- READ 16-bit (byte-lanes ignored) from IPA =  $3B \rightarrow 3F$  hex Low byte, and full-word WRITES

Unused bits zero-filled:

IPA = 3B: IPD[15:3]

IPA = 3C: IPD[15:2]

IPA = 3D: IPD[15:3]

IPA = 3E: IPD[15:8]

IPA = 3F: IPD[15:8]

## PROTOCOL: MEMORY TRANSFERS

- Low byte, high byte, and full-word READs and WRITEs

- Only valid addresses defined as a single asserted '1' address line with 21 negated '0' address lines in the field:

$IPD[15:0] \Rightarrow IPA[22:7]$  (extended memory address during "select" cycle) IPA[6:1] ( $IPD[15] \Rightarrow IPA[22] \equiv most significant address bit)$

## POWER REQUIREMENTS:

Power: +5 Vdc @ 220 mA (typical, no I/O loads)

±12 Vdc @ 0 mA

Electrical characteristics: Refer to Section 5.0 PERFORMANCE

#### ABSOLUTE MAXIMUM RATINGS:

Supply voltage with respect to ground: -0.5Vdc min., +7.0Vdc max.

## **RECOMMENDED SUPPLY RATINGS:**

Supply voltage with respect to ground: +4.75Vdc  $\rightarrow +5.25$ Vdc

#### LOGIC INTERFACE:

IndustryPack specification-compliant carrier

## I/O INTERFACE:

I/O input voltage: ground → supply voltage

Input current =  $5 \mu A$  maximum, 2 nA typical

(for inputs ground → supply voltage)

= -320 mA maximum @ -2.5 volts input

(heavy negative clamping); must be externally limited

to  $\leq 20 \text{ mA}$

Low voltage = 0.8 volts maximum, negative clamp starts @ -1.0 volts

= 2.0 volts minimum High voltage

Rise/Fall times: No limit as long as the input is continually rising or falling

(no more than 200 mVolts of hysteresis) through the

logic threshold region of 0.8 volts  $\rightarrow$  2.0 volts.

I/O output voltage:

Low voltage = 0.55 volts maximum @ 64 mA loading

High voltage = 2.4 volts minimum @ 15 mA loading

Short Circuit = -60 mA minimum, -225 mA maximum

Current No more than one output shorted at a time for  $\leq 1$  sec.

No positive Can power down without disconnecting and de-energizing

clamp: loads

#### **ENVIRONMENTAL SPECIFICATIONS:**

Temperature: (Operating):  $-15^{\circ}\text{C} \rightarrow +85^{\circ}\text{C}$

(Storage):  $-65^{\circ}C \rightarrow +150^{\circ}C$

- Humidity (Noncondensing):  $5\% \rightarrow 95\%$

- Vibration (Operating): 10 G's RMS, 20 Hz→2 KHz, random

- Shock (Operating): 50 G's maximum, all axes

- Altitude (Operating): 10,000 feet maximum

## MEAN TIME BETWEEN FAILURES (MTBF):

4,409,171 hours per MIL-HDBK-217F

## 1.6 Related Products

- Software: 'C' library and OS-9® device driver routines with documentation.

- ATE: Automatic Test Equipment Software/Hardware Package, with CASE based design/analysis.

#### 1.7 Related Publications

- Industry Pack Logic Interface Specification Synopsis published by SYSTRAN Corp. (Doc number: B-T-SH-IPACKSUM-A-0-A2 Rev. 7/15/94)

- Industry Pack Logic Interface Specification Revision 0.7.1 published by GreenSpring Computers, Inc. 1204 O'Brien Drive, Menlo Park, CA 94025.

## 1.8 Ordering Process

If you wish to learn more about SYSTRAN products or to place an order, the following contacts are available:

- Phone: (513) 252-5601

- E-Mail address: info@systran.com

- World Wide Web address: http://www.systran.com/

## 1.9 Technical Support

Technical documentation provided with the product discusses the technology, its performance characteristics, and some typical applications. It includes tutorial material, with comprehensive support information, designed to answer any technical questions that might arise concerning the use of this product. SYSTRAN also publishes and distributes technical briefs and application notes that cover a wide assortment of topics. The applications selected are derived from real scenarios, but do not cover all possible circumstances.

Direct any programming questions, any concerns about the functional-fit of this product for your particular application, or any questions not answered satisfactorily by this document, to the factory at (513)252-5601, or send an E-Mail message to support@systran.com for additional assistance.

Refer to Section 7.0 for warranty and repair information.

## 1.10 Reliability

SYSTRAN Corporate policy is to provide the highest-quality products in support of customer's needs. In addition to the physical product, the company provides documentation, sales and marketing support, hardware and software technical support, and timely product delivery. The SYSTRAN commitment to quality begins with

product concept, and continues after receipt of the purchased product.

An integral part of SYSTRAN quality and reliability goals is customer feedback. Customers are encouraged to contact the factory with any questions or suggestions regarding unique quality requirements, or to obtain additional information about our programs. SYSTRAN's commitment to customers includes, but is not limited to:

- Professional and quick response to customer problems utilizing SYSTRAN's extensive resources.

- Incorporation of established procedures for product design, test, and production operations, with documented milestones. Procedures are constantly reviewed and improved, ensuring the highest possible quality.

SYSTRAN provides products and services that meet or exceed the best expectations of our customers.

- All products are tested using an Automatic Test Equipment system, with samplings for all product types taken through extended testing scenarios that include stress testing for voltage and temperature ranges beyond specifications.

- All products receive a predictive reliability rating based upon a calculated MTBF utilizing the MIL-HDBK-217F. Field failures are continuously logged and evaluated for potential failure modes and trends.

- Other environmental parameters are guaranteed by design, and not tested.

- Design reliability is ensured by methodology (top-down CAE design, VHDL, synthesis, extensive all-cases simulation, ALPHA build and test, and BETA testing if required) with full concurrent engineering practices throughout.

## 2.0 DESCRIPTION

#### 2.1 Overview

The purpose of the TESTIP is to provide a wide variety of READ and WRITE access capabilities for exercising and testing any and all IPack carriers in their various modes of operation. With the exception of 32 MHz and DMA operations (which are not yet well defined), the TESTIP provides all of the transfer variations that are possible under the *IndustryPack Logic Interface Specification, Revision 0.7.1*, including a non-rule recommendation, and other features and functions to facilitate the determination of the performance characteristics for various carriers under test. The generic nature and versatility of the TESTIP, along with 111 word-width WRITE/READ-BACK locations, makes it ideal for performing general-purpose I/O support functions when not being used for carrier testing purposes.

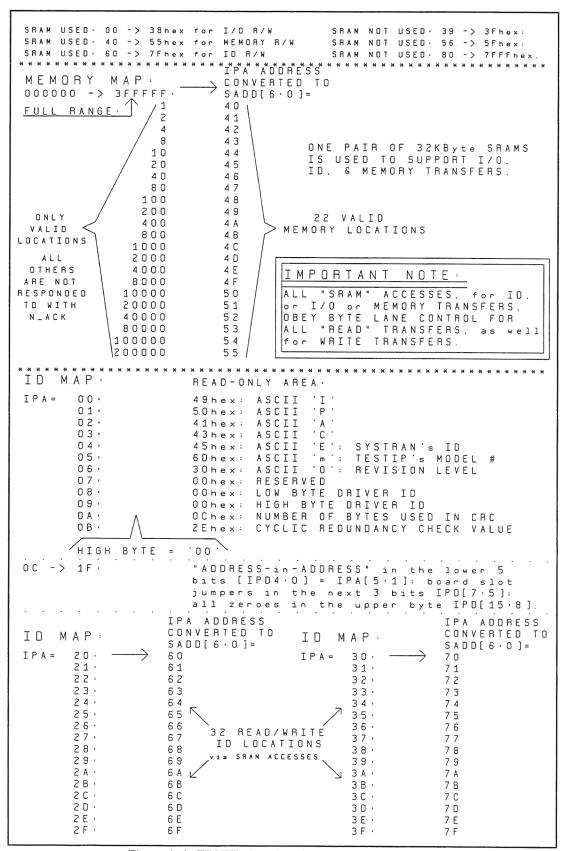

#### 2.1.1 I/O Transfers

All of the available I/O addressing space is utilized on the TESTIP. The first 57 wordwidth locations, consisting of addresses defined as IPA = '00'  $\rightarrow$  '38' hex, are WRITE/READ-BACK "registers" that execute storage in and out of a small portion of a 32 KWord SRAM. The last seven I/O locations, consisting of addresses defined as IPA = '39'  $\rightarrow$  '3F' hex, are EPLD-based control and status registers for various support features provided by the TESTIP.

#### 2.1.2 ID Transfers

All of the available ID space is utilized on the TESTIP. The first 12, READ-only, locations are the standard fixed identification fields that provide system configuration information, like all other IPacks. The next 20 ID locations, consisting of addresses defined as IPA = '0C'  $\rightarrow$  '1F' hex, provide READ-only accesses of information that provide "address-in-address" data, and switch data defining the "board number" for multiple-TESTIP carrier testing. The last 32 locations in the ID space are word-width WRITE/READ-BACK "registers" that operate in and out of a small portion of the 32 KWord SRAM.

## 2.1.3 Memory Transfers

Since the full-memory map for a singlewide IPack includes 8 MBytes of data, memory transfers are limited in scope to just 22 unique locations—one for each significant address line over the full addressing range. As with the 57 I/O and 32 ID SRAM-based accesses, these 22 MEMORY locations are word-width WRITE/READ-BACK "registers" that complete transfers using a small portion of the 32 KWord SRAM. The only "illegal" transfers that exist for the TESTIP are those for "memory" addresses not specifically encoded for this support.

## 2.1.4 Interrupt Transfer

The last transfer type of the TESTIP is interrupt support. These features include local and global, software and hardware interrupt generation capabilities (global for ganging boards together), as well as provisions for supplying distinctive interrupt vectors.

## 2.1.5 Auxiliary Functions

Several auxiliary functions are also included on the TESTIP to further facilitate the testing of various IPack carriers, both for functional and performance purposes:

- A 16-bit, 1 MHz performance counter that can easily be used to ascertain the bandwidth (rate) capacity of any carrier under test for any kind of single or combination of transfer types.

- The ability to insert a random number of (up to seven) wait states.

- The ability to drive the "N\_ERROR" line, via software, for testing the carrier's ability to sense and respond to its assertion.

- The TESTIP also provides a software path for monitoring the "N\_STROBE" input line from the logic connector for those carriers that provide connection capabilities to this IPack function.

## 2.1.6 Exceptions

- This IPack is designed to the *IndustryPack Logic Interface Specification Revision 0.7.1*, and therefore does not support DMA or 32 MHz transfers, since these were not defined at this specification level.

- The TESTIP will not respond with an acknowledgement for any memory transfer at addresses not directly defined in its architecture. This will result in a bus time-out event for the carrier's host system.

## 2.2 Block Diagram Description

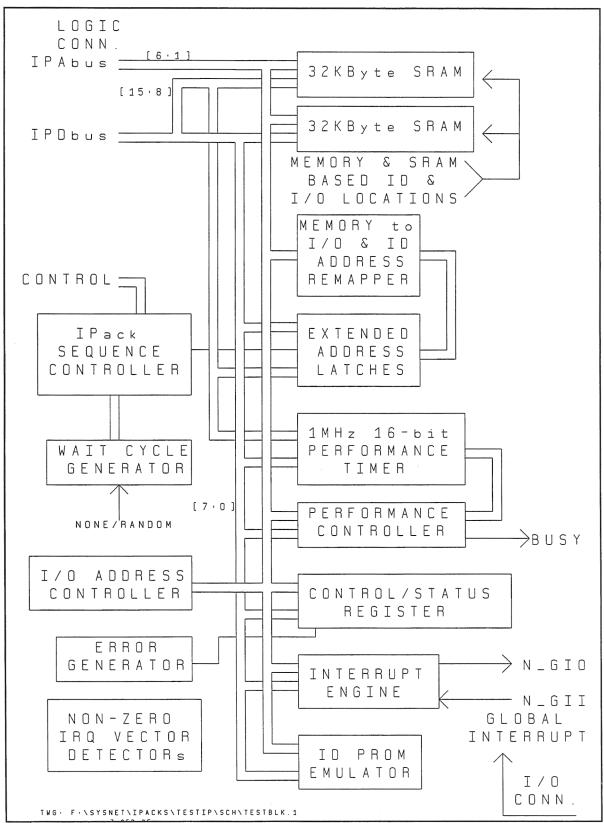

Figure 2-1 presents a block diagram for the TESTIP. In the upper left corner of the block diagram are the IPack Logic Bus connections to the IPAbus, the IPDbus, and various (undefined) IPack control signals, through which all transfers between the IPack carrier and the TESTIP's registers and data sources/destinations are conducted.

In the bottom right corner of the block diagram are the IPack I/O connections. There are only three signals, two for interrupts and one indicating the status of the performance counter. Although not shown, these three signals are buffered coming and going. In the upper right corner of the block diagram are a pair of 32 KB SRAM devices that perform WRITE/READ-BACK registration of data for all Memory Transfers, half of the ID Transfers, and 89% of the I/O transfers. The remaining circuitry depicted is housed in a single EPLD device. Not shown are power-filtering

Figure 2-1 TESTIP Block Diagram

and by-pass circuits, and a triple jumper switch that appears as a portion of the ID information that presents the board's slot position information on a carrier.

## 2.2.1 IPack Sequence Controller

This block provides all of the circuitry with responsibilities for: detection of valid I/O, ID, Memory, or Interrupt Vector transfer operations within their respective fully-decoded address ranges; development of internal and external sequence-control signals for each of the supported transfer types, including those for the external 32 KWord SRAM; proper termination cycle sequencing based upon the state of the wait-cycle generator; IPDbus READ-data source multiplexing and tristate gate control for all valid READ transfer operations; and, proper WRITE data capturing and termination cycle sequencing based upon the carrier's "HOLD" cycle insertions, when executed.

## 2.2.2 Wait Cycle Generator

This block provides all of the circuitry required for implementing a pseudo-random wait-cycle insertion scheme for those carriers needing this test function. It is a 3-bit counter that is normally held at a count of zero unless it is enabled by its control bit. When enabled, it free-runs at the ICLK rate of 8 MHz. The TESTIP will only assert N\_ACK when this counter's value is equal to zero. The randomness is due to the indeterminant nature of application software's accesses to and from the TESTIP, and to the variety of different carriers' access techniques and timings.

#### 2.2.3 I/O Address Controller

The primary operations of the logic encompassed by this block include the sectoring of the I/O accesses between SRAM reads and WRITEs, versus accesses to and from the control registers found at the top of the I/O address map, and handled by logic within the TSTCTRL EPLD. Outputs from this logic support the SRAM access-control signal generation logic contained within the IPack Sequence Controller (described above) and the SRAM-address-remapper logic. The first 57 I/O locations (IPA =  $00 \rightarrow 38 \ hex$ ) are address- and access-mapped to the low end of the SRAM. The remaining top seven I/O locations (IPA =  $39 \rightarrow 3F \ hex$ ) are contained as logic within the TSTCTRL EPLD.

#### 2.2.4 Error Generator

This is a single-bit control/status register that is a subset of the control/status registers within the EPLD. Its function is to allow the application test software to assert and negate the TESTIP's N\_ERROR signal for verifying a carrier's ability to post this status, if supported.

## 2.2.5 Non-Zero IRQ Vector Detectors

This is a pair of 8-bit, zero-value detectors that independently monitor the two top I/O locations where the interrupt vectors for both levels are located. The outputs from these detectors are used by the interrupt engine to block interrupt events. If an interrupt vector is equal to zero (power-up default condition) then this logic will block

any attempts to enable and/or execute its respective interrupt request to the carrier. These detectors were installed as a safety measure for systems that have multiple-TESTIP boards that may receive global-interrupt-request inputs prior to the proper initialization of valid interrupt vectors for subsequent Interrupt Service Routine (ISR) support.

#### 2.2.6 ID PROM Emulator

This is a subset of the IPDbus read-data source multiplexing function identified under the IPack Sequence Controller (above). For ID transfers, this logic presents fixed data in the low byte for the first twelve locations that corresponds to the unique information about the TESTIP for system-level configuration purposes. The next twenty ID locations present an "A-in-A" (Address in Address) data field in the lower five data-bit locations (IPD[4:0]  $\Leftarrow$  IPA[5:1]), while the upper three data bits in the lower byte present the board number selected for this particular TESTIP as determined by the three board number jumpers (IPD[7:5]  $\Leftarrow$  BRDN[2:0]). The upper byte READs as all zeroes for all of the lower half, READ-only ID locations. The remaining 32 ID locations are READ/WRITE accessible from/to unique SRAM locations.

## 2.2.7 Control/Status Registers

These are the locations at the top of the I/O address map that control the functionality and post the status of the TESTIP. These register functions include four locations for interrupt support, a single location for general purpose support, and two locations that provide performance counter support.

#### PERFORMANCE CONTROLLER

This is the logic that controls the starting, stopping, reading, and resetting of the 16-bit performance counter. It also includes a 3-bit prescalar counter that divides the ICLK down to the frequency required to provide 1 µs resolution required for the counter. And finally, this logic also provides the "BUSY" signal drive that indicates that the counter is running.

## 1 MHZ 16-BIT PERFORMANCE TIMER

This function consists of a fully synchronous 16-bit counter implemented with two 8-bit counting blocks with a full-look-ahead carry connecting the two groups. Since this counter is incremented by ICLK, full on-the-fly READs are possible without additional latching of the counter contents. There is no terminal count detection and/or stop logic, with rollover counting being feasible.

#### **Interrupt Engine**

This logic consists of the functions required to generate two separate interrupt requests to the carrier, using local- and global-request mechanisms. Two of the control/status registers are directly used, along with the interrupt vectors' non-zero detection logic, to generate and service interrupt requests, as needed.

## 2.2.8 Extended Address Latches

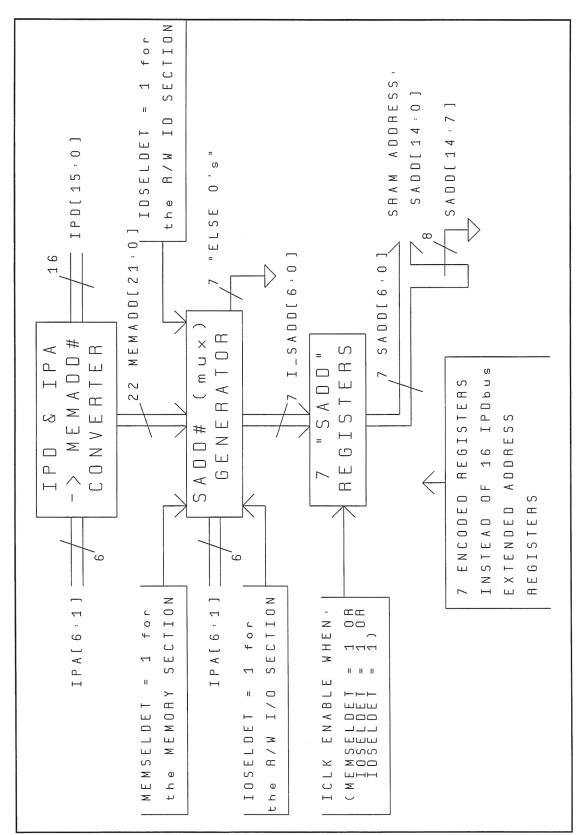

This logic is necessary for the capturing of the extended address bus (IPA[22:7]) presented by IPD[15:0] during the select cycle for memory transfers. Instead of actually using 16 registers for this function, the address is decoded and remapped for the target SRAM address, which is then latched at the end of the select cycle. This technique reduces the number of registers to seven, for capturing SADD[6:0] (SRAM ADDress bus bits  $6 \rightarrow 0$ ). Figure 2-2 presents an overview of this SRAM address generator.

## 2.2.9 Memory Address Remapper

This logic performs an address remapping function on the memory transfer addresses such that only 22 locations are used out of the full 8 MBytes of IPack memory space. This remapping provides for a valid, unique, address hit when 1 of the 22 address lines is asserted to a logic '1' state, with the other 21 address lines being '0'. These 22 memory locations then have their addresses converted, in ascending order, to a sequential address list starting at SADD = 40 hex and ending with SADD = 55 hex. Any other Memory Transfer address values will be ignored as an invalid transfer with no acknowledgement which will result in a bus-time-out error.

## 2.2.10 32-KB SRAMs

These two blocks provide the READ and WRITE locations necessary to implement half of the ID, most of the I/O and all of the memory transfers for the TESTIP. All accesses are byte-lane controlled. The SRAMs were used for economic reasons, since the implementation of one hundred eleven 16-bit READ/WRITE registers would have been prohibitively expensive by any other technique.

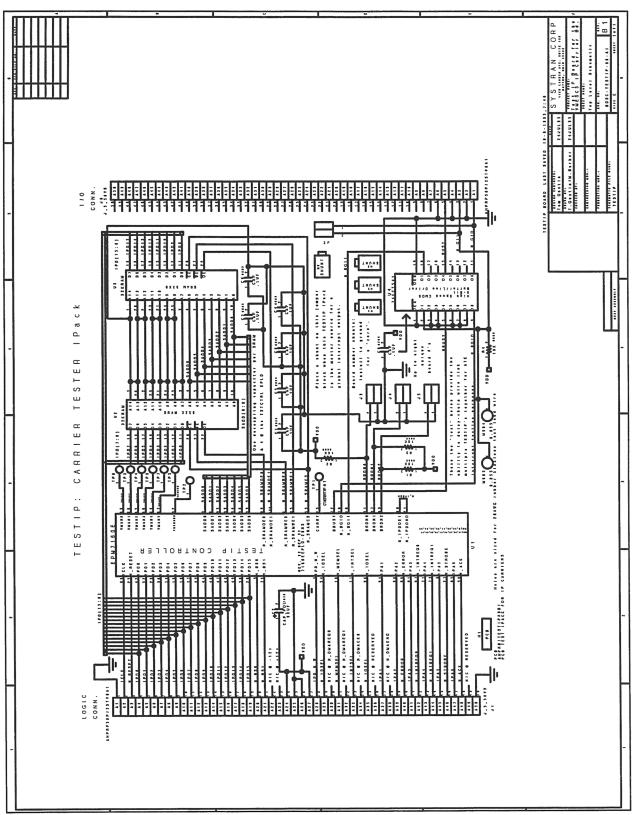

#### 2.3 TESTIP Schematic

There is only a single page schematic for the TESTIP. It is included in Appendix B to this document.

On the left side is the Logic Connector through which all transactions are performed between the TESTIP and its carrier. On the right is U1, the TESTIP Controller EPLD, an ALTERA 7128E device. In the top right portion of the schematic is found two 32 KB SRAM devices, U2 and U3. The bottom right corner contains an octal buffer, 74FCT541, that performs (three channels of) I/O buffering. The I/O connector is on the right side of the schematic. The only other components are passive, board and IC-filtering capacitors and pullup resistors, and four jumper/shunt switches for developing the board number and for automatically self-interrupting during a global-interrupt event.

Figure 2-2 SADDGEN: SRAM's Address Generator Block Diagram

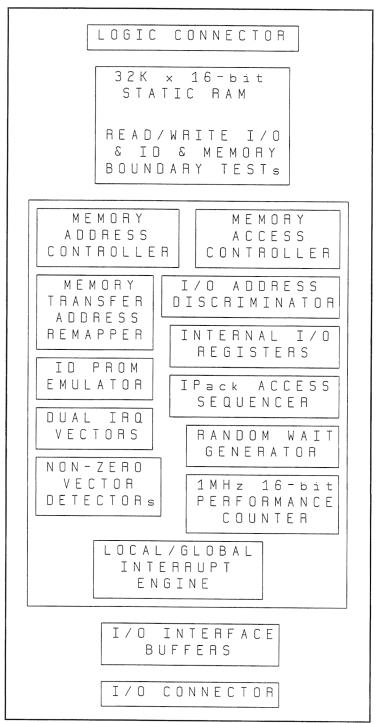

Figure 2-3 presents the TESTIP's logic diagram. The link between the logic diagram and the schematic clearly partitions components and their functions. The logic connector at the top of Figure 2-3 is J1 on the schematic. The next block down corresponds to the pair of SRAM devices at U2 and U3. The largest block on Figure 2-3 depicts U1. The I/O Interface buffer is U4, and the I/O connector is J6.

Figure 2-3 TESTIP's Top Logic Diagram

## 2.4 I/O Accesses

There are two major sections to the I/O map of the TESTIP. The first one consists of 57 locations:16-bit wide READ/WRITE "registers" mapped into the first 57 word locations of the on-board SRAM. All accesses to the SRAM (I/O, ID, and Memory) completely obey byte-lane selections for both WRITEs and READs (unlike most other IPacks which typically provide 16-bit READs regardless of byte-lane selections). The first 57 locations correspond to IPA[6:1] addresses of  $00 \rightarrow 38$  hex, inclusively. On the schematic, these I/O locations directly correspond to SADD[6:0] (SRAM ADDresses) such that the first 57 I/O locations are SADD addresses  $00 \rightarrow 38$  hex.

The remaining group of seven I/O locations are actual registers and pseudo-registers contained within the EPLD described below:.

#### 2.4.1 I/O Location #1

The first EPLD-based I/O location, corresponding to IPA = 39 hex, contains a 16-bit "timer" that runs at a fixed 1 MHz rate when enabled. Since the timer is completely synchronous and is driven by the ICLK, it can be read at any time, on-the-fly. READ accesses ignore the byte-lane control signals such that READs always present the full 16-bit timer value. Any WRITE to this location, including either byte-lane or full word, using any data value, will reset the timer to zero, whether it is running (reset on-the-fly) or stopped.

#### 2.4.2 I/O Location #2

The second EPLD-based I/O location, corresponding to IPA = 3A hex, is a pseudo-register that controls the running of the performance timer. It is a pseudo-register because no real physical registers exist at this location. Any width WRITE access using any data value starts the performance timer. Any width READ access (reads as all zeroes) stops the performance timer. Table 2-1 presents the performance timer controller access types with corresponding functional operations:

Timer Function: Access Location and Type:

STOP TIMER Any READ @ IPA=3A

READ TIMER Any READ @ IPA=39

RESET TIMER Byte/Word WRITE of any data @ IPA=39

START TIMER Byte/Word WRITE of any data @ IPA=3A

PAUSE/CONTINUE Any READ & then any WRITE @ IPA=3A

Table 2-1 Performance Timer Functions and Access Types

#### 2.4.3 I/O Location #3

The third EPLD-based I/O location, corresponding to IPA = 3B hex, is a three-bit, general-purpose control/status register.

- Bit 0, the least significant bit, is the inversion of the N\_ERROR signal. When this bit is set to a '1', the EPLD will assert the N\_ERROR line to its low state for subsequent reading by carriers that have the ability to post the state of this line. When this bit is cleared to a '0', the EPLD will negate the N\_ERROR line to the carrier.

- Bit 1 turns the random-wait-cycle generator on and off. Setting this bit to a '1' enables the insertion of wait cycles for ALL TESTIP accesses, while clearing it to a '0' enables the TESTIP to respond to ALL carrier accesses with no wait cycles.

- Bit 2 is a direct reflection of the logic state of the N\_STROBE signal, for those carriers that provide connectivity to this signal.

On power-up, bits 0 and 1 are cleared to zeroes to negate N\_ERROR and disable wait cycle insertions, respectively. Valid WRITE accesses to this register are byte-lane-sensitive; low-byte or word accesses work; high-byte-only access attempts will result in an acknowledgement but with no register content changes. READs of this register will provide the registered information for bits 0 and 1, the signal state of N\_STROBE for bit 2, and a zero-fill for IPD[15:3].

## 2.4.4 I/O Location #4

The fourth EPLD-based I/O location, corresponding to IPA = 3C hex, is a two-bit interrupt-status register. When bit 0 = '1' it indicates that a level 0 interrupt request is currently being asserted to the carrier via the signal N\_INTREQ0. When bit 1 = '1' it indicates that a level 1 interrupt request is currently being asserted to the carrier via the signal N\_INTREQ1. When this location is read, bits 0 and 1 indicate the interrupt status, while a zero-fill is applied to IPD[15:2]. Interrupt 0 is cleared by a WRITE of a '1' to bit 0 of this register. The WRITE is fully qualified for data = '1' and for byte-lane 0 select; low-byte or word accesses work; data = '0' or high-byte-only access attempts will result in an acknowledgement but with no register content changes. The same is true for the clearing of interrupt level 1 with a WRITE of a '1' to bit 1 of this register. A subsequent READ of the status bit after a clearing event (WRITE of a '1') will indicate that the interrupt has been cleared by the return of a '0' value (WRITE '1'; READ '0'). Both of these bits are set to one value by either a valid WRITE to the interrupt control register (local interrupt request), or the application of a global-interrupt input, provided their corresponding interrupt vectors are non-zero values.

#### 2.4.5 I/O Location #5

The fifth EPLD-based I/O location, corresponding to IPA = 3D hex, is a three-bit interrupt-control register that is tightly coupled to the interrupt-status register (see above).

- A WRITE of a '1' to bit 0 asserts both the interrupt-status bit 0 and the N\_INTREQ0 signal to the carrier, provided the interrupt vector for level 0 is a non-zero value.

- A WRITE of a '1' to bit 1 asserts both the interrupt status bit 1 and the N\_INTREQ1 signal to the carrier, provided the interrupt vector for level 1 is a non-zero value.

- A WRITE of a '1' to bit 2 causes a 250 ns low pulse to appear on the global interrupt-output signal N\_GIO on the I/O connector, regardless of the values in the interrupt vectors.

Any READ of this register will return values of '1' in bits 0 and 1 when local interrupt requests have been generated, while a zero-fill is applied to IPD[15:2].

**NOTE**: Bit 2 of the interrupt request register will always read back as a zero. Bits 0 and 1 are cleared by WRITEs to the interrupt-status register (see above).

## 2.4.6 I/O Locations #6 and #7

The last two EPLD-based I/O locations are a pair of 8-bit interrupt vectors; the next to last I/O location is a vector for interrupt request #0, while the last I/O location provides a vector for interrupt request #1. These locations must be non-zero values for interrupts to be asserted. An in-bound global-interrupt-input and local-interrupt request attempts will be blocked for either or both interrupt requests for zero-value vectors. Global-interrupt inputs can selectively assert interrupt request #0 alone by maintaining vector #1 with a data value of '00'.

## 2.4.7 EPLD-based I/O Defaults

ALL EPLD-based registers are cleared to zero on power-up. This of course does not apply to the N\_STROBE status bit which is hardware signal monitoring only. Figure 2-4 provides a simple summary of the I/O accesses.

```

TESTIP: TEST IPack

I/O ACCESS ADDRESS MAP

IPA[6:1] =

00 -> 38 -

57 x 16 - bit READ/WRITE LOCATIONS

"FULL" ADDRESS DECODING

ODD BYTE. EVEN BYTE. FULL WORD WRITES

EITHER BYTE or FULL WORD READS

SRAM-based I/O "REGISTERS"

39,

16-bit GATED 1MHz TIMER

ANY BYTE/WORD WRITE CAUSES TIMER TO

RESET TO ZERO

3 A ·

PERFORMANCE TIMER CONTROL

ANY BYTE/WORD WRITE STARTS TIMER

ANY READ STOPS TIMER

TIMER RUNNING causes "BUSY" output = 1

ЗΒ ·

CONTROL/STATUS REGISTER

bit O: ERROR SIGNAL CONTROL BIT

N_ERROR ASSERTED (=low) WHEN THIS BIT = 1

N_ERROR NEGATED (=high) WHEN THIS BIT = 0

bit 1 · RANDOM (up to 7) WAIT CYCLES = 1

NO WAIT CYCLES =

DEFAULT = 0: NO WAIT CYCLES

bit 2 · Hardware connection of "N_STROBE"

3 C '

INTERRUPT STATUS REGISTER

bit 0 INTERRUPT #0 ASSERTED = 1

WRITE 1 TO NEGATE INTERRUPT #0

which also clears 30's bit #0

bit 1 · INTERRUPT #1 ASSERTED = 1

WRITE '1' TO NEGATE INTERRUPT #1

which also clears 30's bit #1

30.

INTERRUPT CONTROL REGISTER

bit O·WRITE '1' TO ASSERT INTERRUPT #0

READ FOR CAUSE OF INTERRUPT #0

bit 1 WRITE '1' TO ASSERT INTERRUPT #1

READ FOR CAUSE OF INTERRUPT #1

bit 2 · WRITE '1' TO GENERATE THE "GLOBAL INTERRUPT" 250 nS LOW OUTPUT PULSE

(Self-Clears after PULSE OUTPUT)

NOTE: 30[0] IS CLEARED WHEN 3C[0] IS CLEARED

30[1] IS CLEARED WHEN 3C[1] IS CLEARED

INTERRUPT NOTES:

3D · 1 3D · 0 3C · 1 3C · 0 STATE/NOTES ·

0

٥

n

O NO INTERRUPTS PENDING

0

0

1

LOCALLY-CAUSED INTERRUPT #0

1

0

1

O LOCALLY-CAUSED INTERRUPT #1

1

1

1 LOCALLY-CAUSED INTERRUPTS #0 & #1

0

1 GLOBALLY-CAUSED INTERRUPTS #0 & #1

NEITHER HAVE BEEN SERVICED. YET

0

0

O GLOBALLY-CAUSED INTERRUPTS #1

INTERRUPT #0 HAS ALREADY BEEN SERVICED

Ω

Λ

Ω

1 GLOBALLY-CAUSED INTERRUPTS #0

INTERRUPT #1 HAS ALREADY BEEN SERVICED

3 E ·

INTERRUPT #0 VECTOR REGISTER

3 F ·

INTERRUPT #1 VECTOR REGISTER

BOTH VECTORS IN BYTE LANE #0: IPO[7·0]

POWER-UP DEFAULT = '00'hex FOR BOTH

MUST BE NON-ZERO DATA TO GENERATE INTERRUPTS

```

Figure 2-4 I/O Accesses Summary

## 2.5 Memory Accesses

The memory testing support provided by the TESTIP is a fully-decoded, partial-hit memory map consisting of 22 valid memory locations spread over an 8 MB range; best depicted as a bubble-one addresser over the 22 address lines. Figure 2-5 describes the scheme used. Access attempts to any 16-bit location not listed will result in no acknowledgement and its resultant bus time-out. The VMAN[5:0] labels on the far right side of Figure 2-5 correspond to the TESTIP's test points: TP5, TP7, TP8, TP4, TP3, and TP6, respectively. For each of VMAN[4:0] test points, there are only four valid memory-address conditions that will generate a high-state output; and, only two for VMAN[5]. All 22 valid accesses to the SRAM completely obey byte-lane selections for both WRITEs and READs.

#### 2.6 Identification Accesses

The identification (ID) accesses portion of the TESTIP is significantly different than other IPacks from SYSTRAN Corp.

The ID space is divided evenly between READ-only accesses (per specification), and READ/WRITE accesses (per recommendation).

The lower half of Figure 2-6 presents a simple summary of all of the ID space and the associated data fields and accesses.

## 2.6.1 Configuration ID Space

The first 12 ID locations, IPA =  $00 \rightarrow 0B$  hex contain the standard identification (header) information, typically used for system configuration. These locations are READ-only accesses, with the upper byte set to '00', and the lower byte providing the data depicted in Figure 2-6. These READs are always 16-bits wide as the TSTCTRL EPLD-logic ignores the byte select lines for these accesses. Attempted WRITEs have no effect on the data fields. Acknowledgement is provided for WRITEs for those carriers capable of performing such transfers.

## 2.6.2 Addressing and Number ID Space

The next 20 ID locations, IPA =  $0C \rightarrow 1F$  hex, contain READ-only variable fields. The lower 5 bits, IPD[4:0], have the address of the location being accessed as defined by IPA[5:1], mapped respectively. This "A-in-A" ("Address-in-Address") function is useful for evaluating the address bus for stuck bits, except for IPA[6].

The upper three bits of the lower byte, IPD[7:5], present the board number as described by section 2.7. These READs are 16-bit widths because the EPLD ignores byte-lane selection for accesses in this area. The upper byte always READs '00'. WRITE attempts, while acknowledged, have no effect on the data in this ID space.

| SCHEME  | 7 9 e t          | SH AM S<br>A D DR E S S<br>• S A D D • · |   | 41 | 42 VMANO |   | 4 4 |    | 4 6 VMAN1 |     | / 8 1 | ر<br>6 | A V M A I | 1B / 81 | 7 3    |      | IE VMAN3 | · \     | / 09    | 7        | 52 VMAN4 | 3 / ε    | 7         | SS VMAN5  | (×e          |

|---------|------------------|------------------------------------------|---|----|----------|---|-----|----|-----------|-----|-------|--------|-----------|---------|--------|------|----------|---------|---------|----------|----------|----------|-----------|-----------|--------------|

| ADDRESS | e L              | PHYSICAL A                               |   | 2  | 4        | 8 | 16  | 32 | 6.4       | 128 | 256 4 | 512 4  | 1024 4    | 2048 4  | 4096 4 | 8192 | 16384 4  | 32768 4 | 65536 5 | 131072 5 | 262144 5 | 524288 5 | 1048576 5 | 2097158 5 | (decinal) (h |

| >       | $\leftarrow$     | 4                                        | 1 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 0         |              |

| 0 B     | 2                | 2                                        | 0 | 1  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 0         | ( y se c     |

| Σ<br>W  | ъ                | ю                                        | 0 | 0  | 7        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 0         | ( b 1 r      |

| Σ       | 4                | 4                                        | 0 | 0  | 0        | 1 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 0         | >            |

|         | . 2              | Ŋ                                        | 0 | 0  | 0        | 0 | 7   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 0         |              |

|         | IPA<br>6         | 9                                        | 0 | 0  | 0        | 0 | 0   | 7  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 0         |              |

|         | -                |                                          |   |    |          |   |     |    |           |     |       |        |           |         |        |      |          |         |         |          |          |          |           |           |              |

|         | 0                | 7                                        | 0 | 0  | 0        | 0 | 0   | 0  | П         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 0         |              |

|         | 7                | ۵                                        | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 1   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 0         |              |

|         | 2                | 6 0                                      | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 1     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 0         |              |

|         | r                | 1                                        | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 7      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 0         |              |

|         | 4                | 2 1                                      | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 1         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 0         |              |

| ×       | 5                | 3 1 3                                    | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 1       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 0         |              |

| U       | 9                | 1                                        | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | П      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 0         |              |

| Ф       | s )<br>7         | A .                                      | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 1    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 0         |              |

|         | 0<br>0<br>0<br>0 | IP/<br>6 19                              | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 7        | 0       | 0       | 0        | 0        | 0        | 0         | 0         |              |

| ST      | 9 d d r          | ent<br>7 16                              | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 7       | 0       | 0        | 0        | 0        | 0         | 0         |              |

| Ш       | ed 3             | a 1                                      | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 1       | 0        | 0        | 0        | 0         | 0         |              |

|         | ende<br>2 11     | 9<br>18                                  | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 1        | 0        | 0        | 0         | 0         |              |

| ا م     | e x t e          | D 4                                      | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 1        | 0        | 0         | 0         |              |

| I       | 7                | 3 Y 's                                   | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 7        | 0         | 0         |              |

| S       | 0 .              | M O B                                    | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | ٦         | 0         |              |

| <br> -  | 1 P              | M E                                      | 0 | 0  | 0        | 0 | 0   | 0  | 0         | 0   | 0     | 0      | 0         | 0       | 0      | 0    | 0        | 0       | 0       | 0        | 0        | 0        | 0         | 1         |              |

Figure 2-5 Memory Accesses Summary

## 2.6.3 SRAM-based ID Mapping

The upper 32 locations of the ID space have full WRITE/READ-BACK capability for those carriers with the ability to address and WRITE to this ID space. Figure 2-6 shows the SRAM-based ID mapping scheme of IPA =  $20 \rightarrow 3F$  hex  $\Rightarrow$ SADD[6:0] =  $60 \rightarrow 7F$  hex. As with all other SRAM-based transfers, these ID accesses fully comply with byte-lane selections from the carrier.

Figure 2-6 TESTIP: Test IPack SRAM's Address Map

## 2.7 Board Number

The TESTIP has built into some of its ID fields (see section 2.6, above) a three-bit field that is jumper selectable for identifying individual TESTIP's in multiple board testing scenarios. This scheme provides the ability to allocate unique board numbers for up to eight different TESTIP's on an embedded carrier under test, five on the VMESC5 carrier, or four (or less) for most standard carriers. Figure 2-7 provides the proper jumper selections for all eight board numbers possible.

Figure 2-7 Board Number Jumpers

## 2.8 Timing Diagrams

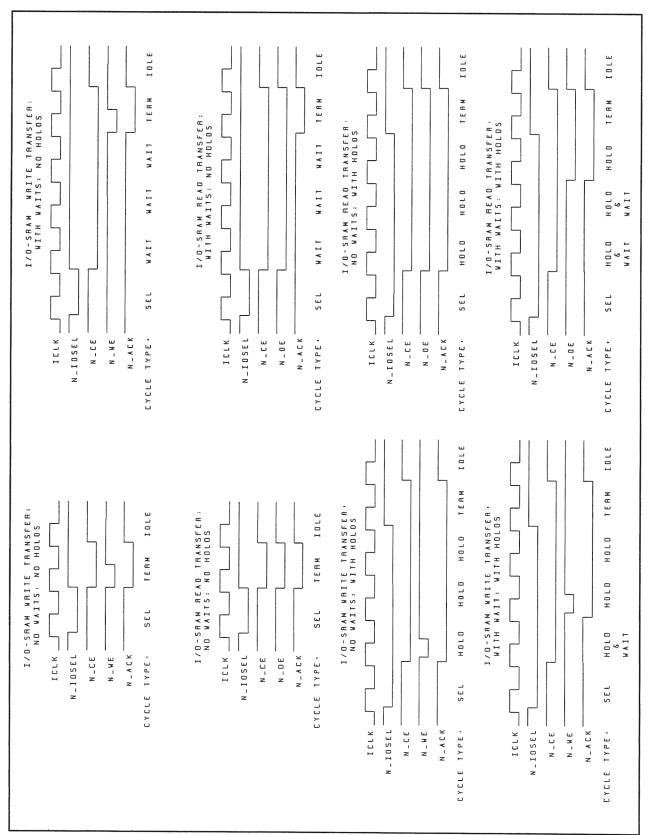

Figures 2-8 through 2-13 present a collection of all of the variations of timing diagrams that are executable by the TESTIP. Most of the variations occur due to WAIT and/or HOLD cycle insertions by the TESTIP and/or Carrier, respectively.

Figure 2-8 presents all of the possible WAIT cycle insertions for all transfer types.

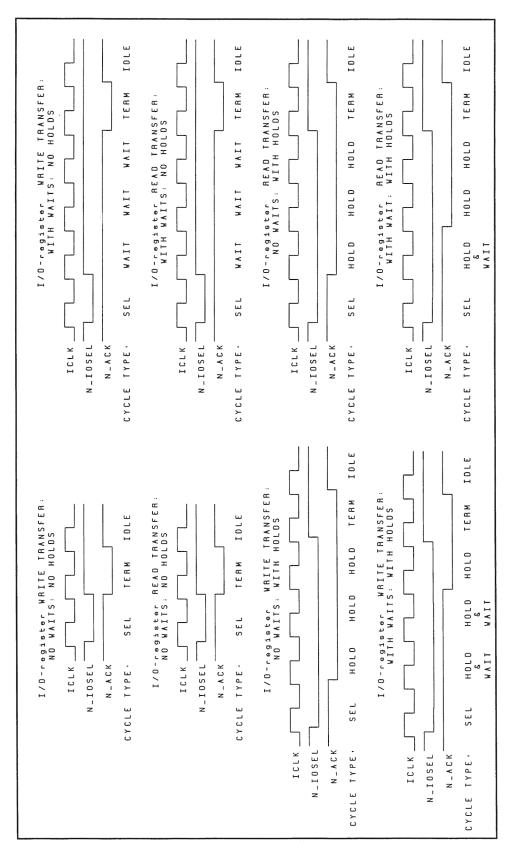

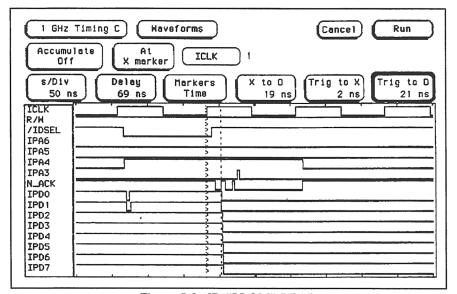

There are two target areas for I/O accesses; the SRAM, and the EPLD-based registers. Figure 2-9 presents all of the possible combinations for the SRAM-based I/O accesses, with variations in READ versus WRITE, with or without wait cycles, and with or without hold cycles. For all three SRAM-based transfer types the "N\_CE" signal is the asserted low SRAM chip (select) enable; the "N\_OE" signal is the asserted low SRAM output enable that is asserted during READ transfers; the "N\_WE" signal is the asserted low SRAM WRITE enable that is asserted during WRITE transfers.

**NOTE**: The rising edge of "N\_WE" performs the actual WRITE This edge precedes the rising edge of ICLK to ensure that data is properly captured.

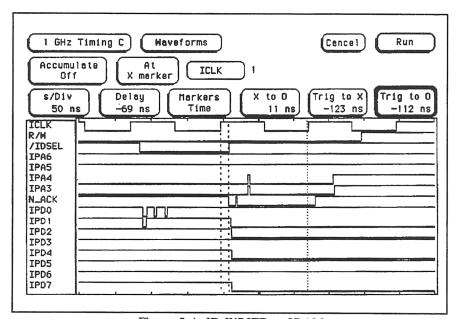

Figure 2-10 presents all of the possible combinations for the EPLD-based I/O registers and pseudo registers accesses, with variations in READ versus WRITE, with or without hold cycles, and with or without wait cycles.

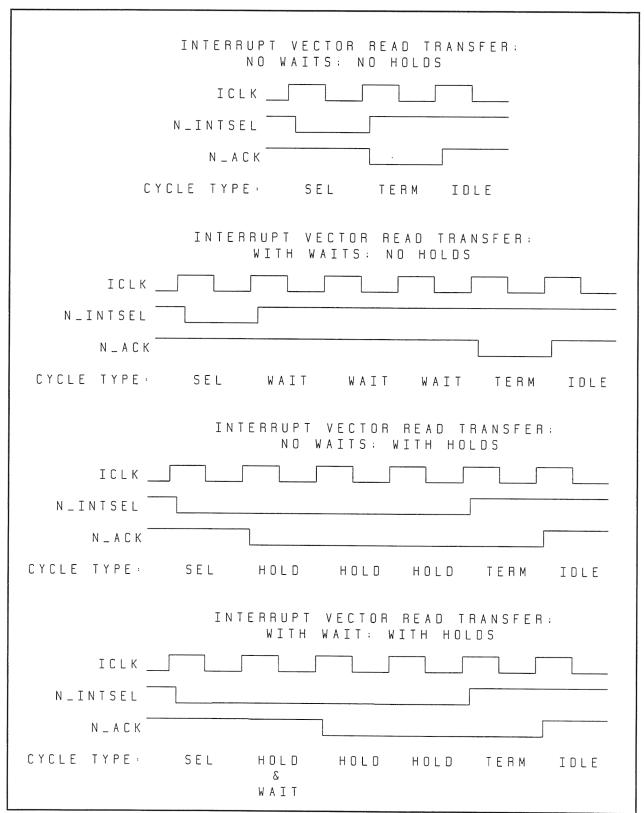

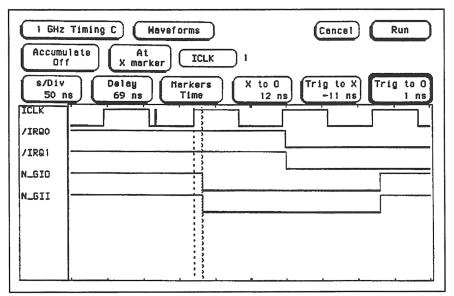

Figure 2-11 presents the only type of IPack transfer that is READ-only—the interrupt vector. The Interrupt vector READ transfer variations are depicted with or without hold cycles, and with or without wait cycles.

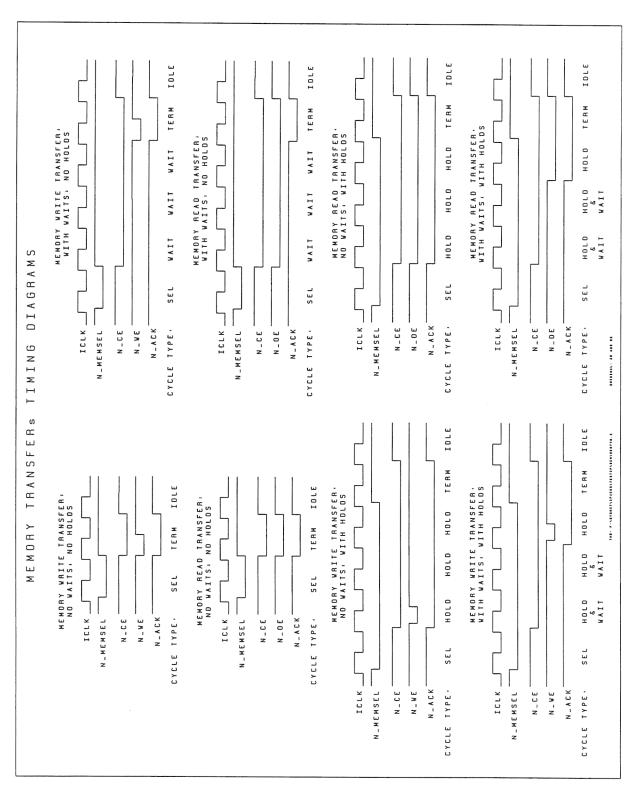

Figure 2-12 demonstrates all of the possible combinations for memory accesses to and from the SRAM, with variations in READ versus WRITE, with or with hold cycles, and with or without wait cycles.

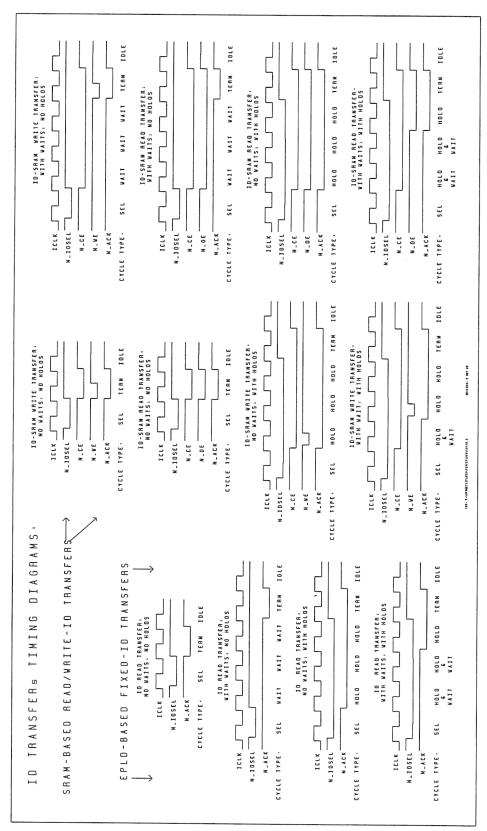

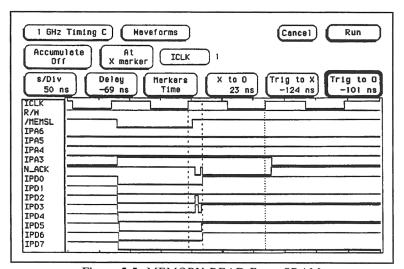

Figure 2-13 presents the 12 different possible timing diagrams for the ID transfers. The READ-only transfers from the lower half of the ID address space is depicted on the left third of Figure 2-13. The SRAM-based WRITE/READ-BACK access combinations for the upper half of the ID space is shown on the right two-thirds of Figure 2-13.

Figure 2-8 WAIT Cycles Timing Diagrams

Figure 2-9 SRAM-based I/O Transfers Timing Diagrams

Figure 2-10 Register-based I/O Transfers Timing Diagrams

Figure 2-11 Interrupt Vector READ Transfers Timing Diagrams

Figure 2-12 Memory Transfers Timing Diagrams

Figure 2-13 ID Transfers Timing Diagrams

# 3.0 HARDWARE INSTALLATION

## 3.1 Unpacking the TESTIP

The contents of the TESTIP shipping packages are listed in Table 3-1:

Table 3-1 Contents of TESTIP Shipping Packages

| QTY | DESCRIPTION                     |  |  |  |  |

|-----|---------------------------------|--|--|--|--|

| 1   | TESTIP Printed Circuit Assembly |  |  |  |  |

| 1   | TESTIP User Manual *            |  |  |  |  |

\* One manual is shipped for each board ordered for orders up to 5 boards. Five manuals will be shipped for orders of over five boards unless additional manuals up to one per board are requested. Extra manuals may be purchased by calling SYSTRAN or by mail. Use the prefix "BTMR-" followed by the product order part number. (e.g. BTMR-TESTIP).

The Printed Circuit Assembly is enclosed in an anti-static box. The box and the manual are packaged together in a larger box. Save the shipping material in case the board needs to be returned.

## 3.2 Visual Inspection of the TESTIP

Examine the TESTIP to determine if any damage occurred during shipping.

#### 3.3 TESTIP Installation

**NOTE:** The TESTIP is an Electrostatic Sensitive Device (ESD). Therefore, the hardware installation of the TESTIP must be conducted on a good anti-static workbench to protect the IPack and carrier boards. The IPack carrier board must be removed from the host system using good ESD practices and moved to an ESD controlled area where the installation of the TESTIP can be completed.

The TESTIP installation requires the following tools:

Table 3-2 TESTIP Installation Tools

| Qty | Description                               |

|-----|-------------------------------------------|

| 1   | ESD Static Control Kit/Ground Strap/Etc.  |

| 1   | Standard Flat Head Screwdriver (Optional) |

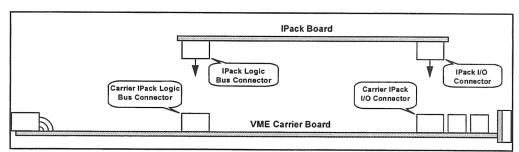

Figure 3-1 Installation of the TESTIP on a VME IPack carrier board.

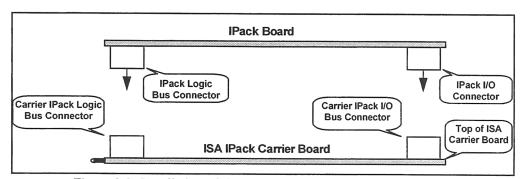

Figure 3-2 Installation of the TESTIP on a ISA IPack carrier board.

Reference Figure 3-1 for the diagram of how the TESTIP is installed on a VME IPack carrier, and Figure 3-2 for installation on an ISA carrier.

Table 3-3 shows the pin assignments for the IPack Logic Bus connector. The signals on the left side of the connector are of the original IPack signal nomenclature, and the signals on the right are those used by SYSTRAN. Table 3-4 shows the pin assignments for the I/O connector. Refer to the IPack Carrier board user's manual for more information.

Referring to the appropriate figures and table described above, perform the following steps. The asterisk (\*) denotes optional items.

- 1. Turn off all power to the host system.

- 2. Remove the target IPack carrier and move it to the ESD controlled area where the installation of the TESTIP can be made.

- 3. Remove the TESTIP from the shipping package and place it on the ESD bench.

- 4. If global interrupts are to be daisy-chained using the solder donuts instead of the I/O connection, wire/solder the TESTIP's together at this time.

- 5. Install the TESTIP onto the carrier board by applying adequate and equal pressure to the TESTIP board at both ends.

- \* 6. Install four M2x5 mm flat head machine screws onto the IPack carrier's IPack connectors.

This completes the installation of the TESTIP to the carrier board.

Table 3-3 IPack Logic Bus Pin Assignments

| Original IPack Signals Names | IPack Logic Bus Pin # | SYSTRAN Signal Names |

|------------------------------|-----------------------|----------------------|

| GND                          | 50                    | GND                  |

| reserved                     | 49                    | RESERVED1            |

| Ack*                         | 48                    | N_ACK                |

| A6                           | 47                    | IPA6                 |

| Strobe*                      | 46                    | N_STROBE             |

| A5                           | 45                    | IPA5                 |

| IntReq1*                     | 44                    | N_INTREQ1            |

| A4                           | 43                    | IPA4                 |

| IntReq0*                     | 42                    | N_INTREQ0            |

| A3                           | 41                    | IPA3                 |

| Error*                       | 40                    | N_ERROR              |

| A2                           | 39                    | IPA2                 |

| DMAEnd*                      | 38                    | N_DMAEND             |

| A1                           | 37                    | IPA1                 |

| reserved                     | 36                    | RESERVED2            |

| IOSel*                       | 35                    | N_IOSEL              |

| DMAck0*                      | 34                    | N_DMACK0             |

| IntSel*                      | 33                    | N_INTSEL             |

| DMAReq1*                     | 32                    | N_DMAREQ1            |

| MemSel*                      | 31                    | N_MEMSEL             |

| DMAReq0*                     | 30                    | N_DMAREQ0            |

| IDSel*                       | 29                    | N_IDSEL              |

| R/W*                         | 28                    | IPR_N_W              |

| +5V                          | 27                    | +5VDC                |

| GND                          | 26                    | GND                  |

| GND                          | 25                    | GND                  |

| +5V                          | 24                    | +5VDC                |

| +12V                         | 23                    | +12VDC               |

| -12V                         | 22                    | -12VDC               |

| BS1*                         | 21                    | N_BS1                |

| BS0*                         | 20                    | N_BS0                |

| D15                          | 19                    | IPD15                |

| D14                          | 18                    | IPD14                |

| D13                          | 17                    | IPD13                |

| D12                          | 16                    | IPD12                |

| D11                          | 15                    | IPD11                |

| D10                          | 14                    | IPD10                |

| D9                           | 13                    | IPD9                 |

| D8                           | 12                    | IPD8                 |

| D7                           | 11                    | IPD7                 |

| D6                           | 10                    | IPD6                 |

| D5                           | 9                     | IPD5                 |

| D4                           | 8                     | IPD4                 |

| D3                           | 7                     | IPD3                 |

| D2                           | 6                     | IPD2                 |

| D2                           | 5                     | IPD1                 |

| D0                           | 4                     | IPD0                 |

| Reset*                       | 3                     |                      |

| CLK                          | 2                     | N_RESET<br>ICLK      |

| GND                          | 1                     | GND                  |

Table 3-4 IPack I/O Connector Pin Assignments

| IPack I/O Pin # | Signal Name   |

|-----------------|---------------|

| ll 50 i         | NO CONNECTION |

| 49              | NO CONNECTION |

| 48              | NO CONNECTION |

| 47              | NO CONNECTION |

| 46              | NO CONNECTION |

| 45              | NO CONNECTION |

| 44              | NO CONNECTION |

| 43              | NO CONNECTION |

| 42              |               |

|                 | NO CONNECTION |

| 41              | NO CONNECTION |

| 40              | NO CONNECTION |

| 39              | NO CONNECTION |

| 38              | NO CONNECTION |

| 37              | NO CONNECTION |

| 36              | NO CONNECTION |

| 35              | NO CONNECTION |

| 34              | NO CONNECTION |

| 33              | NO CONNECTION |

| 32              | NO CONNECTION |

| 31              | NO CONNECTION |

| 30              | NO CONNECTION |

| 29              | NO CONNECTION |

| 28              | NO CONNECTION |

| 27              | NO CONNECTION |

| 26              | NO CONNECTION |

| 25              | NO CONNECTION |

| 24              | NO CONNECTION |

| 23              | NO CONNECTION |

| 22              | NO CONNECTION |

| 21              | NO CONNECTION |

| 20              | NO CONNECTION |

| 19              | NO CONNECTION |

| 18              | NO CONNECTION |

| 17              | NO CONNECTION |

| 16              | NO CONNECTION |

| 15              | NO CONNECTION |

| 14              | NO CONNECTION |

| 13              | NO CONNECTION |

| 12              | NO CONNECTION |

| 11              | NO CONNECTION |

| 10              | NO CONNECTION |

| 9               | NO CONNECTION |

| 8               | NO CONNECTION |

| 7               | NO CONNECTION |

| 6               | GND           |

| 5               | BUSY          |

| 4               | GND           |

| 3               | N_GII         |

| 2               | GND           |

| 1               | N GIO         |

# 4.0 PROGRAMMING GUIDE

This section of the manual describes the operation of the TESTIP from the software perspective, detailing the TESTIP registers and providing programming examples. A more detailed description of the hardware can be found in section 2.0 DESCRIPTION and in section 6.0 TYPICAL APPLICATIONS.

# 4.1 Description

The TESTIP is a general purpose TEST IPack capable of performing all of the well-defined transfer operations for the *IndustryPack Logic Interface Specification Revision 0.7.1*. Its principle function is that of a carrier tester, with provisions for evaluating: the transfer-performance-throughput characteristics, local- and global-interrupt handling capabilities, random-wait-cycle insertions' handling, complete address testing for all transfer types, advanced transfer ability for ID WRITEs, as well as byte-lane selectability for both READ and WRITE transfers for MEMORY, I/O, and ID transactions. Its 16-bit READ-on-the-fly 1 MHz timer and 111 READ/WRITE "memory" locations make it an ideal suplemental IPack when not being used as a carrier tester.

### 4.2 ID PROM Addresses

Table 4-1 shows the TESTIP ID PROM map. The addresses shown are the IPack addresses. To determine the correlation of the local bus to the IPack address, see paragraphs A-4.4: Word Access Address Translation, and A-4.5: Byte Access Address Translation.

Table 4-1 TESTIP ID Address Space Listing

| IPack Address | Description          | Data READ |

|---------------|----------------------|-----------|

| IPA = 00 hex  | ASCII 'I'            | 49 hex    |

| IPA = 01 hex  | ASCII 'P'            | 50 hex    |

| IPA = 02 hex  | ASCII 'A'            | 41 hex    |

| IPA = 03 hex  | ASCII 'C'            | 43 hex    |

| IPA = 04 hex  | SYSTRAN's ID         | 45 hex    |

| IPA = 05 hex  | TESTIP Model Number  | 6D hex    |

| IPA = 06 hex  | Revision Level       | 30 hex    |

| IPA = 07 hex  | Reserved             | 00 hex    |

| IPA = 08 hex  | Low Byte Driver ID   | 00 hex    |

| IPA = 09 hex  | High Byte Driver ID  | 00 hex    |

| IPA = 0A hex  | Number of Bytes Used | 0C hex    |

| IPA = 0B hex  | CRC                  | 2E hex    |

## 4.3 IPack I/O Address Map

The TESTIP I/O Address Map was designed with efficiently located data, control and interrupt registers in the IPack I/O address space (IPA = 00-3F hex). The address detector circuitry is fully decoded.

The first 57 locations in I/O space are 16 bit READ/WRITE locations. The next location (IPA = 39 hex) is the TESTIP 1MHz timer. This timer is reset by performing any byte or word WRITE to the location, a READ gives the current timer value.

IPA 3A hex is the Performance Timer Control register. Any byte/word WRITE starts the timer and any READ stops the timer.

The TESTIP Control/Status register is located at the next location, IPA = 3B hex. Bit 0 is the TESTIP IPack Error Signal Control bit and bit 1 is the Random Wait Cycles bit.

The TESTIP Interrupt Status register is located at the next location, IPA 3C hex. Bit 0 is the assertion flag for interrupt 0, bit 1 is the assertion flag for interrupt 1.

IPA 3D *hex* is the TESTIP Interrupt Control register. Bit 0 is the control bit for interrupt 0, bit 1 is the control bit for interrupt 1.

IPA's 3E and 3F are the Interrupt Vector registers for interrupts 0 and 1, respectively.

Table 4-2 shows the TESTIP register map. The addresses shown are the IPack addresses. To determine the correlation of the local bus to IPack address see paragraphs A.3 Word Access Address Translation and A.4 Byte Access Address Translation.

For further information regarding the TESTIP registers, see Section 2.4.

**IPack Address Bits** Description  $IPA = 00 \rightarrow 38 hex$ [15:0] 57 x 16-bit READ/WRITE locations IPA = 39 hex[15:0] 1 MHz Timer IPA = 3A hex[15:0] Performance Timer Control IPA = 3B hex[XXXX,XXXX] [XXXX,X] [2:0] Control/Status Register Bit 2: READ Only Connection of N\_STROBE Blt 1: Random Wait Cycles (0=OFF, 1=ON) Bit 0: Error Signal Control (0= Negated, 1=Asserted) IPA = 3C hex[XXXX,XXXX] [XXXX,XX] [1:0] Interrupt Status Register Bit 0, 1 = Interrupt 0 Asserted Bit 1, 1 = Interrupt 1 asserted WRITE 1 to Negate. IPA = 3D hex[XXXX,XXXX] [XXXX,X] [2:0] **Interrupt Control Register** Bit 0, 1 = Interrupt 0 Asserted Bit 1, 1 = Interrupt 1 Asserted Bit 2, 1 = Global Interrupt Pulse Asserted IPA = 3E hex[XXXX,XXXX] [7:0] Interrupt Vector 0 (8-bit Register) IPA = 3F hex[XXXX,XXXX] [7:0] Interrupt Vector 1 (8-bit Register)

Table 4-2 TESTIP I/O Address Map

**NOTE**: X = No WRITE, read as zero.

# 4.4 Word Access Address Translation

Table 4-3 shows the relationship between VME, PC-AT, and NUBUS local bus addresses and the IPack address for word accesses. In the table, BASE represents the I/O or ID base address. All addresses are in hexadecimal.

Table 4-3 Word Access Address Translation Table

| VME Bus<br>Address | PC-AT Bus<br>Address | NuBus<br>Address | IPack Address |

|--------------------|----------------------|------------------|---------------|

| BASE + 0           | BASE + 0             | BASE + 2         | IPA = 00 hex  |

| BASE + 2           | BASE + 2             | BASE + 6         | IPA = 01 hex  |

| BASE + 4           | BASE + 4             | BASE + A         | IPA = 02 hex  |

| BASE + 6           | BASE + 6             | BASE + E         | IPA = 03 hex  |

| BASE + 8           | BASE + 8             | BASE + 12        | IPA = 04 hex  |

| BASE + A           | BASE + A             | BASE + 16        | IPA = 05 hex  |

| BASE + C           | BASE + C             | BASE + 1A        | IPA = 06 hex  |

| BASE + E           | BASE + E             | BASE + 1E        | IPA = 07 hex  |

| BASE + 10          | BASE + 10            | BASE + 22        | IPA = 08 hex  |

| BASE + 12          | BASE + 12            | BASE + 26        | IPA = 09 hex  |

| BASE + 14          | BASE + 14            | BASE + 2A        | IPA = 0A hex  |

| BASE + 16          | BASE + 16            | BASE + 2E        | IPA = 0B hex  |

# 4.5 Byte Access Address Translation

Table 4-4 shows the relationship between VME, PC-AT, and NUBUS local bus addresses and the IPack address for byte accesses. In the table, BASE represents the I/O or ID base address. All addresses are in hexadecimal.

Table 4-4 Byte Access Address Translation Table

| VME Bus<br>Address | PC-AT Bus<br>Address | NuBus<br>Address | IPack Address | Byte-lane |

|--------------------|----------------------|------------------|---------------|-----------|

| BASE + 1           | BASE + 0             | BASE + 3         | IPA = 00 hex  | 0         |

| BASE + 0           | BASE + 1             | BASE + 2         | IPA = 00 hex  | 1         |

| BASE + 3           | BASE + 2             | BASE + 7         | IPA = 01 hex  | 0         |

| BASE + 2           | BASE + 3             | BASE + 6         | IPA = 01 hex  | 1         |

| BASE + 5           | BASE + 4             | BASE + B         | IPA = 02 hex  | 0         |

| BASE + 4           | BASE + 5             | BASE + A         | IPA = 02 hex  | 1         |

| BASE + 7           | BASE + 6             | BASE + F         | IPA = 03 hex  | 0         |

| BASE + 6           | BASE + 7             | BASE + E         | IPA = 03 hex  | 1         |

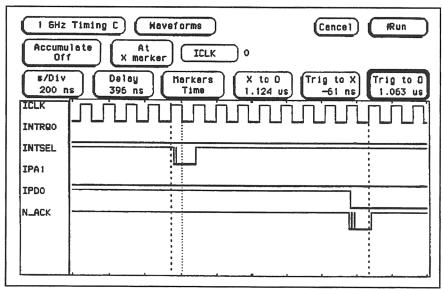

| BASE + 9           | BASE + 8             | BASE + 13        | IPA = 04 hex  | 0         |