## VMIVME-1183 32-Channel P2 Digital Input Board with Change-of-State Interrupts, Sequenceof-Events and Built-in-Test

**Product Manual**

12090 South Memorial Parkway Huntsville, Alabama 35803-3308, USA (256) 880-0444 ◆ (800) 322-3616 ◆ Fax: (256) 882-0859 500-001183-000 Rev. A

A GE Fanuc Company

© Copyright 2003. The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

AMXbus, BITMODULE, COSMODULE, DMAbus, IOMax, IOWorks Foundation, IOWorks Manager, IOWorks Server, MAGICWARE, MEGAMODULE, PLC ACCELERATOR (ACCELERATION), Quick Link, RTnet, Soft Logic Link, SRTbus, TESTCAL, "The Next Generation PLC", The PLC Connection, TURBOMODULE, UCLIO, UIOD, UPLC, Visual Soft Logic Control(ler), *VMEaccess*, VMEbus Access, *VMEmanager*, *VMEmonitor*, VMEnet, VMEnet II, and *VMEprobe* are trademarks and The I/O Experts, The I/O Systems Experts, The Soft Logic Experts, and The Total Solutions Provider are service marks of VMIC.

(I/O man figure)

(IOWorks man figure)

The I/O man figure, IOWorks, IOWorks man figure, UIOC, Visual IOWorks and the VMIC logo are registered trademarks of VMIC.

ActiveX, Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, Windows NT, and XENIX are registered trademarks of Microsoft Corporation.

Celeron and MMX are trademarked, Intel and Pentium are registered trademarks of Intel Corporation.

PICMG and CompactPCI are registered trademarks of PCI Industrial Computer Manufacturers' Group.

Other registered trademarks are the property of their respective owners.

## **Table of Contents**

| List of Figures                                                   |

|-------------------------------------------------------------------|

| List of Tables                                                    |

| Overview                                                          |

| Features                                                          |

| Features (Continued)                                              |

| Functional Description                                            |

| Reference Material List                                           |

| Safety Summary                                                    |

| Ground the System                                                 |

| Do Not Operate in an Explosive Atmosphere15                       |

| Keep Away from Live Circuits                                      |

| Do Not Service or Adjust Alone15                                  |

| Do Not Substitute Parts or Modify System15                        |

| Dangerous Procedure Warnings15                                    |

| Safety Symbols Used in This Manual16                              |

| Chapter 1 - Theory of Operation                                   |

| Overview                                                          |

| Functional Organization                                           |

| VMEbus Interface                                                  |

| Data Transfer Cycles                                              |

| Interrupt Acknowledge Cycles                                      |

| Register Decoder                                                  |

| Debounce Clock                                                    |

| Change-of-State Logic                                             |

| Previous State Data Algorithm                                     |

| Consider the following:                                           |

| "Simultaneous" Data Changes, and the Debounce "Stretching" Effect |

| Inputs                                                            |

| Built-In-Test                                                     |

| Chapter 2 - Configuration and Installation                    |

|---------------------------------------------------------------|

| Unpacking Procedures                                          |

| Physical Installation                                         |

| Before Applying Power: Checklist 39                           |

| Operational Configuration                                     |

| Factory Installed Jumpers 40                                  |

| Board Address and Address Modifier Selection 40               |

| Debounce Timing                                               |

| Input Configurations                                          |

| Connector Description                                         |

| Barrier Terminal Transition Panels                            |

| Chapter 3 - Programming                                       |

| Board ID (BD ID) Register                                     |

| Control and Status Register                                   |

| Data Register                                                 |

| Data FIFO Register                                            |

| Interrupt Processor Control Register                          |

| Interrupt Levels                                              |

| Interrupt Processor COS Vector Register (Offset: \$XXXX0D)    |

| Interrupt Processor Marker Vector Register (Offset: \$XXXX0E) |

| Counter FIFO Register (Offset: \$XXXX10)                      |

| Quadrature Counter Register (Offset: \$XXXX14)                |

| COS Select Register 0                                         |

| COS Select Register 1                                         |

| COS Select Register 2                                         |

| COS Select Register 3                                         |

| COS SEL B/A                                                   |

| Example:                                                      |

| FIFO Count Register (FIFO_CNT) 62                             |

| Counter FIFO Count Register (CTR_FIFO_CNT)                    |

| Channel Interrupt Enable Register (CH_INT_ENA)63              |

| Firmware Revision Register (FREV)                             |

| Quadrature Counter Feature                                    |

| Test Mode                                                     |

| Example Setup:                                                |

| Initialization                                                |

| Chapter 4 - Maintenance                                       |

| Maintenance                                                   |

| Maintenance Prints                                            |

# List of Figures

| Figure 1-1 | VMIVME-1183 Block Diagram                  | 18 |

|------------|--------------------------------------------|----|

| Figure 1-2 | VMIVME-1183 Bus Interface                  | 21 |

| Figure 1-3 | Basic Input Circuitry                      | 31 |

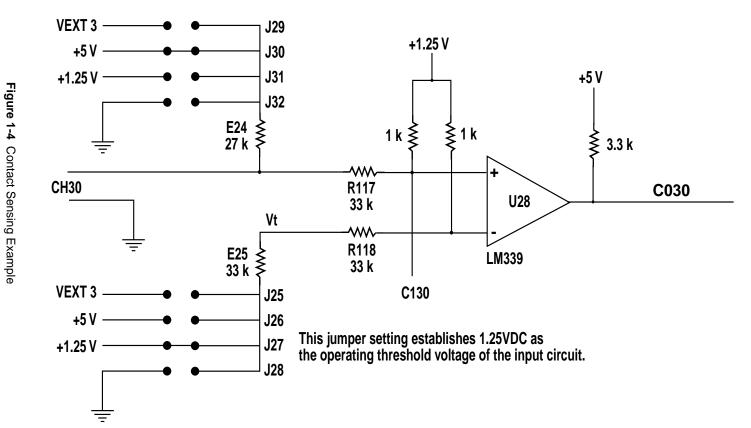

| Figure 1-4 | Contact Sensing Example                    | 32 |

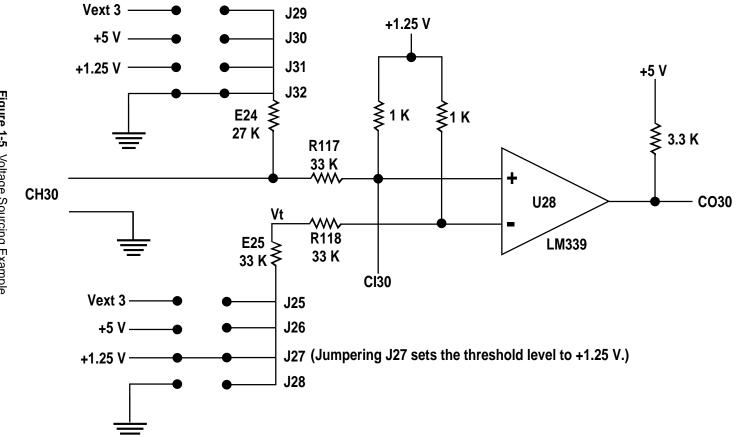

| Figure 1-5 | Voltage Sourcing Example                   | 33 |

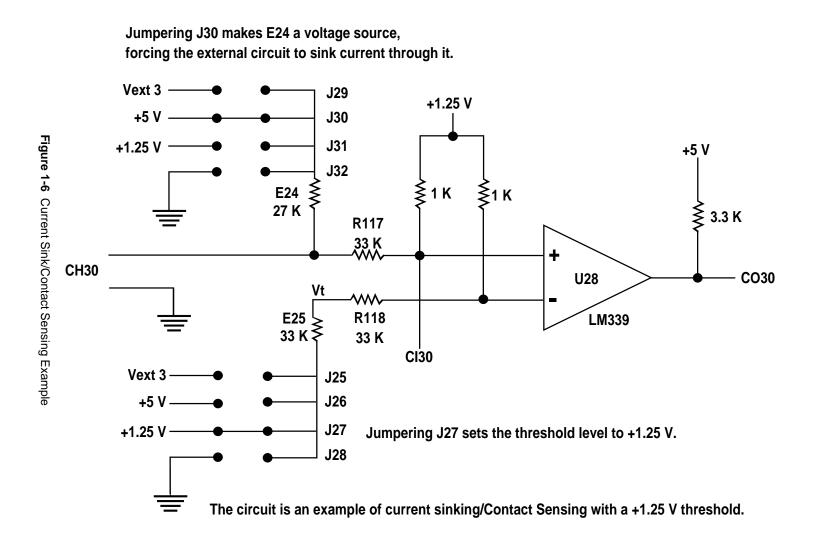

| Figure 1-6 | Current Sink/Contact Sensing Example       | 34 |

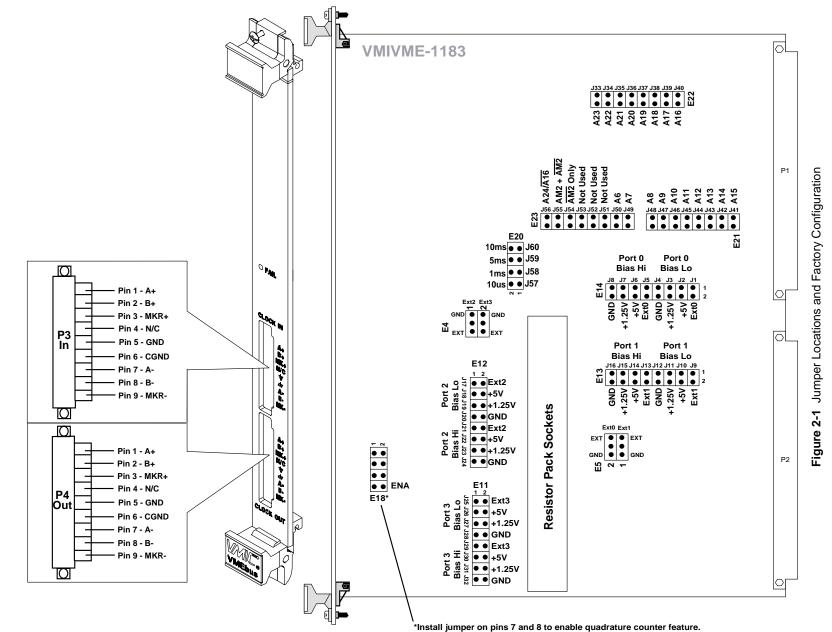

| Figure 2-1 | Jumper Locations and Factory Configuration | 44 |

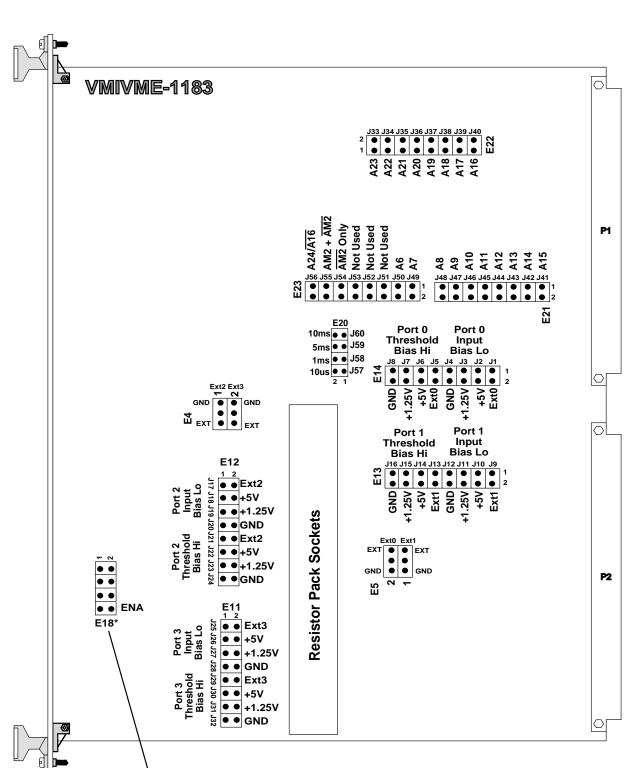

| Figure 2-2 | Input Configuration Worksheet              | 47 |

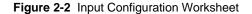

| Figure 2-3 | P2 Connector Pin Layout                    | 49 |

| Figure 2-4 | P3/P4 Connector                            | 51 |

VMIVME-1183 Product Manual

## **List of Tables**

| Table 1-1  | COS States                                                                   | 26   |

|------------|------------------------------------------------------------------------------|------|

| Table 1-2  | Threshold Voltages for E25 = 33 kW, Vt = [(V - 1.25)*(.51)] + 1.25 (Default) | . 35 |

| Table 1-3  | Input and Threshold Biasing Resistor Pack Position Assignment                | . 35 |

| Table 2-1  | Jumper Functions and Factory Configuration                                   | 41   |

| Table 2-1  | Jumper Functions and Factory Configuration (Continued)                       | 42   |

| Table 2-1  | Jumper Functions and Factory Configuration (Concluded)                       | 43   |

| Table 2-2  | Jumper E20 (Debounce Timing)                                                 | . 45 |

| Table 2-3  | Threshold Voltages                                                           | . 46 |

| Table 2-4  | P2 Pin Assignments                                                           | . 50 |

| Table 2-5  | P3 Connector Pinout                                                          | . 51 |

| Table 2-6  | P4 Connector Pinout                                                          | . 51 |

| Table 3-1  | VMIVME-1183 Address Map                                                      | 54   |

| Table 3-2  | Board ID Register Bit Map                                                    | . 54 |

| Table 3-3  | Control and Status Register Bit Map                                          | . 55 |

| Table 3-4  | Data Register Bit Map                                                        | . 56 |

| Table 3-5  | Data FIFO Register Bit Map                                                   | . 57 |

| Table 3-6  | Interrupt Processor Control Register Bit Map                                 | . 58 |

| Table 3-7  | COS Select Register 0 Bit Map                                                | . 60 |

| Table 3-8  | COS Select Register 1 Bit Map                                                | . 60 |

| Table 3-9  | COS Select Register 2 Bit Map                                                | . 60 |

| Table 3-10 | COS Select Register 3 Bit Map                                                | . 61 |

| Table 3-11 | FIFO Count Register Bit Map                                                  | . 62 |

| Table 3-12 | Counter FIFO Count Register Bit Map                                          | . 62 |

| Table 3-13 | Channel Interrupt Enable Register Bit Map                                    | . 63 |

| Table 3-14 | P3/P4 Connector Pinout                                                       | . 64 |

| Table 3-15 | Example Setup of the VMIVME-1183                                             | . 67 |

VMIVME-1183 Product Manual

## **Overview**

## Contents

| Functional Description             | 13 |

|------------------------------------|----|

| Reference Material List            | 14 |

| Safety Summary                     | 15 |

| Safety Symbols Used in This Manual | 16 |

### Introduction

#### Features

The VMIVME-1183 is a 32-channel P2 input board with Change-of-State (COS) interrupt capabilities. The interrupt control logic can be programmed to issue an interrupt upon specific state changes. The user selects the state change to use by programming the Control and Status Register (CSR) and the COS Select register for the desired activity. This board will store up to 512 state changes as long as the COS logic is enabled. This will prevent the board from losing a state change during interrupt servicing. The VMIVME-1183 supports Built-In-Test (BIT). BIT registers are available to test the active components of the input data paths on the board. The board also supports byte, word and longword data transfers during basic input data operations.

The following is a list of some of the features of the VMIVME-1183:

- 32 channels of high voltage digital inputs

- Eight inputs are grouped together and called an input port. Each port can be configured by the user to monitor one of the following input circuits:

- Contact closure

- Current sinking

- Voltage sourcing

- User-configurable input voltage thresholds

- Incoming data is available for direct VMEbus read cycles

- Data can be read using 8-, 16-, or 32-bit data transfers

#### **Features (Continued)**

- Each channel can be independently set up by the user to perform the following functions:

- No interrupts (data only)

- Rising edge only interrupts

- Falling edge only interrupts

- Any edge interrupts

- Sequence of Events logging with or without optional time stamping (See "Quadrature Counter Feature" on page 64.)

- Differential or Single-Ended inputs for Quadrature Counter, with marker signal input and dasiy-chaining capability

- The test registers can be activated at any time to test the integrity of the active components on the board

- This board complies with the VMEbus Specification Rev. C.1

- The board can be jumpered to respond to short I/O accesses or to standard data I/O accesses

## **Functional Description**

The VMIVME-1183 is a 32-channel digital input board. The input circuitry is user configured by positioning SIP resistors and jumpers. This is explained in detail in Chapter 2 of this manual. The inputs can be set up to monitor either voltage sourcing or current sinking external circuits. Contacts are handled like switching transistors. Once the hardware has been configured and the board is installed in a system, you can start monitoring the external circuits. The data ports are always available for VMEbus data transfers. Simply read the address of the port you want and record the state of the external circuits. This data is available in byte, word or longword accesses.

The board can be programmed to interrupt the system based on a change in the inputs. Change-of-State (COS) monitors the logical state of the inputs. When any bit in an input channel changes its state (for example going from a logic one (1) to a logic zero (0)), and the COS logic is set to trigger on just such an event, then an interrupt will be issued to the host CPU. The COS logic can be told (via the Control and Status Register) to issue interrupts upon certain conditions, such as the falling edge described above, and is bit-specific. The following list states the types of state changes the board will respond to:

- No interrupts (processed as data only)

- Rising edge only

- · Falling edge only

- Any edge (or state change)

The VMIVME-1183 stores state changes in on-board FIFO memory. The board can be configured to clear an interrupt request when the FIFO is empty, or an interrupt has been acknowledged (ROAK). This way, if a COS occurs while a previous COS is waiting for service, or during the interrupt service routine, it is saved and will issue its interrupt request as soon as the interrupts are re-enabled.

Additional capabilities are to record Sequence of Events (SOE). In this mode, when a specified change of state occurs on any of the inputs, the previous state of the inputs are stored in the FIFO, followed by the current state of those inputs. Additionally, a counter value from a front panel input quadrature counter (single-ended, or differential) is stored in a separate FIFO to give the SOE an optional time stamp. The quadrature counter feature is available in COS mode as well, See "Quadrature Counter Feature" on page 64.

Test registers are provided to periodically check the integrity of the VMIVME-1183. The registers are mapped into the same address locations as the Input Data registers. By enabling Test Mode in the Control and Status Register 1 (CSRCSR), and then writing data to these registers, you can check the active components of the input data paths on the board and assure yourself of the board's performance. The test register data will not affect the external circuitry. It only overrides the incoming data. When you disable Test Mode, the test data no longer affects the input data.

## **Reference Material List**

For a detailed explanation of the VMEbus and its characteristics, refer to "The VMEbus Specification" available from:

VITA

VMEbus International Trade Association

7825 East Gelding Dr., No. 104

Scottsdale, AZ 85260

(602) 951-8866

FAX: (602) 951-0720

www.vita.com

Physical Description and Specifications: Refer to Product Specification, 800-001183-000 available from:

VMIC

12090 South Memorial Pkwy. Huntsville, AL 35803-3308, USA (256) 880-0444 (800) 322-3616 Fax: (256) 882-0859 www.vmic.com

The following Application and Configuration Guides are available from VMIC to assist in the selection, specification, and implementation of systems based upon VMIC's products:

| Title                                                          | Document No.   |

|----------------------------------------------------------------|----------------|

| Digital Input Board Application Guide                          | 825-000000-000 |

| Change-of-State Application Guide                              | 825-000000-002 |

| Digital I/O (with Built-in-Test) Product Line Description      | 825-000000-003 |

| Synchro/Resolver (Built-in-Test) Subsystem Configuration Guide | 825-000000-004 |

| Analog I/O Products (with Built-in-Test) Configuration Guide   | 825-000000-005 |

| Connector and I/O Cable Application Guide                      | 825-000000-006 |

### **Safety Summary**

The following general safety precautions must be observed during all phases of the operation, service, and repair of this product. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture and intended use of this product.

VMIC assumes no liability for the customer's failure to comply with these requirements.

#### Ground the System

To minimize shock hazard, the chassis and system cabinet must be connected to an electrical ground. A three-conductor AC power cable should be used. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet.

#### Do Not Operate in an Explosive Atmosphere

Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.

#### Keep Away from Live Circuits

Operating personnel must not remove product covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### Do Not Service or Adjust Alone

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### Do Not Substitute Parts or Modify System

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to VMIC for service and repair to ensure that safety features are maintained.

#### **Dangerous Procedure Warnings**

Warnings, such as the example below, precede only potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

**STOP:** Dangerous voltages, capable of causing death, are present in this system. Use extreme caution when handling, testing and adjusting.

## Safety Symbols Used in This Manual

**STOP:** This symbol informs the operator the that a practice or procedure should not be performed. Actions could result in injury or death to personnel, or could result in damage to or destruction of part or all of the system.

**WARNING:** This sign denotes a hazard. It calls attention to a procedure, a practice, a condition, which, if not correctly performed or adhered to, could result in injury or death to personnel.

**CAUTION:** This sign denotes a hazard. It calls attention to an operating procedure, a practice, or a condition, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the system.

**NOTE:** Calls attention to a procedure, a practice, a condition or the like, which is essential to highlight.

# **Theory of Operation**

## Contents

| Overview                |  |

|-------------------------|--|

| Functional Organization |  |

| VMEbus Interface        |  |

| Register Decoder        |  |

| Change-of-State Logic   |  |

| Inputs                  |  |

| Built-In-Test           |  |

### **Overview**

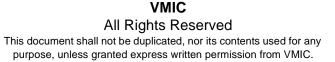

The board functions are broken down into seven major blocks as shown in Figure 1-1 below. These blocks are:

- Bus interface

- Register decoder

- Interrupt Processor (IP)

- Change-of-State (COS) logic

- Input circuits

- Built-in-Test (BIT) registers

- Quadrature counter

The bus interface contains the VMEbus interface logic, the board's address decoding logic and the data steering logic. The register decoder selects which of the data registers (BD ID, CSR, IP, BIT or input) are to be used during a data transfer. The IP interface contains the logic to control the IP and interface it with the VMEbus interrupt bus. The COS logic determines if a change-of-state has occurred, issues the interrupt request (when necessary) and controls the FIFOs data flow. The input circuits contain the hardware to configure the topology (the shape or type of circuit), and their trigger thresholds. The CSR contains the control and enables.

Figure 1-1 VMIVME-1183 Block Diagram

During **DATA ONLY** operations, the board monitors the external circuitry. When the board's address decoder decides the board is being accessed, it clocks the inputs into data registers. In other words, it takes a snapshot of the external world. The data is steered to the correct VMEbus data lines, DTACK\* is asserted, and the board re-arms its address decoder for another cycle. These types of transfers are always available to the user. They will have no effect upon the COS or SOE logic.

During **INTERRUPT CYCLES**, the Interrupt Processor (IP) handles the board functions. When the COS logic issues an interrupt request to the IP, it also stores the incoming data in the associated FIFOs. The IP issues an interrupt request to the host CPU and waits for the proper Interrupt Acknowledge cycle. When the IP responds to the acknowledge cycle, it places the programmed vector for the interrupt service routine upon the VMEbus. The interrupt service routine reads the FIFO's data, which clears its interrupt request if Release On FIFO Empty (ROFE) is enabled.

## **Functional Organization**

The VMIVME-1183 is divided into the following functional categories. Refer to Figure 1-1 on page 18. All of these functions are discussed in detail in this section:

- VMEbus interface

- Data transfer cycles

- Interrupt acknowledge cycles

- Register decoder

- IP interface

- Change-of-State logic

- Inputs

- Built-in-Test

- Quadrature Counter

## **VMEbus Interface**

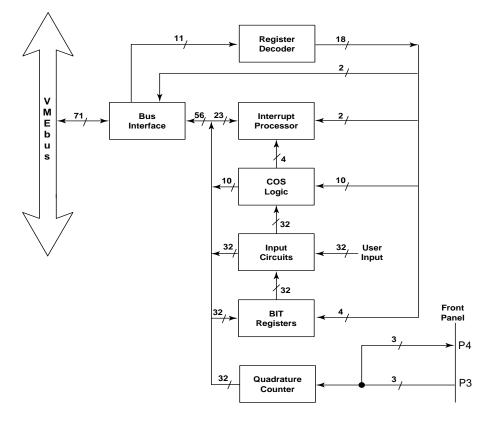

The bus interface logic seen in Figure 1-2 below consists of bus signal buffers and transceivers that meet the VMEbus specification loading requirements. The address decoder (or board-select logic) can respond to standard or short data I/O accesses. The steering logic selects which of the VMEbus data lines are to be connected to the board's Internal Data Bus (IDB) and which direction the data will flow. The Board Identification (BD ID) register, the Control and Status Register (CSR) and the COS Select registers are considered part of the bus interface logic.

Figure 1-2 VMIVME-1183 Bus Interface

#### **Data Transfer Cycles**

The Standard(A24)/Short(A16) jumper establishes the upper address line decoding. If this jumper is installed, the board will only respond to standard A24 data accesses. If the jumper is not installed, the board will only respond to short (A16) I/O accesses. The board's factory default configuration is to respond to short (A16) I/O accesses.

The address decoder compares the 18 address lines (A06 through A23) and the six address modifier lines (AM0 through AM5) with preset conditions. The address lines, the STD(A24)/SHT(A16)CSR line and the AM2 line have jumpers that are used to establish the base address of the board. When a jumper is installed the corresponding address line is compared to a logic zero (0). When the bus address and the address modifier matches the preset address, the board will respond to the bus cycle.

The AM2 line can be jumpered to respond to a specific state (logic HIGH or LOW) or to either logic state. If the jumper is omitted, the board will respond to supervisory data accesses only. If the jumper is in the AM2 position (J53), the board will respond to nonprivileged data accesses only. However, a second jumper (J54) is available for AM2 operations. In this position (AM2 + AM2), the board will respond to either supervisory or nonprivileged accesses.

**CAUTION: DO NOT** install both jumpers J53 and J54. This will short the VMEbus AM2 signal line to ground and disrupt system operations.

When the decoder determines that the board is being accessed, the VMEbus state is stored in a register and the BD\_SEL lines are activated. The board-select line clocks the input registers and records the state of the external circuits. The register decoder uses the bus state information to place the proper data on the IDB, and to energize the proper VMEbus interface data transceivers. The bus interface then issues DTACK\* and watches the Data Strobes (DS0\* and DS1\*). When both Data Strobes are asserted HIGH the decoder resets itself and waits for the next matching address. The cycle then restarts. The BD ID register has a fixed value of \$5D00.

CSR is used to control the basic functions of the board. The even addressed byte of CSR controls the board's test mode and the front panel Fail LED.

When test mode is active, the BIT registers are activated. Data written will overwrite the external inputs. This method allows test data to be used to determine the "health" of the board. By comparing the written data with the read data. The BIT registers occupy the same board addresses as the input data ports, making programming BIT functions easier. The Fail LED is under user control and can be turned OFF when the board is working properly. Two bits of the CSR (Bits 13 and 12) are used to monitor the COS memory device (FIFO). Bit 12 (FIFO\_Full) and Bit 13 (FIFO\_Empty), allow the user to monitor the current condition of the FIFO. If a FIFO is full, any new data will be lost. All bits in the CSR are available during read operations with the exception of Bit 8, 7, 6, 5 and 4 which are reserved. Bit 11 (COS/SOE) of CSR, determines the mode of operation for the board.

The BD ID, CSR, BIT, IP, FIFO and the input registers can be accessed on a byte, word or longword boundary. Please refer to the memory map in Chapter 3 of this manual for the actual relative address locations for these registers. The BD ID is at the base address of the board with the CSR stacked above it, followed by Data/BIT, the COS/SOE FIFO, then the IP control and vector registers. Followed by the longword location where the current value of the SOE quadrature counter can be read. The COS Select 0 through 3 registers are placed next. COS Select registers 0 through 3 controls the monitoring mode (data only, rising/falling/any edge) of each channel. Word and longword accesses are placed upon even address boundaries. This allows you to read the BD ID and the CSR in one longword access. You cannot read the odd byte of the BD ID and the even byte of the CSR in one word transfer.

#### Interrupt Acknowledge Cycles

During Interrupt Acknowledge (IACK\*) cycles, only the lowest three address lines are valid. They carry the interrupt level being acknowledged by the host CPU, bypassing the address decoder and activating the IP. If the IP has an interrupt pending, it places its vector on the bus and issues a DTACK\*. If not, the IP passes the IACKIN\* signal to the IACKOUT\* line.

If the interrupting FIFO is not empty after the interrupt service routine is read and ROAK is selected, then a new interrupt will be generated by the IP as soon as interrupts are enabled. If ROFE is selected, the interrupt will not be released until the FIFO is empty. When more than one longword of data is in the FIFO, a new interrupt occurred before the old one was read by the CPU. If the FIFO gets full, the state changes are too fast for the system to handle.

**NOTE:** If the COSs come faster than the CPU can service, interrupt starvation will occur, keeping the regular programs from executing. Please keep this in mind when designing your system.

## **Register Decoder**

The register decoder, using the five lowest address lines and the data strobes, selects which of the registers is placed on the IDB. The decoder is used during any board access. It is a simple demultiplexer scheme. The address lines are decoded when the board select lines are asserted. Based upon the address lines and the data strobes, the proper register or registers are activated or clocked. A memory map showing the relative addresses for each register used by this board is listed in Chapter 3 of this manual.

## **Debounce Clock**

The debounce clock (DBNC\_CLK) is derived from the VMEbus system clock and is not intended as a synchronizing clock. The COS logic clock signal is the VMEbus clock. The debounce clock is started when a COS condition is detected. This allows for a lower latency, with the glitch-reduction capability of the debounce clock.

## **Change-of-State Logic**

The COS logic bases its action upon the state of its select lines COS\_SEL\_x\_A and COS\_SEL\_x\_B (A and B for short). These lines are controlled by the COS register values. The states are listed in Table 1-1 below:

| SEL B | SEL A | COS Logic's Action        |

|-------|-------|---------------------------|

| 0     | 0     | COS, passing data only    |

| 0     | 1     | COS on rising edges only  |

| 1     | 0     | COS on falling edges only |

| 1     | 1     | COS on any edge           |

Table 1-1

COS States

The COS logic writes data into a FIFO based on the board configuration and the state stored in the new and old data registers. The COS logic decides when to load data into the FIFO. When a channel (bit) is used as data only (no interrupts), the data changes are not clocked into the FIFO. During the interrupt routine, as a COS is occurring, the logic continues to load the new state into the FIFO through the old data registers. The FIFO stores the new state until the states are read by the host. Until then, the FIFO continues to issue interrupt requests to the IP.

#### **Previous State Data Algorithm**

The definition of previous state data is central to a system that detects changes of state. Since all incoming data is compared to this previous data state, what this previous state data is, and when it is stored is critical to the proper operation of the COS state machine.

First of all, several definitions are in order. A "flagged" Change-Of-State (COS) occurs when one or more data input channel's logic state changes in a way that the VMIVME-1183 has been programmed to detect. For example, if Channel 3 changes from a one (1) logic state to a zero (0) logic state, and the COS Select Register has been programmed to detect falling edges for Channel 3, then Channel 3 has caused a "flagged" COS event. A non-flagged COS event would occur if the logic level on Channel 3 changed from a logic zero (0) to a logic one (1), with falling edge detection enabled. Flagged COS data is the value of all of the input channels when one or more "flagged" changes of state have occurred. Non-flagged COS data is data in which one or more channels change state, but are not flagged for saving.

There are two approaches to choosing when input channel data is saved as previous state data:

• Store the value of the inputs only when a flagged COS event occurs.

• Store incoming data at some predetermined rate, or when any COS event, flagged or not, occurs.

On the VMIVME-1183, as incoming data completes the debounce cycle, if no flagged changes of state are detected, all 32 channels of data are clocked into the previous data buffer. The reason for this is to record the non-flagged COS events that will cause the flagged COS events to be detected. If a flagged COS event does occur, the changed state of the inputs is stored after the COS FIFO is written.

#### Consider the following:

Channel 16 of the COS circuit is programmed to detect rising edge events. The initial condition of Channel 16 is a logic one (1). At some indeterminate point in time, Channel 16's value drops to a logic zero (0). Then, at some future time, Channel 16's value changes back to a logic one (1). If data has been saved to the previous data register only when flagged COS events occur, then the 0 - 1 change of state may be missed since the recording of the previous state of Channel 16 may have been recorded due to a 0 - 1 change on Channel 16 itself. This would cause the previous data value of Channel 16 to be one (1). However, if the input channel data is periodically stored to the previous state register when no flagged COS events are occurring, then the 0 - 1 transition is detected because the zero (0) value of Channel 16 would have been saved.

#### "Simultaneous" Data Changes, and the Debounce "Stretching" Effect

When conducting Device Verification Testing (DVT), or production testing a digital I/O board, a common test utilized is the "walking ones" test. In this test, all input channels are set to zero (0), and a one (1) is written to each successive channel in the following manner:

| State 0 | 00000000 |

|---------|----------|

| State 1 | 00000001 |

| State 2 | 00000010 |

| State 3 | 00000100 |

In this test, two channels are actually changing value after State 1. In State 2, channel 0 has changed from a one (1) to a zero (0), and channel 1 has changed from a zero to a one. In an ideal world, these changes occur simultaneously, and are seen as a single COS event. In actuality, factors can be introduced which will make the arrival of signals on different channels non-simultaneous. Comparators have different times on

rising vs. falling edges. Trace lengths, both inside and outside of FPGAs, can have slightly different lengths. Cables between sensors and I/O boards may not be of precisely matched lengths. If any of the above conditions occur, then data transmitted simultaneously on two or more channels may not arrive simultaneously at the COS detection circuitry.

A factor which aggravates this situation is the need for the inputs to the FPGA containing the COS detection circuitry to be synchronized to a common clock. If two incoming signals arrive as little as 2 nanoseconds skewed, the first arriving signal may arrive just before the synchronizing rising clock edge, and the second signal may arrive just after the rising clock edge. If this occurs, then skew between the two signals is now stretched to the period of the synchronizing clock, which on the VMIVME-1183 is 16 MHz. Another factor, which can skew "simultaneous" signals to a greater extent, is the debounce clock. In a situation where two incoming signals are skewed by one or more synchronizing clock cycles, the synchronized incoming signals can encounter another early-late condition (as was in the synchronizing clock) with the debounce circuitry. Since the COS detection and FIFO circuitry runs at the VMEbus clock rate, the first arriving signal will have encountered, been processed by the COS circuit, and stored in the COS FIFO (if it was a flagged COS event) before the second arriving signal has passed the debounce circuitry. If the second signal was also a flagged COS, then two COS events would be stored in the COS FIFO. This "double-hit" COS event can also show what appears to be an invalid state condition. Consider the following example:

Channel 5 is flagged for rising edge events. Channel 4 is flagged for falling edge events. The CSR is set to SOE (Sequence-Of-Events) mode. In testing, a walking ones test is performed. The expected COS FIFO output is:

|                  | Channel 5            | Channel 4 |

|------------------|----------------------|-----------|

| Previous State 1 | 0                    | 1         |

|                  | 01 to 10 change occu | ırs here  |

| COS State 1      | 1                    | 0         |

The actual FIFO output, due to skew introduced by cabling, synchronizing clock skewing, and debounce skewing, is as follows:

|                | <u>Ch</u>        | annel 4             | <u>Channel 5</u>                |

|----------------|------------------|---------------------|---------------------------------|

| Previous State | 21               | 1                   | 0                               |

|                | 01 to 10 change  | occurs here, but Ch | annel 4 lags Channel 5 by 3nsec |

| COS State 1    |                  | 1                   | 1                               |

|                |                  |                     |                                 |

|                |                  | Channel 4           | Channel 5                       |

|                | Previous State 2 | 1                   | 1                               |

|                | COS State 2      | 0                   | 1                               |

It appears, from the recovered COS FIFO data, that the previous state, and the current state have been logically "anded" together in COS State 1 and Previous State 2, while the perceived correct COS data does not appear until COS State 2. When viewed on a logic analyzer, the incoming data skew may have been as little as 3 or 4 nsec, but due to synchronizing clock skew stretching and debounce skew stretching, the saved COS sequence appears as two separate events.

If the Channel 4 COS detection circuitry had not been set to detect falling edges, a perceived erroneous result would still occur, but only Previous State 1 and COS State 1 would have occurred. This would still leave the tester with the impression that the values of the previous state (01) and final state (10) had somehow been logically "Anded" together.

A better approach to a walking ones test would be to reset the input channels to all zeros (0s) between walking a one from one channel to the next. This allows for the various skews to settle, and still allows the tester to detect channel cross-talk, which is one of the primary purposes of the walking ones testing.

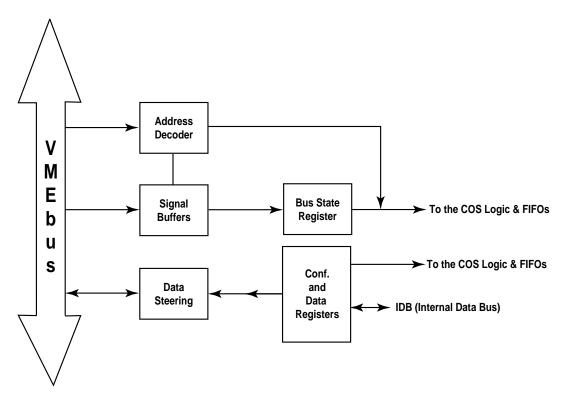

#### Inputs

The input circuit topology (or type of circuit) is controlled by the user. Figure 1-3 on page 31 shows the basic circuit. It depicts the circuitry for input channel 30. The user can configure this circuit to monitor the various external inputs by simply adjusting the position of jumpers that control the common pins (pin 1) of the input bias resistors RP2 and RP3. Figure 1-5 on page 33 shows the voltage sourcing input circuit. Figure 1-6 on page 34 depicts the current sinking input topology. For monitoring contacts-to-ground, use the current sinking input circuit of Figure 1-6 on page 34. If you are monitoring contacts-to-power, use the voltage sourcing inputs of Figure 1-5 on page 33.

Once the input topology has been chosen, the trip threshold must be established. This is done by adjusting the voltage at the V<sub>t</sub> point. The threshold voltage equation for a threshold resistor of 33 k $\Omega$  is V<sub>t</sub> = [(V- 1.25)\*(.51)] + 1.25 V, where V is selected by the user via a jumper field (E11 through E14). This jumper sets V to ground, +1.25V, +5V or whatever the external input voltage Vext is. Table 1-2 on page 35 lists the values for some commonly used values of V.

This biasing arrangement is done on a byte-by-byte basis. E24 and the jumpers shown in the figures control the input channels 31 through 24. This is input byte 0. Byte 1 is controlled in the same manner by E27 and the jumpers shown in Figure 1-1 on page 18 under the column name Byte 1. J12 is in this column. Byte 2 is controlled in the same manner by E9 and the jumpers shown in Figure 1-1 on page 18 under the column name Byte 2. J20 is in this column. Byte 3 is controlled in the same manner by E7 and the jumpers shown in Figure 1-1 on page 18 under the column name Byte 2. J20 is in this column. Byte 3 is controlled in the same manner by E7 and the jumpers shown in Figure 1-1 on page 18 under the column name Byte 3. J5 is in this column. Table 1-2 on page 35 is valid for these input ports as well.

With this arrangement, each of the input ports can have a different configuration. For example, input Byte 0 can be a voltage sourcing input with a 3.2 V threshold for 5 V signals. Byte 1 could be a current sinking input using a 6.7 V trip level for 12 V inputs. Byte 2 may be set up to handle logic levels. This is a voltage sourcing input using the 1.25 V threshold and 5 V inputs. This circuit is not a true TTL input, but it will work with TTL signals. Finally, Byte 3 can be set to monitor some switches. This is done by using the current sinking topology with a threshold voltage of 6.7 V for 12 V signals. This shows just one of the ways this board can be configured. See Chapter 2 for a detailed discussion on how to configure the board. As you can see, the board can monitor a variety of inputs at the same time just by placing jumpers in the right places on the board.

These jumpers set up the type of input the external circuit will see. Grounding resistor pack E24 will require an external voltage source input. Using any of the other jumpers will show the external circuitry a current sink input with the shown voltage level.

Figure 1-3 Basic Input Circuitry

Inputs

This jumper setting supplies a 5VDC pullup path to the inputs. When the relay is open the inputs are pulled up to 5VDC and the input turns on. When the relay is closed, the pullup is eliminated and the input turns off.

Jumpering J32 grounds the input resistor, forcing the external circuit to source voltage across it.

Inputs

34

| V      | Vt       |

|--------|----------|

| 0 V    | 0.61 V   |

| 1.25 V | 1.25 V   |

| 5 V    | 3.16 V   |

| 12 V   | *6.73 V  |

| 24 V   | *12.85 V |

| 28 V   | *14.89 V |

| 48 V   | *25.09 V |

| 66 V   | *34.27 V |

**Table 1-2** Threshold Voltages for  $E25 = 33 \text{ k}\Omega$ ,  $V_t = [(V - 1.25)^*(.51)] + 1.25$  (Default)

NOTE: \*Requires external voltage source for bias and input.

| Channels      | Input Bias | Threshold Bias |

|---------------|------------|----------------|

| 0 through 7   | E7         | E6             |

| 8 through 15  | E9         | E8             |

| 16 through 23 | E27        | E28            |

| 24 through 31 | E24        | E25            |

Table 1-3 Input and Threshold Biasing Resistor Pack Position Assignment

## **Built-In-Test**

The VMIVME-1183 is designed with Built-In-Test (BIT) internal logic. Special output registers are provided to permit writing data to the board. This data is written to the same addresses as the input data registers. This way you can check a particular input byte. These registers are enabled via a test mode bit in the CSR (see Chapter 3 for programming information concerning this bit). Once these registers are enabled, the data stored will overwrite the external inputs. The data read can be compared with the written data. In this manner, the "health" of the board can be determined. BIT is always available to the user. There is only one test mode bit in the CSR. When you enable test mode, all of the BIT registers are enabled. You cannot enable the output registers on a byte-by-byte basis.

Since BIT affects the input data, it will also affect the COS logic. If this is not desired, set the COS mode to "No Interrupts" (see the COS selection table). The COS logic simply samples the input data at the rising edge of the debounce clock. Changing input data will be sensed by the COS logic and appropriate action, if any, will be taken. This way, the COS logic and the FIFO data capture registers can be tested. However, if any "real-time" data previously stored in the FIFO must be dealt with in some manner, testing should be done with an empty FIFO. This way the data in the FIFO reflects the BIT data and not some residual external data.

Since BIT also overwrites the external inputs, any toggle changes in the external signals during testing will be lost. For example, if a valid input signal goes from low to high and then back to low, (or vice versa) before testing is done, it will be lost. A "valid input" is an input state that is present at the rising edge of the VMEbus clock.

NOTE: BIT should occur during system resets or before data acquisition begins.

A front panel Fail LED is available to the user. It is illuminated at power-up or after a system reset and can be extinguished under program control upon the successful completion of diagnostic testing. It can be used for any purpose you wish. For example, it can be used to display data activity.

# **Configuration and Installation**

# Contents

| Unpacking Procedures      | 38 |

|---------------------------|----|

| Physical Installation     | 39 |

| Operational Configuration | 40 |

| Input Configurations      | 46 |

| Connector Description     | 48 |

# Introduction

This chapter describes the installation and configuration of the board. Cable configuration, jumper/switch configuration and board layout are illustrated in this chapter.

# **Unpacking Procedures**

**CAUTION:** Some of the components assembled on VMIC's products may be sensitive to electrostatic discharge and damage may occur on boards that are subjected to a high-energy electrostatic field. When the board is placed on a bench for configuring, etc., it is suggested that conductive material should be inserted under the board to provide a conductive shunt. Unused boards should be stored in the same protective boxes in which they were shipped.

Upon receipt, any precautions found in the shipping container should be observed. All items should be carefully unpacked and thoroughly inspected for damage that might have occurred during shipment. The board(s) should be checked for broken components, damaged printed circuit board(s), heat damage, and other visible contamination. All claims arising from shipping damage should be filed with the carrier and a complete report sent to VMIC together with a request for advice concerning the disposition of the damaged item(s).

# **Physical Installation**

CAUTION: Do not install or remove the boards while power is applied.

### **Before Applying Power: Checklist**

Before installing the board in a VMEbus system, check the following items to ensure that the board is ready for the intended application.

- 1. Review *Factory Installed Jumpers* on page 40 and Table 2-1 on page 41 to verify that all the desired jumpers are in place. To change the board address or address modifier response, refer to *Board Address and Address Modifier Selection* on page 40. \_\_\_\_\_

- 2. Review *Input Configurations* on page 46 to configure the input circuits for the desired operation. \_\_\_\_\_

- 3. Have the I/O cables, with the proper mating connectors, been connected to the input/output connector P2? Refer to *Connector Description* on page 48 for a description of the P2 connector. \_\_\_\_\_

- 4. Have the sections pertaining to theory and programming (Chapter 1 and 3) been reviewed and applied to the system requirements? \_\_\_\_\_

- 5. De-energize the equipment and insert the board into an appropriate slot of the chassis. While ensuring that the board is properly aligned and oriented in the supporting card guides, slide the board smoothly forward against the mating connector until firmly seated.

# **Operational Configuration**

The VMIVME-1183 Board's base address and I/O access mode are determined by field replaceable, on-board jumpers. This section describes the use of these jumpers. The locations and function of all the jumpers on the VMIVME-1183 are shown in Figure 2-1 on page 44 and Table 2-1 on page 41.

### **Factory Installed Jumpers**

Each VMIVME-1183 is configured at the factory with the specific jumper arrangement shown in Figure 2-1 on page 44. The factory configuration establishes the following functional baseline for the board, and ensures that all essential jumpers are installed.

- Base address is set to 0000 HEX

- Short supervisory and short nonprivileged I/O accesses

- Input biasing of 1.25 V, threshold biasing of 1.25 V

- Current sinking inputs

- A 10 µs debounce time

#### **Board Address and Address Modifier Selection**

The jumper field shown in Figure 2-1 on page 44 shows the jumpers and their associated address weights. The values of these bits is determined by the presence or absence of a jumper shunt. When a jumper shunt is installed the address bit's value must be a "zero" for a match. If the jumper shunt is omitted, the value is a "one" to get a match. Therefore, a shunt is installed at every "zero" in the base address to be assigned to this board.

This board is designed to respond to standard (A24) or short (A16) address ranges. Jumper J56 is used to establish the address range for the board. With a jumper shunt omitted from J56 the board will operate in the **standard** address region. In this mode, the upper 8 (A16 to A23) address lines will be ignored. Thus, the jumpers for those address lines can be removed. If J56 jumper shunt is installed, then these lines will be decoded. Therefore, they must be configured as the base address demands.

Jumpers J54 and J55 determine which address modifier the board will respond to during data transfers (see Figure 2-1 on page 44). These jumpers determine supervisory or nonprivileged transfers. Installing a jumper at J54 selects nonprivileged transfers only. Omitting both jumpers will have the board respond only to supervisory accesses. But by installing a jumper at J55, the board will accept either I/O access.

**NOTE:** DO NOT install both jumpers. If J54 or J55 is installed, the AM2 line wil be grounded and this will disrupt the system's operations.

| 2 | 2 |  |

|---|---|--|

|---|---|--|

Г

| RefName/FunctionFactory<br>ConfigurationJ1External Voltage for the threshold biasing of INPUT BYTE 0OMITTEDJ2+5 V for the threshold biasing of INPUT BYTE 0OMITTEDJ3+1.25 V for the threshold biasing of INPUT BYTE 0INSTALLEDJ4For grounding the threshold biasing network of INPUT BYTE 0OMITTEDJ5External Voltage for the input biasing of INPUT BYTE 0OMITTEDJ6+5 V for the input biasing of INPUT BYTE 0OMITTEDJ6+5 V for the input biasing of INPUT BYTE 0OMITTEDJ8For grounding the input network of INPUT BYTE 0OMITTEDJ8For grounding the input network of INPUT BYTE 0OMITTEDJ9External Voltage for the threshold biasing of INPUT BYTE 1OMITTEDJ10+5 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1OMITTEDJ12For grounding the threshold network of INPUT BYTE 1OMITTEDJ13External Voltage for the input biasing of INPUT BYTE 1OMITTEDJ14+5 V for the input biasing of INPUT BYTE 1OMITTEDJ15+1.25 V for the input biasing of INPUT BYTE 1OMITTEDJ16For grounding the input biasing of INPUT BYTE 1OMITTEDJ17External Voltage for the input biasing of INPUT BYTE 1OMITTEDJ18+5 V for the input biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ116For grounding the input biasing of INPUT BYTE 2                                                                                                                                                                                                                                                                                                                                                              | Ref |                                                             | Factory       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------|---------------|

| J1       External Voltage for the threshold biasing of INPUT BYTE 0       OMITTED         J2       +5 V for the threshold biasing of INPUT BYTE 0       OMITTED         J3       +1.25 V for the threshold biasing of INPUT BYTE 0       INSTALLED         J4       For grounding the threshold biasing of INPUT BYTE 0       OMITTED         J3       External Voltage for the input biasing of INPUT BYTE 0       OMITTED         J6       +5 V for the input biasing of INPUT BYTE 0       OMITTED         J7       +1.25 V for the input biasing of INPUT BYTE 0       OMITTED         J8       For grounding the input network of INPUT BYTE 0       OMITTED         J8       For grounding the input network of INPUT BYTE 0       OMITTED         J9       External Voltage for the threshold biasing of INPUT BYTE 1       OMITTED         J10       +5 V for the threshold biasing of INPUT BYTE 1       OMITTED         J11       +1.25 V for the threshold biasing of INPUT BYTE 1       OMITTED         J12       For grounding the threshold network of INPUT BYTE 1       OMITTED         J13       External Voltage for the input biasing of INPUT BYTE 1       OMITTED         J14       +5 V for the input biasing of INPUT BYTE 1       OMITTED         J15       +1.25 V for the input biasing of INPUT BYTE 1       OMITTED         J14 <th></th> <th>Name/Function</th> <th>•</th>                                                                                                                                                                                                                                                                       |     | Name/Function                                               | •             |

| J2+5 V for the threshold biasing of INPUT BYTE 0OMITTEDJ3+1.25 V for the threshold biasing of INPUT BYTE 0INSTALLEDJ4For grounding the threshold biasing network of INPUT BYTE 0OMITTEDJ5External Voltage for the input biasing of INPUT BYTE 0OMITTEDJ6+5 V for the input biasing of INPUT BYTE 0INSTALLEDJ7+1.25 V for the input biasing of INPUT BYTE 0OMITTEDJ8For grounding the input network of INPUT BYTE 0OMITTEDJ9External Voltage for the threshold biasing of INPUT BYTE 1OMITTEDJ10+5 V for the input biasing of INPUT BYTE 1OMITTEDJ10+5 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1OMITTEDJ12For grounding the threshold network of INPUT BYTE 1OMITTEDJ13External Voltage for the input biasing of INPUT BYTE 1OMITTEDJ14+5 V for the input biasing of INPUT BYTE 1OMITTEDJ15+1.25 V for the input biasing of INPUT BYTE 1OMITTEDJ16For grounding the input biasing of INPUT BYTE 1OMITTEDJ17External Voltage for the threshold biasing of INPUT BYTE 2OMITTEDJ18+5 V for the input biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the input biasing of INPUT BYTE 2OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ12For grounding the input biasing of INPUT BYTE 2OMITTEDJ13External Voltage for the threshold bias                                                                                                                                                                                                                                                                                                                                                             | Des |                                                             | Configuration |

| J2+5 V for the threshold biasing of INPUT BYTE 0OMITTEDJ3+1.25 V for the threshold biasing of INPUT BYTE 0INSTALLEDJ4For grounding the threshold biasing network of INPUT BYTE 0OMITTEDJ5External Voltage for the input biasing of INPUT BYTE 0OMITTEDJ6+5 V for the input biasing of INPUT BYTE 0INSTALLEDJ7+1.25 V for the input biasing of INPUT BYTE 0OMITTEDJ8For grounding the input network of INPUT BYTE 0OMITTEDJ9External Voltage for the threshold biasing of INPUT BYTE 1OMITTEDJ10+5 V for the input biasing of INPUT BYTE 1OMITTEDJ10+5 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1OMITTEDJ12For grounding the threshold network of INPUT BYTE 1OMITTEDJ13External Voltage for the input biasing of INPUT BYTE 1OMITTEDJ14+5 V for the input biasing of INPUT BYTE 1OMITTEDJ15+1.25 V for the input biasing of INPUT BYTE 1OMITTEDJ16For grounding the input biasing of INPUT BYTE 1OMITTEDJ17External Voltage for the threshold biasing of INPUT BYTE 2OMITTEDJ18+5 V for the input biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the input biasing of INPUT BYTE 2OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ12For grounding the input biasing of INPUT BYTE 2OMITTEDJ13External Voltage for the threshold bias                                                                                                                                                                                                                                                                                                                                                             | J1  | External Voltage for the threshold biasing of INPUT BYTE 0  | OMITTED       |

| J3+1.25 V for the thershold biasing of INPUT BYTE 0INSTALLEDJ4For grounding the threshold biasing network of INPUT BYTE 0OMITTEDJ5External Voltage for the input biasing of INPUT BYTE 0OMITTEDJ6+5 V for the input biasing of INPUT BYTE 0OMITTEDJ7+1.25 V for the input biasing of INPUT BYTE 0OMITTEDJ8For grounding the input network of INPUT BYTE 0OMITTEDJ9External Voltage for the threshold biasing of INPUT BYTE 1OMITTEDJ10+5 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1OMITTEDJ12For grounding the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1OMITTEDJ12For grounding the threshold network of INPUT BYTE 1OMITTEDJ13External Voltage for the input biasing of INPUT BYTE 1OMITTEDJ14+5 V for the input biasing of INPUT BYTE 1OMITTEDJ15+1.25 V for the input biasing of INPUT BYTE 1OMITTEDJ16For grounding the input biasing of INPUT BYTE 1OMITTEDJ17External Voltage for the threshold biasing of INPUT BYTE 2OMITTEDJ18+5 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ16For grounding the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ20For grounding th                                                                                                                                                                                                                                                                                                                                                             | J2  |                                                             | OMITTED       |

| J4For grounding the threshold biasing network of INPUT BYTE 0<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ5External Voltage for the input biasing of INPUT BYTE 0<br>INSTALLEDOMITTEDJ6+5 V for the input biasing of INPUT BYTE 0<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ8For grounding the input network of INPUT BYTE 0<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ9External Voltage for the threshold biasing of INPUT BYTE 1<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ10+5 V for the threshold biasing of INPUT BYTE 1<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ13External Voltage for the input biasing of INPUT BYTE 1<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ14+5 V for the input biasing of INPUT BYTE 1<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ13External Voltage for the input biasing of INPUT BYTE 1<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ14+5 V for the input biasing of INPUT BYTE 1<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ16For grounding the input biasing of INPUT BYTE 2<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ17External Voltage for the threshold biasing of INPUT BYTE 2<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ17External Voltage for the input biasing o                                                                                                               | J3  | 0                                                           | INSTALLED     |

| USE ONLY ONE OF THESE FOUR JUMPER POSITIONSJ5External Voltage for the input biasing of INPUT BYTE 0OMITTEDJ6+5 V for the input biasing of INPUT BYTE 0INSTALLEDJ7+1.25 V for the input biasing of INPUT BYTE 0OMITTEDJ8For grounding the input network of INPUT BYTE 0OMITTEDJ9External Voltage for the threshold biasing of INPUT BYTE 1OMITTEDJ10+5 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+5 V for the threshold biasing of INPUT BYTE 1OMITTEDJ12For grounding the threshold network of INPUT BYTE 1OMITTEDJ13External Voltage for the input biasing of INPUT BYTE 1OMITTEDJ14+5 V for the input biasing of INPUT BYTE 1OMITTEDJ15+1.25 V for the input biasing of INPUT BYTE 1OMITTEDJ16For grounding the input biasing of INPUT BYTE 1OMITTEDJ17External Voltage for the input biasing of INPUT BYTE 1OMITTEDJ18+5 V for the input biasing of INPUT BYTE 1OMITTEDJ19+1.25 V for the input biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ20For grounding the threshold network of INPUT BYTE 2OMITT                                                                                                                                                                                                                                                                                                                                                                | J4  | For grounding the threshold biasing network of INPUT BYTE 0 | OMITTED       |

| J6+5 V for the input biasing of INPUT BYTE 0INSTALLEDJ7+1.25 V for the input biasing of INPUT BYTE 0OMITTEDJ8For grounding the input network of INPUT BYTE 0OMITTEDJ9External Voltage for the threshold biasing of INPUT BYTE 1OMITTEDJ10+5 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1OMITTEDJ12For grounding the threshold network of INPUT BYTE 1OMITTEDJ13External Voltage for the input biasing of INPUT BYTE 1OMITTEDJ14+5 V for the input biasing of INPUT BYTE 1OMITTEDJ15+1.25 V for the input biasing of INPUT BYTE 1OMITTEDJ16For grounding the input biasing of INPUT BYTE 2OMITTEDJ17External Voltage for the threshold biasing of INPUT BYTE 2OMITTEDJ18+5 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ12External Voltage for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ20For grounding the threshold network of INPUT BYTE 2OMITTEDJ21External Voltage for the input biasing of INPUT BYTE 2OMITTEDJ22+5 V for the inp                                                                                                                                                                                                                                                                                                                                                             |     | USE ONLY ONE OF THESE FOUR JUMPER POSITIONS                 |               |

| J6+5 V for the input biasing of INPUT BYTE 0INSTALLEDJ7+1.25 V for the input biasing of INPUT BYTE 0OMITTEDJ8For grounding the input network of INPUT BYTE 0OMITTEDJ9External Voltage for the threshold biasing of INPUT BYTE 1OMITTEDJ10+5 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1OMITTEDJ12For grounding the threshold network of INPUT BYTE 1OMITTEDJ13External Voltage for the input biasing of INPUT BYTE 1OMITTEDJ14+5 V for the input biasing of INPUT BYTE 1OMITTEDJ15+1.25 V for the input biasing of INPUT BYTE 1OMITTEDJ16For grounding the input biasing of INPUT BYTE 2OMITTEDJ17External Voltage for the threshold biasing of INPUT BYTE 2OMITTEDJ18+5 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ12External Voltage for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ20For grounding the threshold network of INPUT BYTE 2OMITTEDJ21External Voltage for the input biasing of INPUT BYTE 2OMITTEDJ22+5 V for the inp                                                                                                                                                                                                                                                                                                                                                             | 15  | External Voltage for the input biasing of INPLIT RVTE 0     | OMITTED       |

| J7+1.25 V for the input biasing of INPUT BYTE 0OMITTEDJ8For grounding the input network of INPUT BYTE 0OMITTEDJ9External Voltage for the threshold biasing of INPUT BYTE 1OMITTEDJ10+5 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1OMITTEDJ12For grounding the threshold network of INPUT BYTE 1INSTALLEDJ13External Voltage for the input biasing of INPUT BYTE 1OMITTEDJ14+5 V for the input biasing of INPUT BYTE 1OMITTEDJ15+1.25 V for the input biasing of INPUT BYTE 1OMITTEDJ16For grounding the input biasing of INPUT BYTE 1OMITTEDJ17External Voltage for the threshold biasing of INPUT BYTE 2OMITTEDJ18+5 V for the input biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the input biasing of INPUT BYTE 2OMITTEDJ17External Voltage for the threshold biasing of INPUT BYTE 2OMITTEDJ18+5 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ20For grounding the threshold network of INPUT BYTE 2OMITTEDJ21External Voltage for the input biasing of INPUT BYTE 2OMITTEDJ22+5 V for the threshold biasing of INPUT BYTE 2OMITTEDJ23+1.25 V for the input biasing of INPUT BYTE 2OMITTEDJ24For grounding the input biasing of INPUT BYTE 2OMITTEDJ24For grounding the input bias                                                                                                                                                                                                                                                                                                                                                             |     |                                                             |               |

| J8For grounding the input network of INPUT BYTE 0<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ9External Voltage for the threshold biasing of INPUT BYTE 1<br>J10<br>+5 V for the threshold biasing of INPUT BYTE 1<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ11<br>J12+1.25 V for the threshold biasing of INPUT BYTE 1<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ13<br>J14<br>t +5 V for the input biasing of INPUT BYTE 1<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ14<br>J15<br>t +1.25 V for the input biasing of INPUT BYTE 1<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ16<br>J17<br>For grounding the input biasing of INPUT BYTE 1<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ17<br>J18<br>t 5 V for the threshold biasing of INPUT BYTE 2<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ19<br>J20<br>J20<br>For grounding the threshold biasing of INPUT BYTE 2<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ21<br>J22<br>L23<br>L41.25 V for the threshold biasing of INPUT BYTE 2<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ21<br>L24<br>L25 V for the threshold biasing of INPUT BYTE 2<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ21<br>L24<br>L25 V for the input biasing of INPUT BYTE 2<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ21<br>L25 V for the input biasing of INPUT BYTE 2<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ22<br>L45 V for the input biasing of INPUT BYTE 2<br>L35 V for the input biasing of INPUT BYTE 2<br>USE ONLY ONE OF THESE FOUR JUMPER POSITIONSOMITTEDJ22<br>L45 V for the input biasing of |     |                                                             |               |

| USE ONLY ONE OF THESE FOUR JUMPER POSITIONSJ9External Voltage for the threshold biasing of INPUT BYTE 1OMITTEDJ10+5 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1INSTALLEDJ12For grounding the threshold network of INPUT BYTE 1OMITTEDJ13External Voltage for the input biasing of INPUT BYTE 1OMITTEDJ14+5 V for the input biasing of INPUT BYTE 1OMITTEDJ15+1.25 V for the input biasing of INPUT BYTE 1OMITTEDJ16For grounding the input biasing network of INPUT BYTE 1OMITTEDJ17External Voltage for the threshold biasing of INPUT BYTE 2OMITTEDJ18+5 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ20For grounding the threshold network of INPUT BYTE 2OMITTEDJ21External Voltage for the input biasing of INPUT BYTE 2OMITTEDJ22+5 V for the input biasing of INPUT BYTE 2OMITTEDJ23+1.25 V for the input biasing of INPUT BYTE 2OMITTEDJ24For grounding the input biasing network of INPUT BYTE 2OMITTEDJ24For grounding the input biasing network of INPUT BYTE 2OMITTED                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |                                                             |               |

| J10+5 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1INSTALLEDJ12For grounding the threshold network of INPUT BYTE 1OMITTEDJ13External Voltage for the input biasing of INPUT BYTE 1OMITTEDJ14+5 V for the input biasing of INPUT BYTE 1INSTALLEDJ15+1.25 V for the input biasing of INPUT BYTE 1OMITTEDJ16For grounding the input biasing of INPUT BYTE 1OMITTEDJ17External Voltage for the threshold biasing of INPUT BYTE 2OMITTEDJ18+5 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ20For grounding the threshold network of INPUT BYTE 2OMITTEDJ21External Voltage for the input biasing of INPUT BYTE 2OMITTEDJ22For grounding the threshold network of INPUT BYTE 2OMITTEDJ23+1.25 V for the input biasing of INPUT BYTE 2OMITTEDJ24For grounding the input biasing of INPUT BYTE 2OMITTEDJ24For grounding the input biasing network of INPUT BYTE 2OMITTEDJ24For grounding the input biasing network of INPUT BYTE 2OMITTEDJ24For grounding the input biasing network of INPUT BYTE 2OMITTED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30  |                                                             | OWITTED       |

| J10+5 V for the threshold biasing of INPUT BYTE 1OMITTEDJ11+1.25 V for the threshold biasing of INPUT BYTE 1INSTALLEDJ12For grounding the threshold network of INPUT BYTE 1OMITTEDJ13External Voltage for the input biasing of INPUT BYTE 1OMITTEDJ14+5 V for the input biasing of INPUT BYTE 1INSTALLEDJ15+1.25 V for the input biasing of INPUT BYTE 1OMITTEDJ16For grounding the input biasing of INPUT BYTE 1OMITTEDJ17External Voltage for the threshold biasing of INPUT BYTE 2OMITTEDJ18+5 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ20For grounding the threshold network of INPUT BYTE 2OMITTEDJ21External Voltage for the input biasing of INPUT BYTE 2OMITTEDJ22For grounding the threshold network of INPUT BYTE 2OMITTEDJ23+1.25 V for the input biasing of INPUT BYTE 2OMITTEDJ24For grounding the input biasing of INPUT BYTE 2OMITTEDJ24For grounding the input biasing network of INPUT BYTE 2OMITTEDJ24For grounding the input biasing network of INPUT BYTE 2OMITTEDJ24For grounding the input biasing network of INPUT BYTE 2OMITTED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |                                                             |               |

| J11+1.25 V for the threshold biasing of INPUT BYTE 1INSTALLEDJ12For grounding the threshold network of INPUT BYTE 1OMITTEDJ13External Voltage for the input biasing of INPUT BYTE 1OMITTEDJ14+5 V for the input biasing of INPUT BYTE 1INSTALLEDJ15+1.25 V for the input biasing of INPUT BYTE 1OMITTEDJ16For grounding the input biasing network of INPUT BYTE 1OMITTEDJ17External Voltage for the threshold biasing of INPUT BYTE 2OMITTEDJ18+5 V for the threshold biasing of INPUT BYTE 2OMITTEDJ19+1.25 V for the threshold biasing of INPUT BYTE 2OMITTEDJ20For grounding the threshold network of INPUT BYTE 2OMITTEDJ21External Voltage for the input biasing of INPUT BYTE 2OMITTEDJ22+5 V for the threshold network of INPUT BYTE 2OMITTEDJ23+1.25 V for the input biasing of INPUT BYTE 2OMITTEDJ24For grounding the input biasing of INPUT BYTE 2OMITTEDJ24For grounding the input biasing network of INPUT BYTE 2OMITTEDJ24For grounding the input biasing network of INPUT BYTE 2OMITTED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | J9  | External Voltage for the threshold biasing of INPUT BYTE 1  | OMITTED       |