## VMIVME-2534

## 32-BIT HIGH VOLTAGE DIGITAL INPUT OR OUTPUT BOARD WITH P2 I/O AND BUILT-IN-TEST

#### INSTRUCTION MANUAL

DOCUMENT NO. 500-002534-000 K

Revised July 22, 1994

VME MICROSYSTEMS INTERNATIONAL CORPORATION 12090 SOUTH MEMORIAL PARKWAY HUNTSVILLE, ALABAMA 35803-3308 (205) 880-0444 1-800-322-3616

#### NOTICE

The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

BITMODULETM, MEGAMODULETM, TURBOMODULETM, AMXbustm, SRTbustm, DMAbustm, VMEnettm, VMEnettltm, NETbustm, TESTCALtm, UCLIOTM, UIODTM, UIOCTM, and VMEmanagertm are trademarks of VME Microsystems International Corporation. The VMIC logo is a registered trademark of VME Microsystems International Corporation. Other registered trademarks are the property of their respective owners.

#### VME Microsystems International Corporation

All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless granted express written permission from VMIC.

Copyright © October 1988 by VME Microsystems International Corporation

| REVISION<br>LETTER | DATE     | PAGES INVOLVED                                                                                                                               | CHANGE NUMBER |

|--------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Α                  | 08/31/89 | Release ZZZ Manual                                                                                                                           | 89-0105       |

| В                  | 11/02/89 | Cover, pages ii, 2-9, and Appendix A                                                                                                         | 89-0148       |

| С                  | 01/17/90 | Cover, page ii, and Appendix A                                                                                                               | 89-0174       |

| D                  | 01/17/90 | Cover, page ii, and Appendix A                                                                                                               | 89-0197       |

| Е                  | 01/17/90 | Cover, pages ii, 1-1, 2-7, 2-9, 3-10, 5-1, 5-2, and 5-10                                                                                     | 90-0003       |

| F                  | 05/08/90 | Cover, page ii, and Appendix A                                                                                                               | 90-0060       |

| G                  | 05/08/90 | Cover, page ii, and Appendix A                                                                                                               | 90-0061       |

| Н                  | 01/14/91 | Cover, page ii, and Appendix A                                                                                                               | 90-0203       |

| J                  | 04/22/92 | Cover, page ii, Section 2, Section 6, and Appendix A                                                                                         | 92-0104       |

| К                  | 07/22/94 | Cover, Notice, page ii, Table of<br>Contents, pages 1-2, 3-1, 3-5, 3-8, 3-10,<br>4-1, 4-2, 5-1, 5-2, 5-6, 5-21, 5-23, 5-25,<br>and Section 6 | 94-0713       |

|                    |          |                                                                                                                                              |               |

|                    |          |                                                                                                                                              |               |

|                    |          |                                                                                                                                              |               |

|                    |          |                                                                                                                                              |               |

VME MICROSYSTEMS INT'L CORP.

PAGE NO.

12090 South Memorial Parkway • Huntsville, AL 35803-3308• (205) 880-0444

DOC. NO. 500-002534-000

K

II

#### VMIC SAFETY SUMMARY

THE FOLLOWING GENERAL SAFETY PRECAUTIONS MUST BE OBSERVED DURING ALL PHASES OF THIS OPERATION, SERVICE, AND REPAIR OF THIS PRODUCT. FAILURE TO COMPLY WITH THESE PRECAUTIONS OR WITH SPECIFIC WARNINGS ELSEWHERE IN THIS MANUAL VIOLATES SAFETY STANDARDS OF DESIGN, MANUFACTURE, AND INTENDED USE OF THE PRODUCT. VME MICROSYSTEMS INTERNATIONAL CORPORATION ASSUMES NO LIABILITY FOR THE CUSTOMER'S FAILURE TO COMPLY WITH THESE REQUIREMENTS.

#### GROUND THE SYSTEM

To minimize shock hazard, the chassis and system cabinet must be connected to an electrical ground. A three-conductor AC power cable should be used. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet.

DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE

Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.

KEEP AWAY FROM LIVE CIRCUITS

Operating personnel must not remove product covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

DO NOT SERVICE OR ADJUST ALONE

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

DO NOT SUBSTITUTE PARTS OR MODIFY SYSTEM

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to VME Microsystems International Corporation for service and repair to ensure that safety features are maintained.

DANGEROUS PROCEDURE WARNINGS

Warnings, such as the example below, precede only potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

WARNING

DANGEROUS VOLTAGES, CAPABLE OF CAUSING DEATH, ARE PRESENT IN THIS SYSTEM. USE EXTREME CAUTION WHEN HANDLING, TESTING, AND ADJUSTING.

### SAFETY SYMBOLS

## GENERAL DEFINITIONS OF SAFETY SYMBOLS USED IN THIS MANUAL

Instruction manual symbol: the product is marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect against damage to the system.

Indicates dangerous voltage (terminals fed from the interior by voltage exceeding 1000 volts are so marked).

Protective conductor terminal. For protection against electrical shock in case of a fault. Used with field wiring terminals to indicate the terminal which must be connected to ground before operating equipment.

Low-noise or noiseless, clean ground (earth) terminal. Used for a signal common, as well as providing protection against electrical shock in case of a fault. Before operating the equipment, terminal marked with this symbol must be connected to ground in the manner described in the installation (operation) manual.

Frame or chassis terminal. A connection to the frame (chassis) of the equipment which normally includes all exposed metal structures.

Alternating current (power line).

Direct current (power line).

Alternating or direct current (power line).

WARNING

The WARNING sign denotes a hazard. It calls attention to a procedure, a practice, a condition, or the like, which, if not correctly performed or adhered to, could result in injury or death to personnel.

The CAUTION sign denotes a hazard. It calls attention to an operating a procedure, a practice, a condition, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the system.

NOTE:

The NOTE sign denotes important information. It calls attention to a procedure, a practice, a condition or the like, which is essential to highlight.

## VMIVME-2534

## 32-BIT HIGH VOLTAGE DIGITAL INPUT OR OUTPUT BOARD WITH P2 I/O AND BUILT-IN-TEST

## **TABLE OF CONTENTS**

| SEC | CTION 1. | INTRODUCTION                            | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|----------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 | FEATU    | JRES                                    | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | FUNCT    | TIONAL DESCRIPTION                      | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.3 | PEEEE    | TIONAL BLOCK DIAGRAM                    | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.4 | HEFER    | RENCE MATERIAL LIST                     | 1-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SEC | TION 2.  | PHYSICAL DESCRIPTION AND SPECIFICATIONS | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SEC | TION 3.  | THEORY OF OPERATION                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.1 | INTRO    | DUCTION                                 | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2 | OPERA    | TIONAL OVERVIEW                         | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3 | VMEbu    | s FOUNDATION LOGIC                      | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.4 | DEVICE   | E ADDRESSING                            | 3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5 | CONTR    | ROL STATUS REGISTER (CSR)               | 3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.6 | OUTPU    | /T DATA PATH                            | 3-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.7 | INPUT    | DATA PATH                               | 3-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.8 | BUILT-I  | IN-FUNCTIONS DESCRIPTION                | 3-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SEC | TION 4.  | PROGRAMMING                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.1 | INTRO    | DUCTION                                 | 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.2 | DATA T   | RANSFERS                                | 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.3 | CONTR    | OL STATUS REGISTER (CSR)                | 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SEC | TION 5.  | CONFIGURATION AND INSTALLATION          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.1 | UNPAC    | KING PROCEDURES                         | 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.2 | PHYSIC   | CAL INSTALLATION                        | 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |          |                                         | TOUR SECRETARION OF THE PARTY O |

## **TABLE OF CONTENTS (Continued)**

## SECTION 5. CONFIGURATION AND INSTALLATION (Concluded)

|                                                                                                                                             | E                                   | age                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------|

| 5.2.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                                                           | Installation                        | 5-6<br>5-6<br>5-9<br>5-10                                             |

| SECTION                                                                                                                                     | ON 6. MAINTENANCE AND WARRANTY      |                                                                       |

| 6.1 I<br>6.2 I                                                                                                                              | MAINTENANCE6<br>MAINTENANCE PRINTS6 | 6-1<br>6-1                                                            |

|                                                                                                                                             | LIST OF FIGURES                     |                                                                       |

| <u>Figure</u>                                                                                                                               | Pa                                  | <u>ige</u>                                                            |

| 1.2-1<br>1.2-2<br>1.3-1<br>3.2-1<br>3.3-1<br>3.3-2<br>3.4-1<br>3.5-1<br>5.2.1-1<br>5.2.1-2<br>5.3.1-1<br>5.3.1-2<br>5.4-1<br>5.5-1<br>5.5-2 | Basic Digital I/O Board Functions   | -4<br>-5<br>-2<br>-3<br>-4<br>-6<br>-7<br>-9<br>-2<br>-5<br>-9<br>-11 |

|                                                                                                                                             | Pos True5-                          | -13                                                                   |

## TABLE OF CONTENTS (Continued)

## LIST OF FIGURES (Concluded)

| <u>Figure</u>                                                       |                                                                                                                                                                                          | Page                                  |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 5.5-4                                                               | Jumper Configuration and Typical Input Circuit for Contact Closure,<br>Neg True                                                                                                          | 5-14                                  |

| 5.5-5                                                               | Jumper Configuration and Typical Input Circuit for Voltage Sourcing, Pos True                                                                                                            | 5-15                                  |

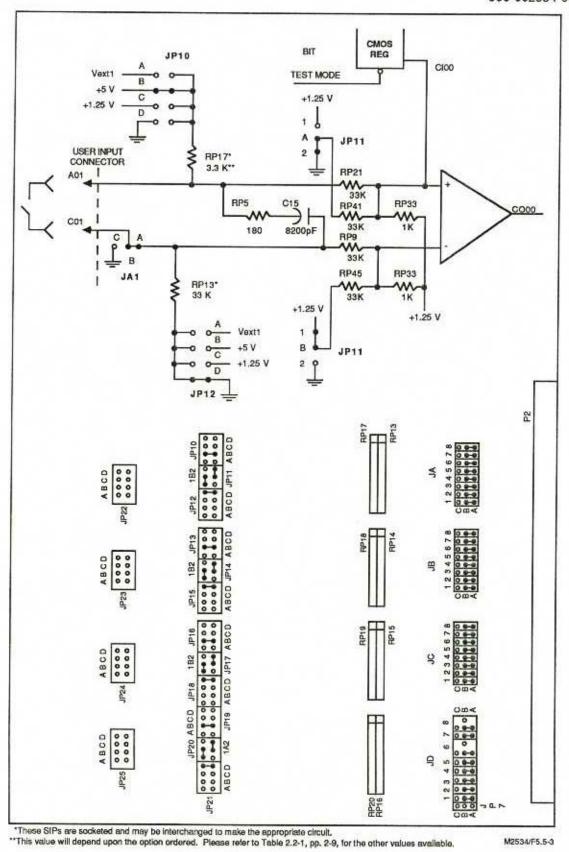

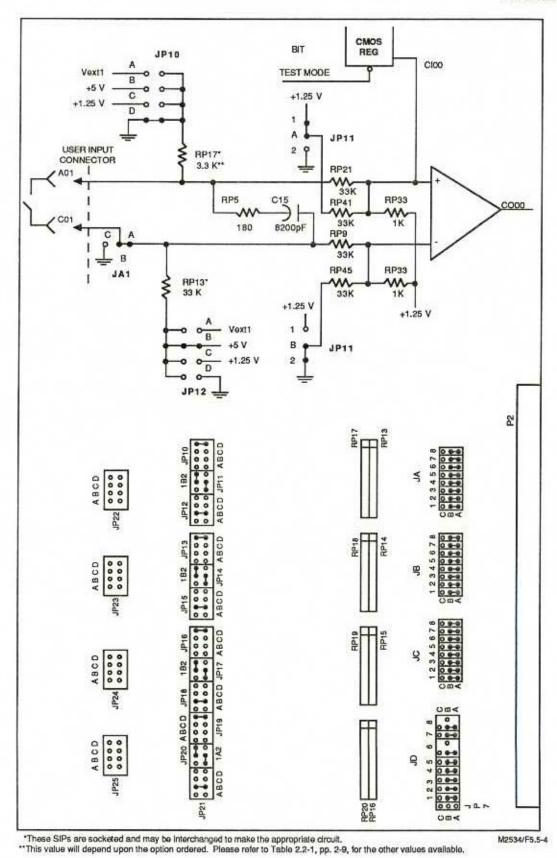

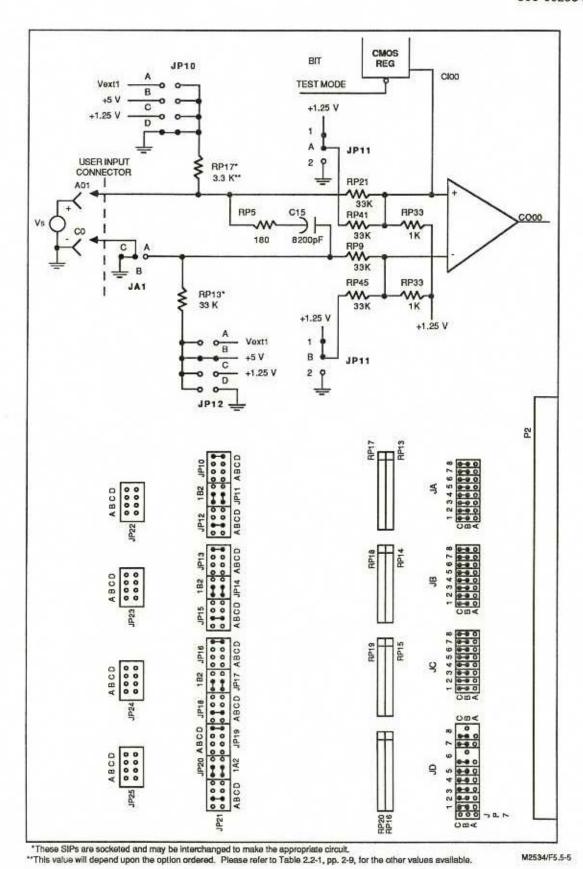

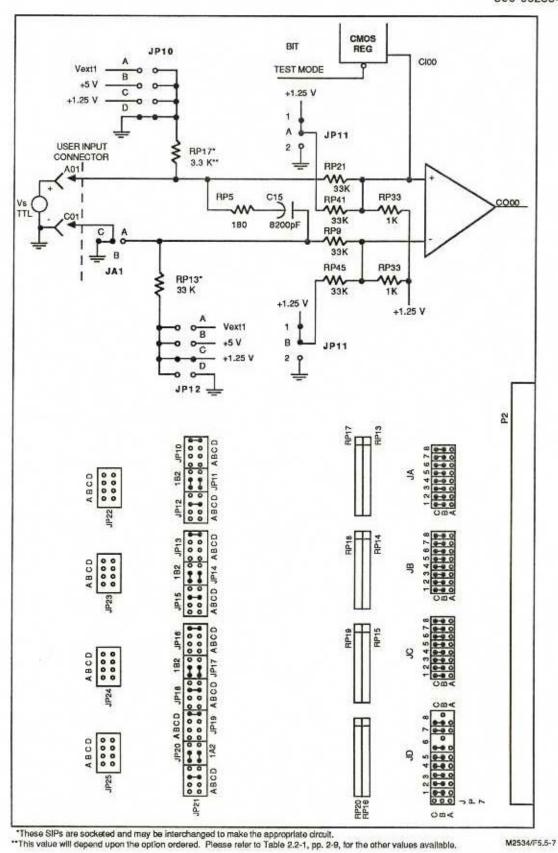

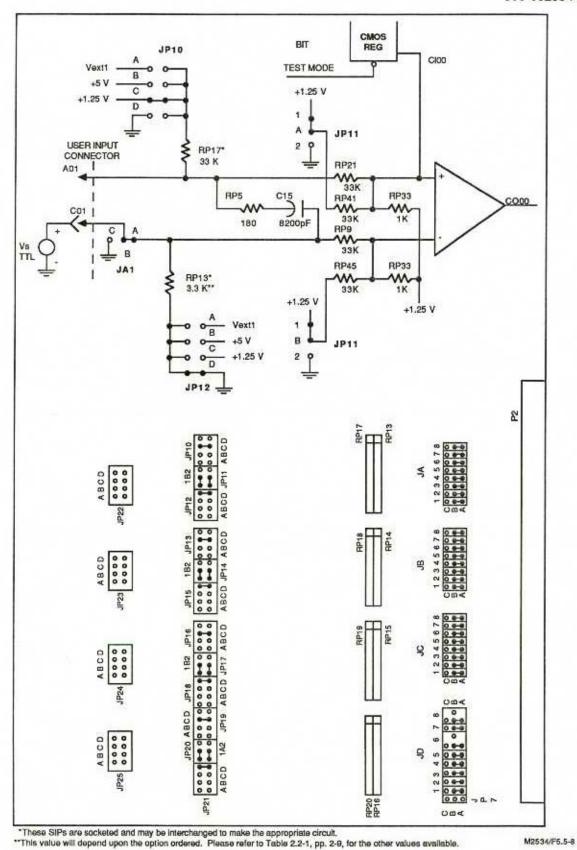

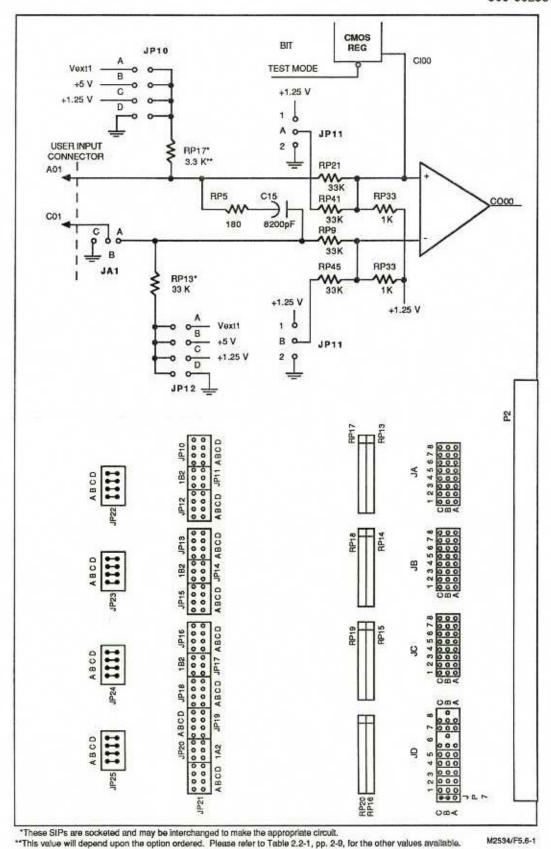

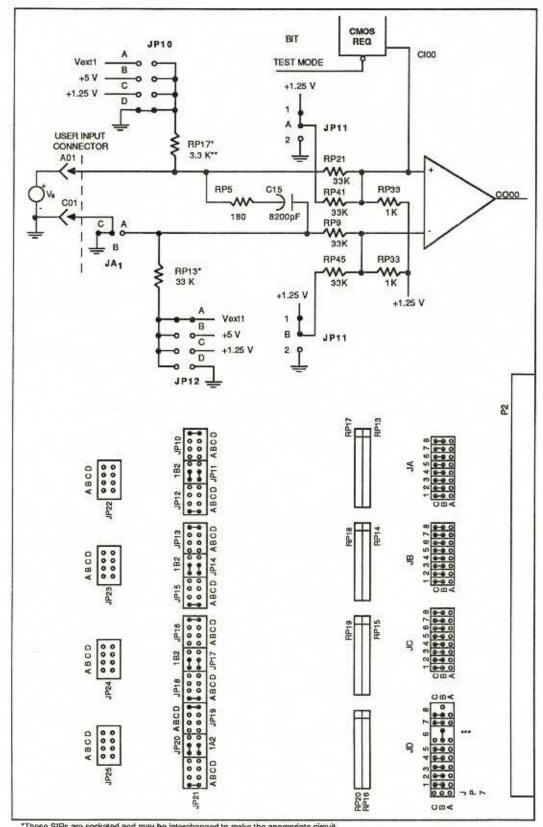

| 5.5-6                                                               | Jumper Configuration and Typical Input Circuit for Voltage Sourcing, Neg True                                                                                                            | 5-16                                  |

| 5.5-7                                                               | Jumper Configuration and Typical Input Circuit for Voltage Sourcing,                                                                                                                     | 5-10                                  |

| 5.5-8                                                               | Jumper Configuration and Typical Input Circuit for Voltage Sourcing                                                                                                                      |                                       |

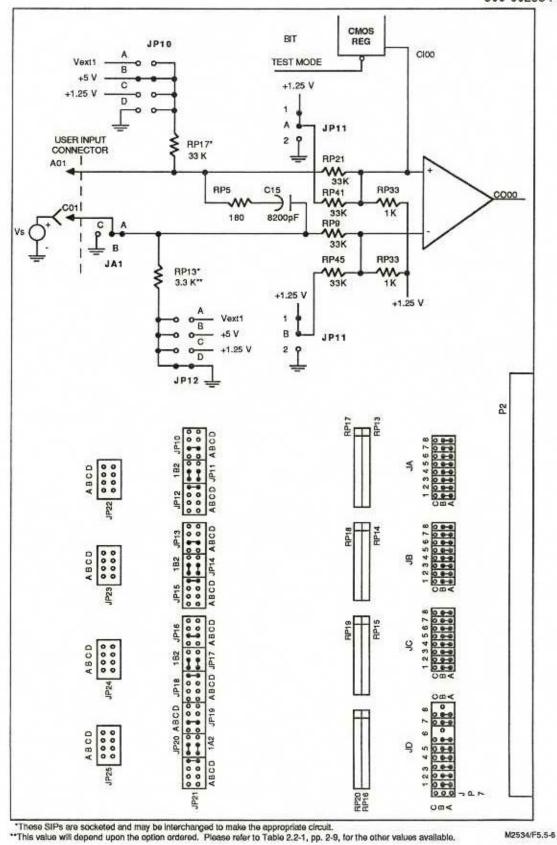

| 5.6-1<br>5.6-2                                                      | Jumper Configuration for On Board +5 V Diode Clamp Voltage  Jumper Configuration for Voltage Sourcing Pos True Using External Voltage                                                    |                                       |

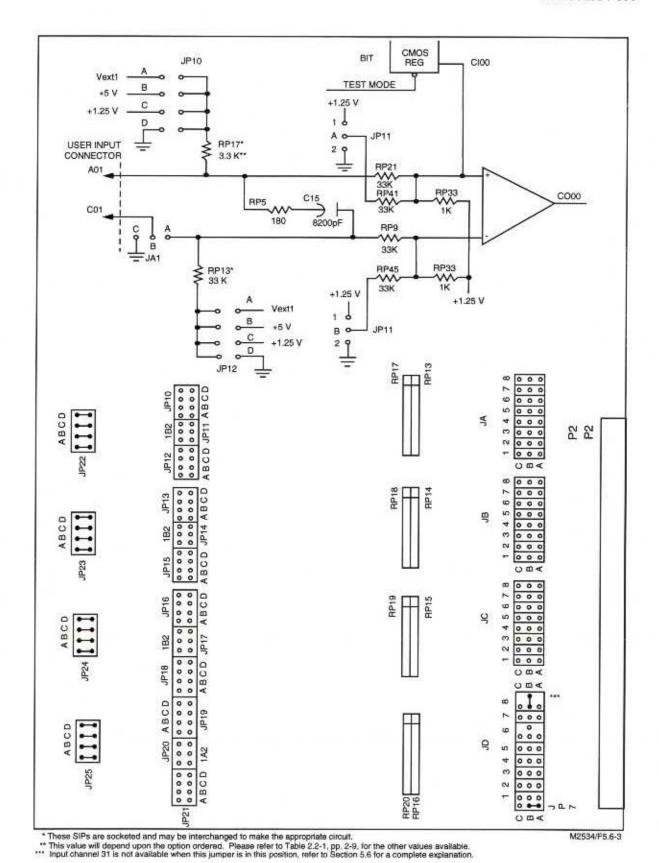

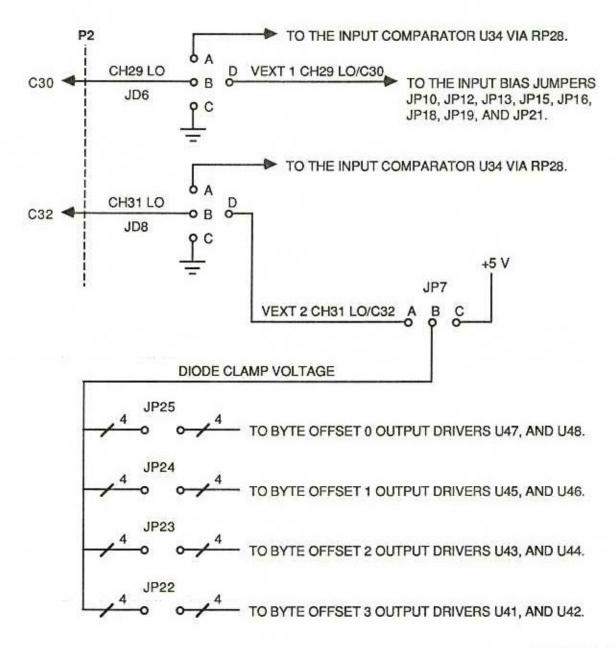

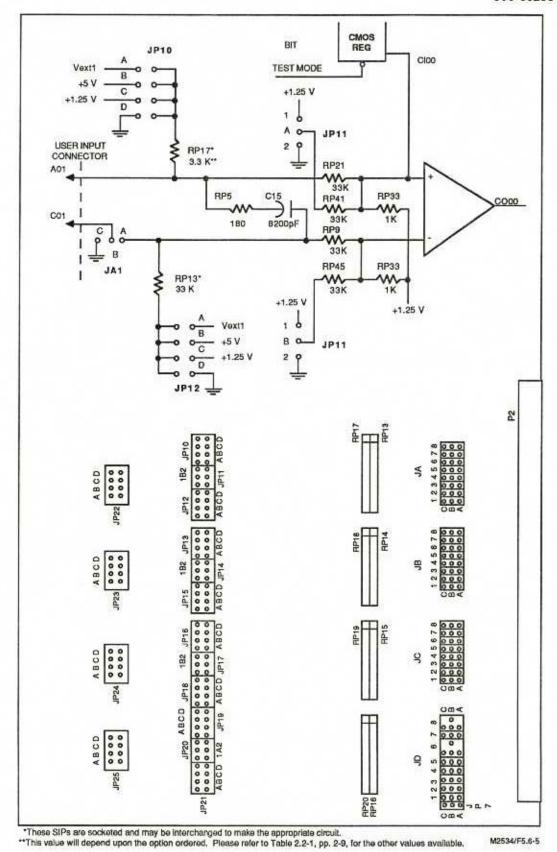

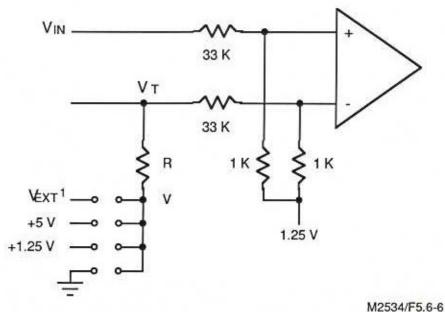

| 5.6-3<br>5.6-4<br>5.6-5<br>5.6-6                                    | Jumper Configuration for External Diode Clamp Voltage External Voltage Jumper Definitions Jumper Configuration and Typical Input Circuit Chosen Threshold Voltage Diagram                | .5-21<br>.5-22<br>5-24                |

|                                                                     | LIST OF TABLES                                                                                                                                                                           |                                       |

| <u>Table</u>                                                        | <u>P</u>                                                                                                                                                                                 | age                                   |

| 4.3-1<br>5.2.1-1<br>5.2.1-2<br>5.2.2-1<br>5.2.2-2<br>5.6-1<br>5.6-2 | Input Circuit Configuration  Pullup/Pulldown Resistor Installation Sheet  Threshold Voltages for R = 3.3 k Ohms  Threshold Voltages for R = 33 k Ohms                                    | .5-3<br>.5-4<br>.5-7<br>.5-8<br>.5-26 |

| 5.6-3<br>5.6-4<br>5.6-5<br>5.6-6<br>5.6-7                           | Threshold Voltages for R = 270 Ohms Threshold Voltages for R = 560 Ohms Threshold Voltages for R = 1.5 k Ohms Threshold Voltages for R = 6.8 k Ohms Threshold Voltages for R = 27 k Ohms | 5-27<br>5-27<br>5-27                  |

#### **APPENDIX**

A Assembly Drawing, Parts List, and Schematic

## TABLE OF CONTENTS (Concluded)

#### LIST OF TABLES (Concluded)

| <u>Table</u> |                                             | Page |

|--------------|---------------------------------------------|------|

| 5.2.2-2      | Pullup/Pulldown Resistor Installation Sheet | 5-8  |

| 5.6-1        | Threshold Voltages for R = 3.3 k Ohms       | 5-26 |

| 5.6-2        | Threshold Voltages for R = 33 k Ohms        | 5-26 |

|              | Threshold Voltages for R = 270 Ohms         |      |

| 5.6-4        | Threshold Voltages for R = 560 Ohms         |      |

| 5.6-5        | Threshold Voltages for R = 1.5 k Ohms       |      |

| 5.6-6        | Threshold Voltages for R = 6.8 k Ohms       | 5-27 |

| 5.6-7        | Threshold Voltages for R = 27 k Ohms        |      |

#### **APPENDIX**

A Assembly Drawing, Parts List, and Schematic

#### SECTION 1

#### INTRODUCTION

#### 1.1 FEATURES

The VMIVME-2534 is a VMEbus Compatible High Voltage Digital I/O Board with 32 channels of high voltage digital outputs and 32 channels of high voltage or differential digital inputs. Its features include:

- a. Thirty-two High Voltage Outputs

- (1) High sink current (600 mA)

(2) High breakdown voltage (70 V)

(3) Output voltage range options (TTL compatible, 5 V, 12 V, 24 V, and 48 V)

(4) Output clamp diodes

(5) Outputs in the same chip may be paralleled for higher drive capability

(6) 8-, 16-, or 32-bit data transfers

(7) Uses the UDN-2549B incandescent lamp driver (no external warming resistors required)

#### b. Thirty-two High Voltage/Differential Inputs

Each group of eight inputs are jumper selectable to monitor contact closure, voltage sourcing, current sinking, or differential signals.

(2) Open circuit provides a logic "zero" or (jumper selectable) a logic "one".

(3) Input filter option or RS422/RS485 compatible terminator option

(4) User selectable input voltage thresholds (1.25 V to 66 V)

#### c. Common Board Features

(1) P2 I/O connection (no front panel connectors)

(2) Built-in-Test (off-line and real-time support)

(3) 100% testing of all active components (including the output drivers)

(4) Front panel with Fail LED

(5) Compatible with Intelligent I/O Controllers

(6) Software compatible with the VMIVME-2532

#### 1.2 FUNCTIONAL DESCRIPTION

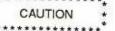

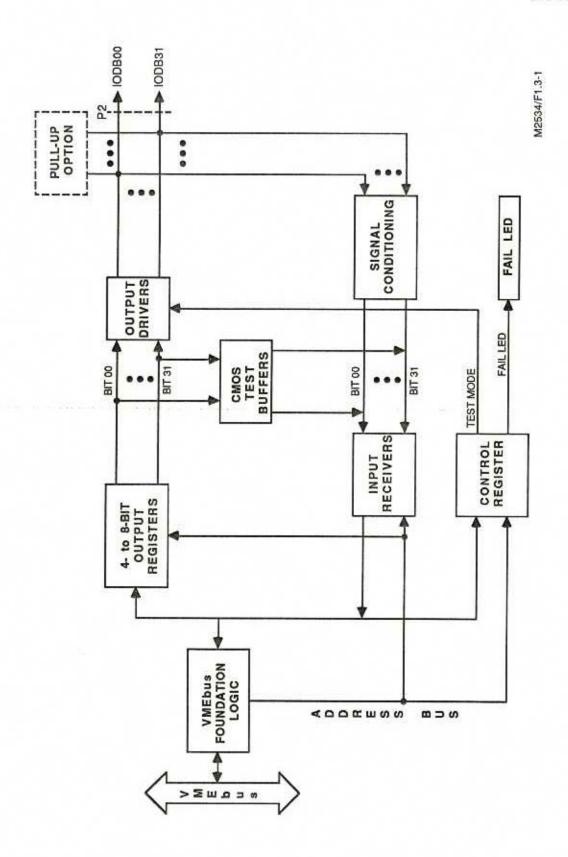

The 32-bit Digital Input/Output (DIO) board transfers digital data from the VMEbus backplane to output registers that are interfaced to high voltage output drivers. It also reads high voltage or differential input signals and puts the data on the VMEbus backplane for subsequent transfer to a CPU. A simplified functional block diagram of a 32-bit DIO board is illustrated in Figure 1.2-1.

This high voltage DIO board is designed with a variety of manufacturing options to allow the user to specify the board's input and output configurations. The input signal conditioning circuitry supports a wide variety of topologies. These topologies include differential, single-ended active-high data, single-ended active-low data, and filtered (or debounced) inputs. The single-ended inputs can be configured for contact sensing, voltage sourcing, or current sinking with selectable input threshold voltages on a byte-by-byte basis. These topologies are user configurable. The output configuration is basically open collector, but the input topology permits an input resistor to be used as a pull-up for the output drivers.

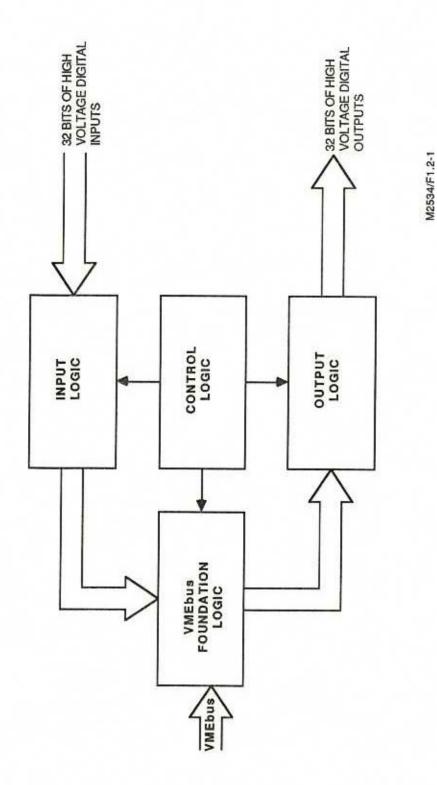

The VMIVME-2534 is designed with extensive Built-in-Test electronics that enable the user to test the functioning of the board. Test registers are provided for off-line testing of the board. This test tristates the output drivers to prevent damage to the field circuity. The board's outputs are tied to the input signal conditioning circuits, and by reading the input circuits the outputs can be tested. Thus 100% of the board's I/O circuitry can be tested this way. Figure 1.2-2 is a functional block diagram showing the Built-in-Test features of the VMIVME-2534 board.

#### 1.3 FUNCTIONAL BLOCK DIAGRAM

The VMIVME-2534 DIO board consists of VMEbus compatibility logic, four 8-bit output registers, four 8-bit input ports, a Control Status Register (CSR), and Built-in-Test logic, as shown in Figure 1.3-1. The VMEbus compatibility logic controls data transfers allowing 8-, 16-, or 32-bit VMEbus data transfers. Four 8-bit output registers latch 32-bits of output data, which drive the high voltage output drivers. Four 8-bit input receivers monitor the user field circuitry (and the output drivers if they are being used). The CSR controls the on-board Fail LED, the test functions, and the state of the I/O circuits of the board. The Built-in-Test logic enables the output data to be read back through the input ports without affecting incoming signals from the field. System reset or power-up puts the board in test mode for immediate loopback testing.

Figure 1.2-1. Basic Digital I/O Board Functions

Figure 1.2-2. Simplified Built-in-Test Functional Block Diagram

Figure 1.3-1. Functional Block Diagram

#### 1.4 REFERENCE MATERIAL LIST

The reader should refer to "The VMEbus Specification" for a detailed explanation of the VMEbus. "The VMEbus Specification" is available from the following source:

# VITA VMEbus International Trade Association 10229 N. Scottsdale Road Scottsdale, AZ 85253 (602) 951-8866

The following applications and configuration guides are available from VMIC to assist the user in the selection, specification, and implementation of systems based on VMIC's products.

| TITLE                                                     | DOCUMENT NO.   |

|-----------------------------------------------------------|----------------|

| Digital Input Board Application Guide                     | 825-000000-000 |

| Change-of-State Application Guide                         | 825-000000-002 |

| Connector and I/O Cable Application Guide                 | 825-000000-006 |

| Digital I/O (with Built-in-Test) Product Line Description | 825-000000-003 |

## SECTION 2 PHYSICAL DESCRIPTION AND SPECIFICATIONS

REFER TO 800-002534-000 SPECIFICATION

#### SECTION 3

#### THEORY OF OPERATION

#### 3.1 INTRODUCTION

This section of the manual presents information concerning the hardware operation of the board. The reader should refer to VMIC Document Number 825-00000-000 (Digital Input Board Application Guide) for a thorough understanding of the voltage sourcing and current sinking concepts.

#### 3.2 OPERATIONAL OVERVIEW

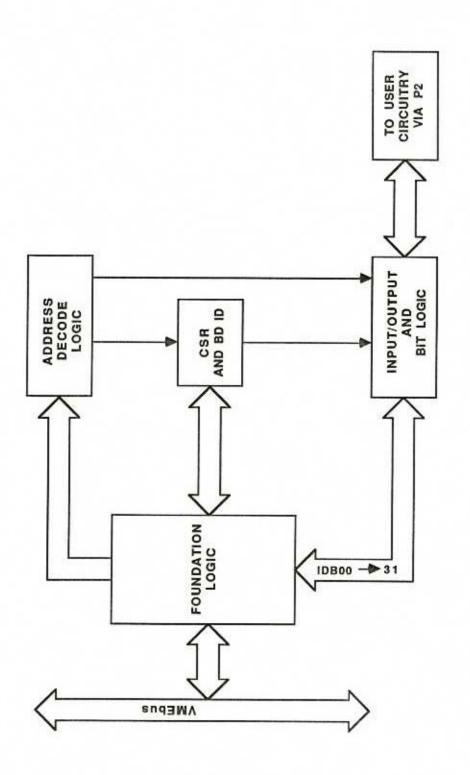

The VMIVME-2534 consists of four primary blocks as illustrated in Figure 3.2-1. These blocks will be described in detail in the following sections. To perform an output data transfer, data is written into the Output Data Registers (ODR) from the VMEbus and controls the output driver stage of the board. The input ports monitor the P2 connector and hence the output drivers. When the drivers are *NOT* enabled (tristated) or they are removed from the board (they are socketed), the inputs can monitor the field circuitry and input transfers can be performed via the Input Data Registers (IDR). If the output drivers *ARE* enabled, the inputs can monitor their state. In this way the inputs perform the real-time Built-in-Test function.

#### 3.3 VMEbus FOUNDATION LOGIC

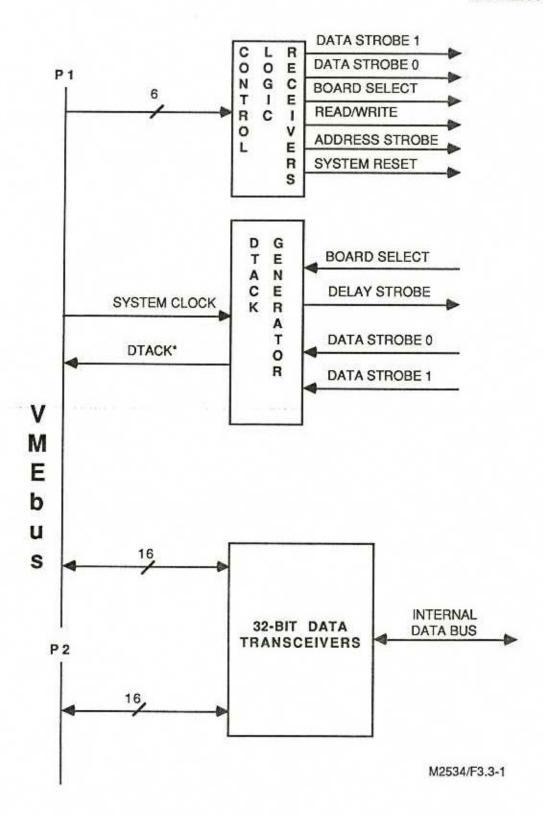

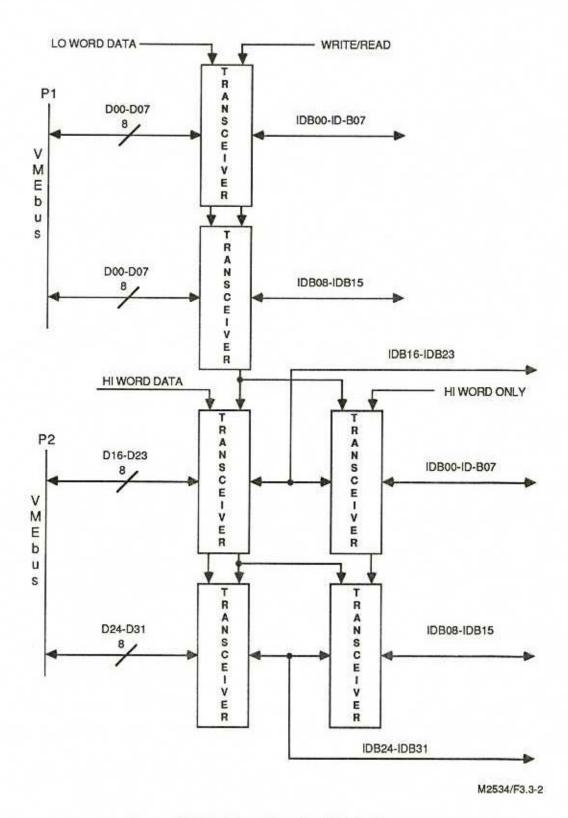

The basic VMEbus foundation logic used by the VMIVME-2534 is illustrated in Figure 3.3-1. It consists of control signal receivers, a DTACK generator, and the 32-bit data bus transceivers. The buffer drivers and receivers or transceivers, are used to present minimum VMEbus loading and board logic buffering. The DTACK generator is designed to provide the maximum data transfer rate for this board. The VMIVME-2534 can perform 8-, 16-, or 32-bit data transfers. Figure 3.3-2 shows the data transceivers and the topology used in processing the data transfers. The detailed logic diagram (Document Number 141-002534-000) used in this design can be found in Appendix A to this manual.

M2534/F3.2-1

Figure 3.2-1. Functional Block Diagram

Figure 3.3-1. VMEbus Foundation Logic

Figure 3.3-2. Data Transfer Block Diagram

#### 3.4 DEVICE ADDRESSING

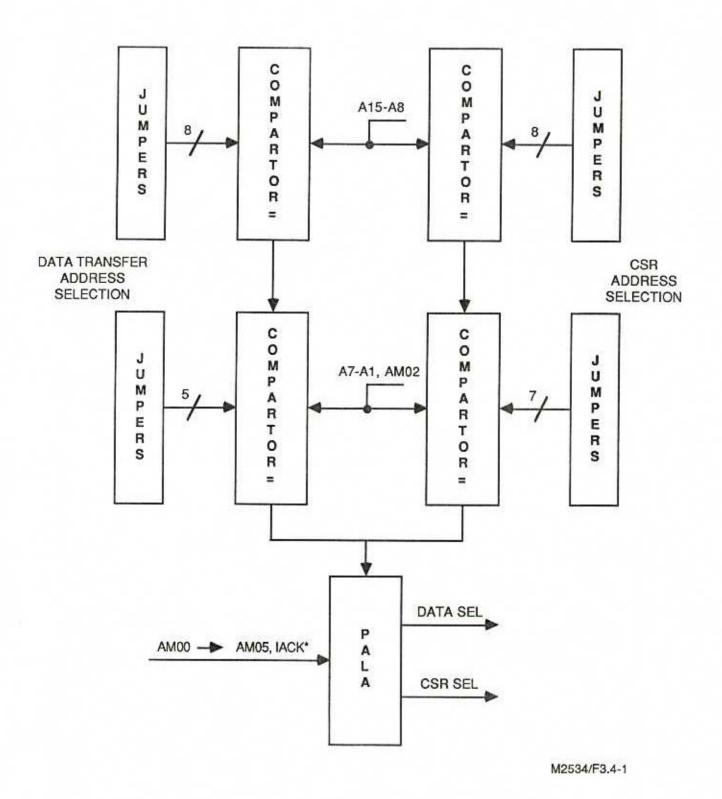

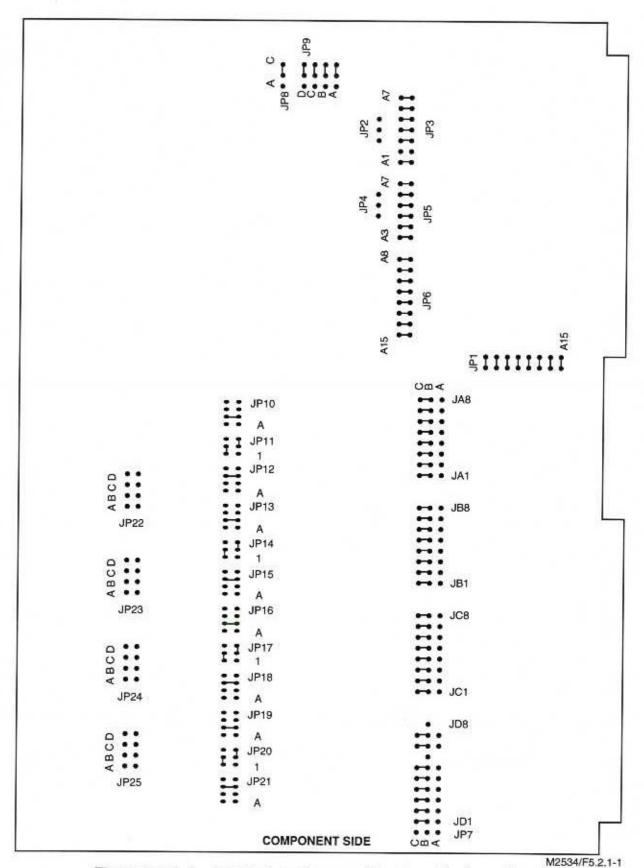

The address decoding scheme used in this design is shown in Figure 3.4-1. The data registers are decoded separately from the Control Status Register (CSR). This allows the CSRs and data registers of several boards to be mapped into separate, but contiguous, memory addresses. This can help make software more efficient. The board is shipped with the CSR stacked on top of the data registers. This makes it software compatible with the VMIVME-2532 for the shipped address. The user will have to adjust all of the address headers when he sets up this board.

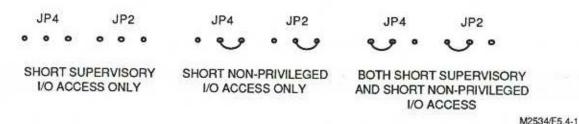

The board is designed to support data transfers in the short I/O memory space. A pair of jumpers (labeled AM2) are used to establish the I/O space to be used. One is used for the data registers and the other is used with the CSR. These jumpers permit the user to select between supervisory, non-privileged or both I/O accesses for the data, or CSR registers. The board is factory configured (jumpers AM2 not installed) to respond to supervisory I/O accesses.

#### 3.5 CONTROL STATUS REGISTER (CSR)

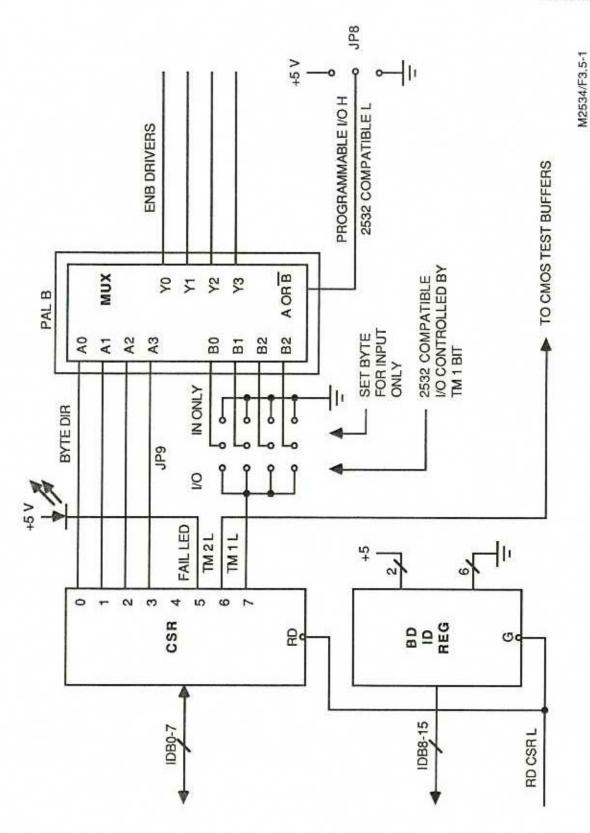

The Control Status Register (CSR) in the VMIVME-2534 is a read/write register that controls the test mode bits, a Fail LED, the output drivers, and includes a read only board Identification Register (IDR). The CSR and the board IDR are read as a 16-bit word with the IDR in the upper (MSB) byte as shown in Figure 3.5-1. The test mode and the LED bits are in the same BIT positions as the VMIVME-2532. This is to keep these two boards software compatible. These three bits perform the same VMIVME-2532 functions in the 2534; however, test mode bit 1 (TM 1 L) can be programmed (by jumpers J8 and J9) to permit software control of the I/O direction on a byte-by-byte basis. Test mode bit 2 (TM 2 L) is used to enable the CMOS test buffers, which are used during diagnostic testing.

Jumpers JP8 and JP9 are used in conjunction with CSR bits to control the output drivers. The two modes are VMIVME-2532 simulation and VMIVME-2534 mode. JP8 sets the mode to VMIVME-2532 simulation in position B-C. The VMIVME-2532 simulation mode allows the inputs to be configured a byte at a time as input only mode (JP9 in position 2) or I/O control using TM1 bit in the CSR (JP9 in position 1). Installing JP8 in position A-B will set the mode to VMIVME-2534, where the direction is controlled a byte at a time via TM1 and B0H-B3H. Program TM1 to a logic 1 to enable the output drivers. The byte of channels can be programmed using B0H (CH.24-CH.31), B1H (CH.16-CH.23), B2H (CH.8-CH.15), and B3H (CH.0-CH.7), where a logic 1 enables the byte as an output.

A front panel Fail LED is provided by the VMIVME-2534. This Fail LED is illuminated upon power-up or after a system reset. It may be extinguished under

Figure 3.4-1. Device Address Selection Block Diagram

Figure 3.5-1. CSR and Board Input Data Registers

software control after successfully completing some diagnostic software. It can be turned on if the board fails to respond to commands it should. This can be useful in locating faulty boards in a system.

A board IDR is also provided by the VMIVME-2534. This IDR is part of the CSR word. Its value is 05 HEX for positive true output option. The value is FA HEX for negative true output option. This is a *read only* register. It can be used by system start-up software to automatically set up the system configuration, thus, eliminating possible human error.

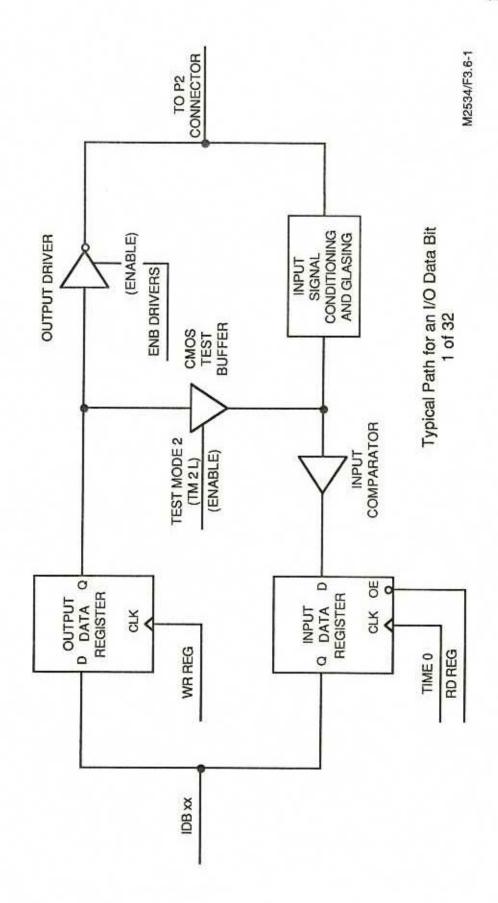

#### 3.6 OUTPUT DATA PATH

The typical path for a bit of I/O data is shown in Figure 3.6-1. The output path consists of an output data register which controls the associated output driver, and, therefore, the user's field circuitry via the P2 connector. In the on-line (normal) mode of operation, a write instruction moves data from the VMEbus via the board's internal data bus to the Output Data Registers (ODRs) and hence to the output drivers. These drivers are open collector devices, thus, the output data gets inverted (a logic "one" turns ON the driver and a logic "zero" is sent to the user's field circuitry). The data registers control this data polarity. If a non-inverting register is used (as in the positive true option) then a logic "one" written to the board issues a logic "zero" to the field circuitry. However, if an inverting latch is used (as in the negative true option) then a logic "one" written to the board turns OFF the driver and the output will go to the state dictated by the passive components in the output circuitry of the board.

#### 3.7 INPUT DATA PATH

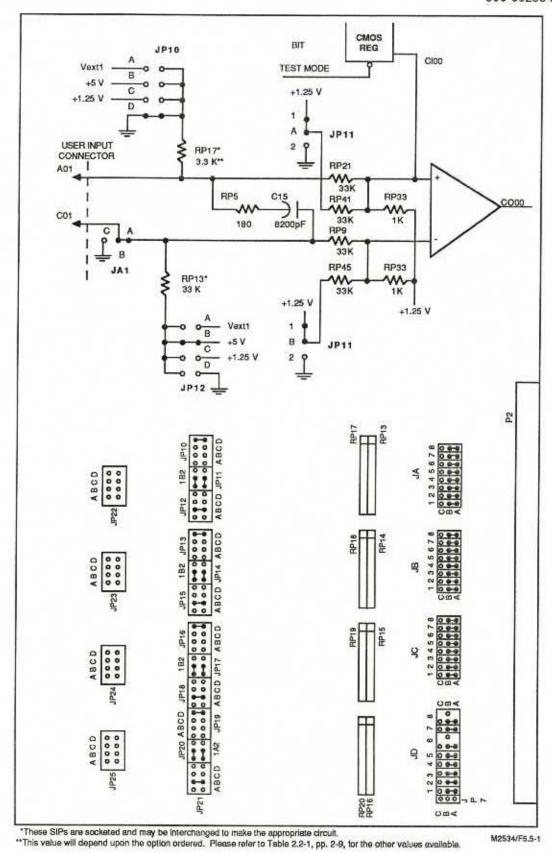

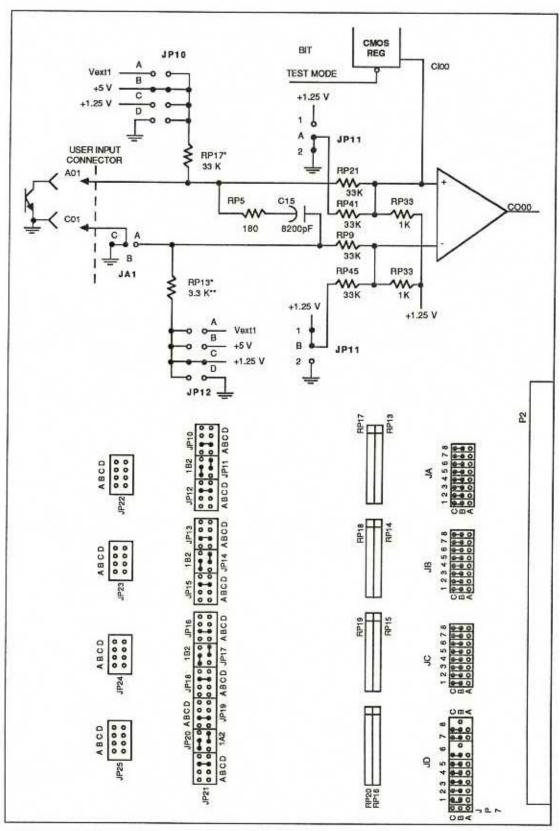

The input data path flows from the user's field electronics (via the P2 connector) through the input signal conditioning circuit (consisting of resistor networks for the input and comparator biasing) to the input voltage comparator to the Input Data Register (IDR), and finally the VMEbus via the board's internal data bus. If the output drivers are not enabled (tristated) and a *read* operation is performed, the input data from the voltage comparator is latched in the IDR. From there the data moves through the internal data bus to the VMEbus. The output drivers are socketed and can be removed by the user if their leakage current is to much for the input circuitry.

The input circuitry can be arranged to perform many types of signal conditioning. Voltage sourcing, current sensing, contact closure sensing, differential, positive true or negative true inputs are all supported by various circuit configurations. These set ups may be configured by the user on a byte-by-byte basis. Thus, one byte may be fixed to read voltage sourcing inputs with positive true data, while another byte is set up to read differential inputs, and yet another byte is configured to process contact closures with negative true data. These

Figure 3.6-1. Digital Input/Output and BIT Block Diagram

configurations are done by jumper selections and the position of input resistor SIP networks. Different voltage levels are handled by different values for the input SIP resistors. The specific SIP and jumper configurations for specific input requirements are discussed in Section 5 of this manual. However, it must be remembered that the outputs must be tristated or removed for these inputs to read the user's external inputs.

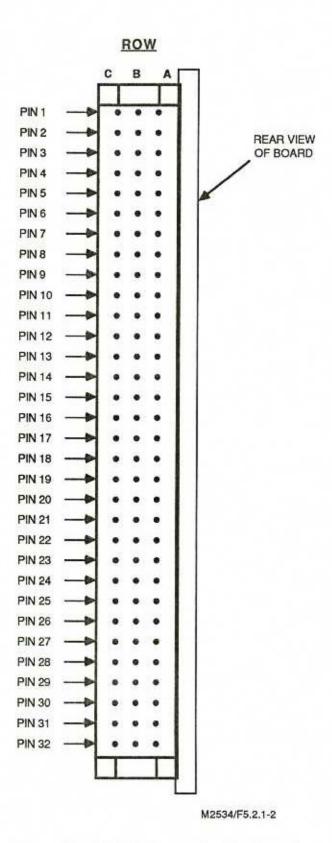

#### 3.8 BUILT-IN-FUNCTIONS DESCRIPTION