# VMIVME-2540 Intelligent Counter/Controller

**Product Manual**

12090 South Memorial Parkway Huntsville, Alabama 35803-3308, USA (256) 880-0444 • (800) 322-3616 • Fax: (256) 882-0859

500-002540-000 Rev. N

A GE Fanuc Company

© Copyright 2001. The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

AMXbus, BITMODULE, COSMODULE, DMAbus, IOMax, IOWorks Foundation, IOWorks Manager, IOWorks Server, MAGICWARE, MEGAMODULE, PLC ACCELERATOR (ACCELERATION), Quick Link, RTnet, Soft Logic Link, SRTbus, TESTCAL, "The Next Generation PLC", The PLC Connection, TURBOMODULE, UCLIO, UIOD, UPLC, Visual Soft Logic Control(ler), *VMEaccess*, VMEbus Access, *VMEmanager*, *VMEmonitor*, VMEnet, VMEnet II, and *VMEprobe* are trademarks and The I/O Experts, The I/O Systems Experts, The Soft Logic Experts, and The Total Solutions Provider are service marks of VMIC.

(I/O man figure)

(IOWorks man figure)

The I/O man figure, IOWorks, IOWorks man figure, UIOC, Visual IOWorks and the VMIC logo are registered trademarks of VMIC.

ActiveX, Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, Windows NT, and XENIX are registered trademarks of Microsoft Corporation.

Celeron and MMX are trademarks, and Intel and Pentium are registered trademarks of Intel Corporation.

PICMG and CompactPCI are registered trademarks of PCI Industrial Computer Manufacturers' Group.

Other registered trademarks are the property of their respective owners.

# **Table of Contents**

| List of Figures                             |

|---------------------------------------------|

| List of Tables                              |

| Overview                                    |

| Disclaimer: Notice About Equivalent Parts   |

| Reference Material List                     |

| Physical Description and Specifications1    |

| Safety Summary                              |

| Ground the System                           |

| Do Not Operate in an Explosive Atmosphere10 |

| Keep Away from Live Circuits10              |

| Do Not Service or Adjust Alone10            |

| Do Not Substitute Parts or Modify System10  |

| Dangerous Procedure Warnings10              |

| Safety Symbols Used in This Manual1         |

| Chapter 1 - Theory of Operation             |

| Functional Description                      |

| System Timing Controller Front-End Logic19  |

| RS-422 Line Driver and Receiver19           |

| Synchronizer and Conditioning Logic         |

| AM9513A System Timing Controller            |

| QPM Direction Change Interrupt Logic23      |

| I/O Processor                               |

| 68HC000 CPU                                 |

| Decode and Control Logic                    |

| Local Bus Arbitration                       |

| Local Address Decode                                      | 26 |

|-----------------------------------------------------------|----|

| Local I/O Functions                                       | 28 |

| Local Memory                                              | 30 |

| EPROM Firmware                                            | 30 |

| Static RAM                                                | 30 |

| Local Interrupt Controller                                | 31 |

| STC Interrupts                                            | 31 |

| VMEbus Command Interrupt                                  | 31 |

| VMEbus Slave Interface                                    | 33 |

| VMEbus Slave Address Decode                               | 33 |

| Command Status Code                                       | 33 |

| VMEbus Interrupter Modules                                | 35 |

| Chanter 2. Configuration and Installation                 | 07 |

| Chapter 2 - Configuration and Installation                |    |

|                                                           |    |

|                                                           |    |

| DIP Switch Settings                                       |    |

| Jumper Options.                                           |    |

| I/O Connector Pin Assignments                             |    |

| Recommended Discrete Wire Connectors and Terminal Blocks. |    |

| TTL/Single-Ended Input Signal Compatibility Configuration | 46 |

| Chapter 3 - Programming                                   | 49 |

| VMEbus Interface Memory Map                               | 51 |

| Board ID/Configuration Buffer                             |    |

| Firmware Revision Level.                                  |    |

| Command Code                                              |    |

| Command Status Code                                       |    |

| Command Status Interrupt Request Level                    | 54 |

| Command Status Interrupt Vector.                          |    |

| Channel ID                                                | 55 |

| Continuous/Discrete Flag                                  |    |

| Measurement Ready Flag.                                   |    |

| Measurement Channel ID.                                   |    |

| Channel Measurement Status.                               | 56 |

| Channel Control Block Registers                           |    |

| Timer Channel Control Block                               |    |

| VMIVME-2540 Continuous/Discrete Flag Buffer               |    |

| VMIVME-2540 Measurement Data Valid Flags Buffer           |    |

| VMIVME-2540 Firmware Release Information.        | 58 |

|--------------------------------------------------|----|

| VMIVME-2540 Daignostic Buffer                    | 59 |

| Command Interface                                | 60 |

| Programming Using the Command Interface          | 61 |

| Command Status Codes                             | 63 |

| Modes of Operation                               | 64 |

| Input Modes of Operation.                        | 65 |

| Output Modes of Operation                        | 66 |

| Timing Modes of Operation                        | 66 |

| Channel Control Blocks Common Parameters         | 67 |

| Operation Mode Selection Flag                    | 68 |

| Format of the Operation Mode Select Flag:        | 69 |

| Operational Mode Select Flag                     | 69 |

| Command Descriptions                             | 70 |

| Initialization and Synchronization Command Codes |    |

| Channel Input/Measurement Command Codes          | 71 |

| Integer 16-bit Event Counting                    | 71 |

| Integer 32-bit Event Counting                    | 72 |

| Period Measurement                               | 74 |

| Frequency Measurement                            | 75 |

| Pulse-Width Measurement                          | 76 |

| Quadrature Position Measurement                  | 78 |

| Integer Quadrature Position Measurement          | 81 |

| 16-bit Integer Period Measurement                | 82 |

| 32-bit Integer Period Measurement                |    |

| 32-bit Integer Pulse-Width Measurement           | 85 |

| Group Acquisition Mode (Integer QPM)             | 86 |

| 16-bit Integer Pulse Measurement                 | 87 |

| Delayed Event Timer with VMEbus Interrupt        | 88 |

| Programming Strategies for Input Operations      | 89 |

| Continuous Data Acquisition Mode                 | 90 |

| Discrete Data Acquisition Mode                   | 91 |

| Channel Output/Waveform Generation Command Codes | 93 |

| 16-bit Frequency Divider                         | 93 |

| 32-bit Frequency Divider                         | 94 |

| Period/Pulse-Width Generation                    | 95 |

| Frequency/Duty Cycle Generation                  | 96 |

| Pulse Sequence Generation                        | 96 |

| Programmed Output Mode                       | 97  |

|----------------------------------------------|-----|

| Quadrature Position Control                  | 98  |

| Programming Strategies for Output Operations | 99  |

| Timer Operation Command Codes                | 99  |

| Timer/Periodic Interrupt                     | 99  |

| Auxiliary Commands                           | 00  |

| Getting Started                              | 02  |

| ppendix A - Example Code                     | 117 |

| Terminal Output of Program gs.c 1            | 18  |

| Programming Example                          | 20  |

# List of Figures

| Figure 1-1 | VMIVME-2540 Intelligent Counter/Controller   | 21 |

|------------|----------------------------------------------|----|

| Figure 1-2 | VMIVME-2540 System Timing Controller         | 22 |

| Figure 1-3 | QPM Direction Change Interrupt Logic         | 23 |

| Figure 1-4 | Local Bus Arbitration                        | 25 |

| Figure 1-5 | Interrupt Controller for STC Outputs         | 32 |

| Figure 1-6 | VMEbus Slave Address Decode                  | 34 |

| Figure 1-7 | Intelligent Interface Interrupter Module     | 35 |

| Figure 2-1 | VMIVME-2540 DIP Switches and Jumper Options  | 39 |

| Figure 2-2 | Example DIP Switch Settings                  | 40 |

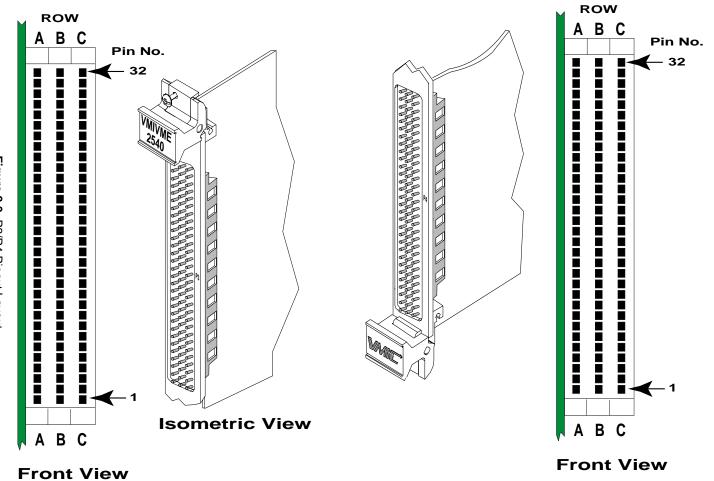

| Figure 2-3 | P3/P4 Pinout Layout                          | 44 |

| Figure 2-4 | Typical RS-422-Compatible Signal Connections | 47 |

| Figure 2-5 | Typical TTL-Compatible Signal Connections    | 47 |

VMIVME-2540 Intelligent Counter/Controller

# List of Tables

| Table 1-1  | VMIVME-2540 Local CPU Address Map                           |

|------------|-------------------------------------------------------------|

| Table 1-2  | VMIVME-2540 Local I/O Address Map                           |

| Table 2-1  | RS-422 Receiver Termination Jumper Options 40               |

| Table 2-2  | Configuration Jumpers E50 and E5141                         |

| Table 2-3  | VMEbus Access Select Jumpers E52, E53 and E5441             |

| Table 2-4  | I/O Connector P3 Pin Assignments                            |

| Table 2-5  | I/O Connector P4 Pin Assignments                            |

| Table 2-6  | Recommended Discrete Wire Connectors and Accessories        |

| Table 2-7  | TTL/Single-Ended Input Signal Compatibility Configuration46 |

| Table 3-1  | VMIVME-2540 VMEbus I/F Addresses 51                         |

| Table 3-2  | Board ID/Configuration (Offset \$0000)52                    |

| Table 3-3  | VMIVME-2540 ID/Configuration Values                         |

| Table 3-4  | Firmware Revision Level (Offset \$0002)53                   |

| Table 3-5  | Command Code (Offset \$0004)53                              |

| Table 3-6  | Command Status Code (Offset \$0006)                         |

| Table 3-7  | Command Status Interrupt Request Level (Offset \$0008)54    |

| Table 3-8  | Command Status Interrupt Vector (Offset \$0009)55           |

| Table 3-9  | Channel ID (Offset \$000A)                                  |

| Table 3-10 | Continuous/Discrete Flag (Offset \$000B)                    |

| Table 3-11 | Measurement Ready Flag (Offset \$000C)56                    |

| Table 3-12 | Measurement Channel ID (Offset \$000E)56                    |

| Table 3-13 | Channel Measurement Status (Offset \$000F)56                |

| Table 3-14 | Channel Control Block Registers                             |

| Table 3-15 | Timer Channel Control Block Registers                       |

| Table 3-16 | VMIVME-2540 Continuous/Discrete Flag Buffer                 |

| Table 3-17 | VMIVME-2540 Measurement Data Valid Flags Buffer             |

| Table 3-18 | VMIVME-2540 Firmware Release Information                    |

| Table 3-19 | VMIVME-2540 Diagnostic Buffer                                |

|------------|--------------------------------------------------------------|

| Table 3-20 | VMIVME-2540 Host Commands                                    |

| Table 3-21 | VMIVME-2540 Status Codes                                     |

| Table 3-22 | Front Panel External Clock, Gate, and Output Connections     |

| Table 3-23 | Typical CCB Format/Common Parameters                         |

| Table 3-24 | Gate/Edge Codes                                              |

| Table 3-25 | Clock Period (Time Base) Select Code                         |

| Table 3-26 | Operational Mode Select Flag                                 |

| Table 3-27 | 16-bit Event Counter Channel Control Block                   |

| Table 3-28 | 32-bit Event Counter Channel Control Block                   |

| Table 3-29 | Period Measurement Channel Control Block                     |

| Table 3-30 | Frequency Measurement Channel Control Block                  |

| Table 3-31 | Pulse-Width Measurement Channel Control Block                |

| Table 3-32 | QPM Channel Control Block                                    |

| Table 3-33 | QPM Channel Status Codes                                     |

| Table 3-34 | Integer QPM Channel Control Block                            |

| Table 3-35 | Integer Period Measurement Channel Control Block             |

| Table 3-36 | 32-bit Integer Period Measurement Channel Control Block      |

| Table 3-37 | 32-bit Pulse-Width Measurement Channel Control Block         |

| Table 3-38 | 16-bit Integer Pulse-Width Measurement Channel Control Block |

| Table 3-39 | Delayed Event Timer CCB Format                               |

| Table 3-40 | 16-bit Frequency Divider Channel Control Block               |

| Table 3-41 | 32-bit Frequency Divider Channel Control Block               |

| Table 3-42 | Period/Pulse-Width Generation Channel Control Block95        |

| Table 3-43 | Frequency/Duty Cycle Generation Channel Control Block        |

| Table 3-44 | Pulse Sequence CCB Parameters                                |

| Table 3-45 | Programmed Output CCB Parameters                             |

| Table 3-46 | Quadrature Control Output Mode                               |

| Table 3-47 | Timer/Periodic Interrupt Channel Control Block 100           |

| Table 3-48 | Block Move Diagnostic Buffer Entries 101                     |

| Table 3-49 | Diagnostic Buffer Entry for Execute Command101               |

| Table 3-50 | VMIVME-2540 Configuration Using Example Set 1 102            |

| Table 3-51 | VMIVME-2540 Configuration Using Example Set 2 102            |

| Table 3-52 | Wire Connections - Example Set 1                             |

| Table 3-53 | Wire Connections - Example Set 2                             |

# Overview

# Contents

| Reference Material List            | 15 |

|------------------------------------|----|

| Safety Summary                     | 16 |

| Safety Symbols Used in This Manual | 17 |

## Introduction

The VMIVME-2540 is an intelligent digital input/output board with a VMEbus slave interface which optionally provides 4, 8, 16, or 24 channels of digital signal measurement and signal generation capability. These measurement and signal output functions are implemented by an array of AM9513A system timing controllers (STC) and associated interface logic. An on-board VMIVME-2540 local CPU (68HC000 Microprocessor) relieves the user from the task of programming the system timing controllers directly by providing a command-driven user interface to perform the board functions. The user configures measurement, timing and output functions for each channel through a simple, memory-mapped interface consisting of commands, command status, parameters, and return measurements.

Each channel of the VMIVME-2540 consists of a 16-bit counter with clock and gate inputs and a digital waveform output. The modes of operation for the unit are:

- Event counter with programmable limit count and optional gate

- Frequency divider

- · Event-triggered interrupt with delay

- Timer/periodic VMEbus interrupt

- Period/frequency/pulse-width measurement

- Square wave/pulse train generation

- Quadrature position measurement

- Quadrature position control

Channels may be grouped in pairs for 32-bit extended precision and extended measurement modes. The channels are all buffered at the VMIVME-2540 front panel

with RS-422 line receivers and drivers. Support for single-ended TTL inputs is provided by an on-board TTL threshold voltage which may be connected externally to the inverting input of the RS-422 line receiver.

The VMEbus interface of the VMIVME-2540 consists of a 64 Kbyte static RAM memory, a command status buffer, and two interrupter modules. The 64 Kbyte memory, shared between the VMEbus and the VMIVME-2540 local CPU, is used to exchange command, command status, and parametric and measurement data. The command status buffer overlays a one word memory location with no local bus arbitration for VMEbus access to the status data. VMEbus access to the command status buffer occurs with minimal delay. The interrupter modules on the VMIVME-2540 may assert up to two VMEbus interrupts simultaneously on interrupt levels IRQ1 through IRQ7 with independent 8-bit vectors.

#### **Disclaimer: Notice About Equivalent Parts**

"In the sections which follow, reference to specific part types do not guarantee the usage of that part in the final assembly. Equivalent Integrated Circuits may be substituted in the final assembly without notification."

## **Reference Material List**

Refer to *The VMEbus Specification* for a detailed explanation of the VMEbus. *The VMEbus Specification* is available from the following source:

VITA VMEbus International Trade Association 7825 East Gelding Dr. Suite 104 Scottsdale, AZ 85260-3415 (602) 951-8866 FAX: (602) 951-0720 Email: info@vita.com

### **Physical Description and Specifications**

Refer to 800-002540-000 specification available from VMIC.

VMIC 12090 South Memorial Pkwy. Huntsville, AL 35803-3308, USA (256) 880-0444 (800) 322-3616 FAX: (256) 882-0859 www.vmic.com

## Safety Summary

The following general safety precautions must be observed during all phases of the operation, service, and repair of this product. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of this product.

VMIC assumes no liability for the customer's failure to comply with these requirements.

#### Ground the System

To minimize shock hazard, the chassis and system cabinet must be connected to an electrical ground. A three-conductor AC power cable should be used. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet.

#### Do Not Operate in an Explosive Atmosphere

Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.

#### **Keep Away from Live Circuits**

Operating personnel must not remove product covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### Do Not Service or Adjust Alone

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### **Do Not Substitute Parts or Modify System**

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to VMIC for service and repair to ensure that safety features are maintained.

#### **Dangerous Procedure Warnings**

Warnings, such as the example below, precede only potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

**STOP:** Dangerous voltages, capable of causing death, are present in this system. Use extreme caution when handling, testing, and adjusting.

# Safety Symbols Used in This Manual

Indicates dangerous voltage (terminals fed from the interior by voltage exceeding 1,000 V are so marked). Protective conductor terminal. For protection against electrical shock in case of a ⊥\_ OR (⊥) fault. Used with field wiring terminals to indicate the terminal which must be connected to ground before operating equipment. Low-noise or noiseless, clean ground (earth) terminal. Used for a signal common, as well as providing protection against electrical shock in case of a fault. Before operating the equipment, terminal marked with this symbol must be connected to ground in the manner described in the installation (operation) manual. Frame or chassis terminal. A connection to the frame (chassis) of the equipment / OR which normally includes all exposed metal structures. Alternating current (power line). Direct current (power line). Alternating or direct current (power line). STOP: Informs the operator that a practice or procedure should not be performed. Actions could result in injury or death to personnel or could result in damage to or destruction of part or all of the system. WARNING: Denotes a hazard. It calls attention to a procedure, a practice, a condition, which, if not correctly performed or adhered to, could result in injury or death to personnel. CAUTION: Denotes a hazard. It calls attention to an operating procedure, a practice, or a condition, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the system.

**NOTE:** Denotes important information. It calls attention to a procedure, a practice, a condition or the like, which is essential to highlight.

VMIVME-2540 Intelligent Counter/Controller

# Theory of Operation

# Contents

| I/O Processor              | . 24 |

|----------------------------|------|

| Local Memory               | . 30 |

| Local Interrupt Controller | . 31 |

| VMEbus Slave Interface     | . 33 |

| VMEbus Interrupter Modules | . 35 |

|                            |      |

## Introduction

### **Functional Description**

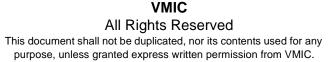

A block diagram of the VMIVME-2540 Intelligent Counter/Controller is shown in Figure 1-1 on page 21. The functions of the board may be divided into five groups:

- System timing controller front-end logic

- VMIVME-2540 local CPU interrupt controller

- VMIVME-2540 local CPU/memory/interface support logic

- VMEbus Slave DTB Interface

- VMEbus Interrupter Modules

Each of these groups will be discussed in more detail in the following sections.

#### System Timing Controller Front-End Logic

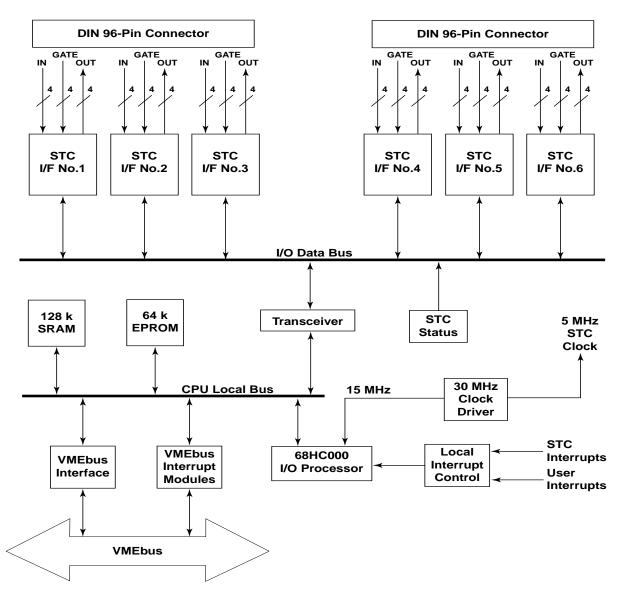

The system timing controller front-end logic consists of RS-422 buffers, synchronizing and conditioning logic, quadrature position measurement logic (QPM), and the AM9513A system timing controller, as shown in Figure 1-2 on page 22.

#### **RS-422 Line Driver and Receiver**

The RS-422 line drivers used on the VMIVME-2540 have a specified current sink/ source value of  $\pm 60$  mA and 2.0 V minimum differential output voltage. The RS-422 line receivers have a differential input voltage  $\pm 25$  V maximum. Each input is

optionally terminated with a 120 Ohm resistor (See "Jumper Options" on page 40). TTL input signal compatibility is supported by disconnecting the termination resistor, connecting TTL compatibility voltage (VTTL) at the P3 and P4 I/O connectors to the inverting input of the RS-422 line receiver, and driving the noninverting input of the RS-422 line receiver, and driving the noninverting input of the RS-422 line receiver with the TTL signal. The on-board threshold voltage source is a regulated source with output current 100 mA maximum and output voltage 1.4 V nominal. Refer to "Jumper Options" on page 40 and "TTL/Single-Ended Input Signal Compatibility Configuration" on page 46 for more information about TTL applications.

#### Synchronizer and Conditioning Logic

Each group of four clock inputs to the VMIVME-2540 are synchronized to the 5 MHz STC clock by octal registers. The synchronized clock signals feed into the source-gate conditioning logic, implemented in a programmable logic device (PLD). Each group of four gate inputs to the VMIVME-2540 are data inputs to D-flip-flop (DFF) macrocells in the source-gate conditioning logic with the DFF macrocells clocked by the corresponding synchronous clock signal. Therefore, the gate inputs to the AM9513A are guaranteed to meet setup and hold requirements relative to the corresponding synchronous clock signal and the 5 MHz STC clock.

This conditioning logic is mode dependent. There is a quadrature position measurement (QPM) mode register bit which corresponds to each pair of adjacent even/odd pair channels. When a mode register bit is zero (nonquadrature position measurement mode), the two synchronous source signals pass on directly to the AM9513A system timing controller. When a mode register bit is one, the two synchronized clock sources pass through edge-detection logic which creates a 100 ns pulse for every source edge. The quadrature clock inputs are analyzed for direction, and this direction signal selects which input to the AM9513A STC receives an edge pulse: for 16-bit quadrature position measurement, even channel numbers may be considered *clockwise*, and odd channel numbers considered *counterclockwise*.

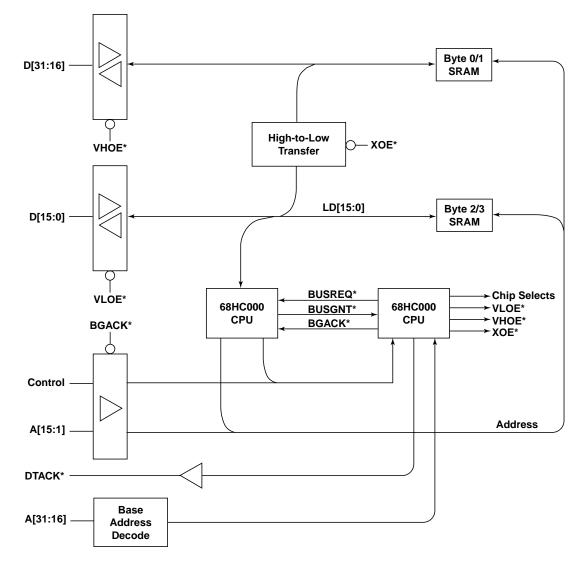

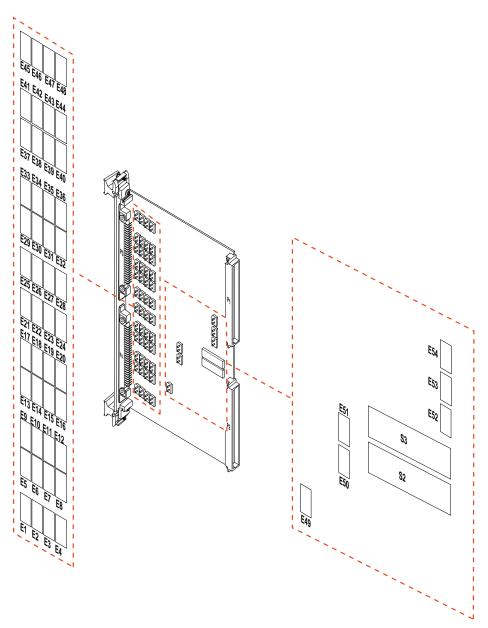

Figure 1-1 VMIVME-2540 Intelligent Counter/Controller

Figure 1-2 VMIVME-2540 System Timing Controller

The direction signal corresponding to each pair of even/odd channels is output from the source-gate conditioning logic to a latch (for the VMIVME-2540 local CPU to read) and to the QPM direction change interrupt logic. The QPM direction change logic will be discussed in a later section.

#### AM9513A System Timing Controller

The counting, timing, and waveform functions of the VMIVME-2540 are all controlled by the AM9513A STC. Each system timing controller has five very versatile 16-bit counter logic groups. Each counter logic group consists of a 16-bit counter, 16-bit load register, 16-bit hold register, and 16-bit counter mode register. In addition, counter logic groups one and two in the AM9513A have a 16-bit comparator and a 16-bit alarm register. Each 16-bit counter has programmable clocks and gate inputs from a number of sources, including the five clock and five gate inputs. Each counter logic group has a programmable output which may be configured to be inactive (high or low), terminal count (single clock cycle), or terminal count toggle (square wave). Counter logic groups may be cascaded to create higher precision 32-bit counters.

Of the five counter logic groups in the AM9513A, the VMIVME-2540 uses counters one through four to process the conditioned source and gate signals, while the fifth counter is used only for generating a periodic or delayed interrupts using the internal 5 MHz timebase. The internal timebase consists of a divider chain with four 4-bit binary/BCD counters, providing a total of five clock sources for any of the counter logic groups. These five timebase frequency sources are used by the VMIVME-2540 to measure period and pulse width using one of five available clock frequencies (200 ns to 2 ms). Refer to the *AM9513A Technical Manual (1990 rev.) or the 1987 AMD MOS Microprocessor and Peripherals Handbook* for more application information on the system timing controller.

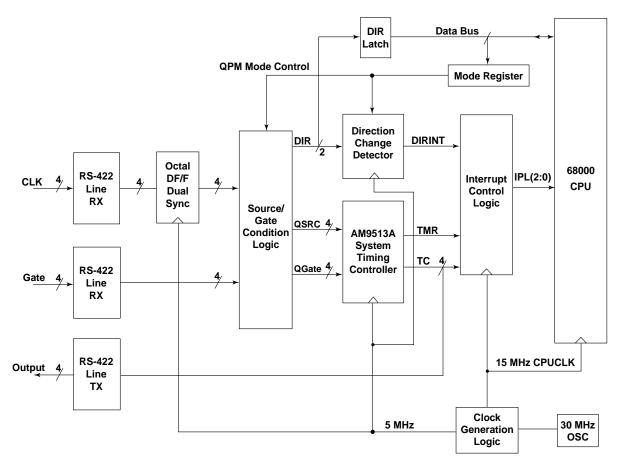

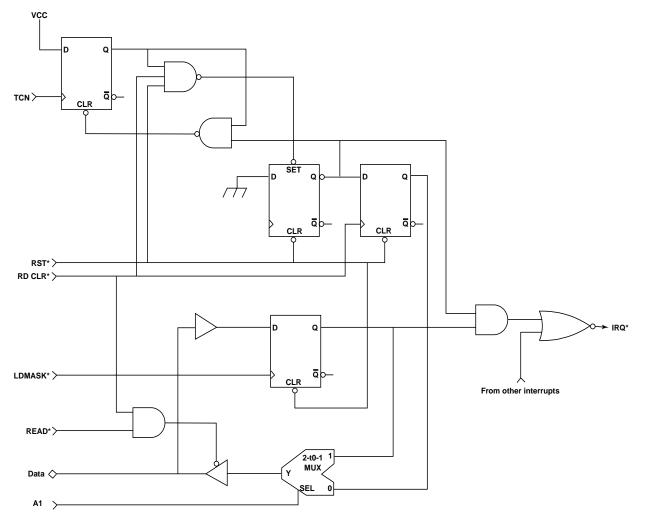

#### **QPM Direction Change Interrupt Logic**

The quadrature clock signals are synchronized to the 5 MHz STC clock by an octal register, and then the direction is detected in the source-gate conditioning logic. The direction signal goes to the QPM direction change interrupt logic, shown in Figure 1-3 below. The VMIVME-2540 local CPU uses the QPM direction change interrupt to interrogate the direction latch and record quadrature position profiles in VMEbus-accessible memory. The quadrature position measurement direction change interrupt logic is implemented using programmable logic.

Figure 1-3 QPM Direction Change Interrupt Logic

# I/O Processor

### 68HC000 CPU

The on-board intelligence of the VMIVME-2540 is provided by a 68HC000 microprocessor with a 15 MHz CPU clock. The HCMOS CPU has external 16-bit data/24-bit address buses, internal 32-bit data paths, and is a complex instruction set computer (CISC). Refer to *Motorola M68000 User's Manual*, 7th edition for more detail about the 68HC000.

### **Decode and Control Logic**

All of the address decode, interrupt control, and arbitration functions for the local CPU are partitioned between two 68-pin PLDs. One PLD provides the following address decode and arbitration functions for the 68HC000:

- Local bus arbitration

- Local SRAM and EPROM chip selects

- Local I/O block decode and R/W strobes

- Data transceiver output controls

- User Command Interrupt/Command Status Buffer controls

- VMEbus DTACK and write strobe generation

- 15 MHz CPU clock and 5 MHz STC clock generation

The other PLD provides the following address decode and interrupt control functions:

- System timing controller chip selects decode

- QPM Mode Register and Direction Latch control strobes

- Local interrupt controller R/W strobes

- 68HC000 Interrupt Acknowledge bus cycle decode

- Local interrupt priority encoding IPL(0:2)

- Configuration buffer /Status LED control

- Front panel reset /VMEbus reset combination into local reset signal

#### **Local Bus Arbitration**

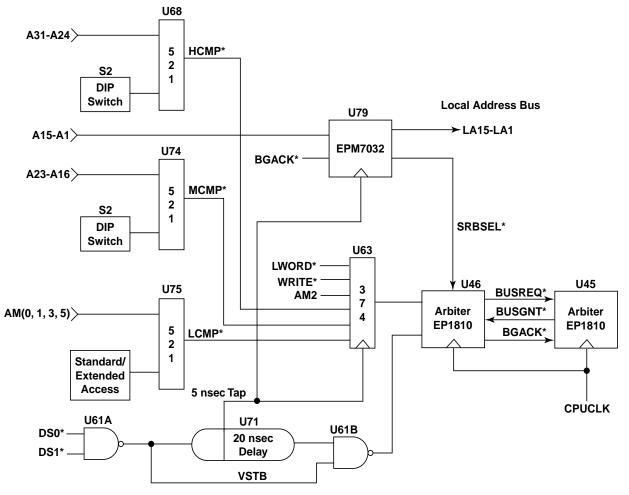

The VMEbus may access a 64 Kbyte block of static RAM on the VMIVME-2540 board that is shared with the local 68HC000 CPU. This shared RAM and local data and address buses have two possible masters: the CPU has default control, while the VMEbus must request access. Figure 1-4 on page 25 shows the local resources arbitrated by PLD logic.

A bus request is issued to the 68HC000 whenever the following conditions are met:

- a. A31:A24 matches the setting of DIP switch S2 (A32 mode only)

- b. A23:A16 matches the setting of DIP switch S3

- c. AM[5:0] matches the code for standard or extended data access

- d. AM2 and jumpers E53/E54 match supervisory/nonprivileged access type

- e. Signals IACK\*, BGACK\*, and SRBSEL\* are not asserted.

Figure 1-4 Local Bus Arbitration

The 68HC000 responds with a Bus Grant within 1.5 to 3.5 clock cycles after it completes the current bus cycle. One clock cycle after BUSGNT\* is asserted, the local bus arbiter asserts Bus Grant Acknowledge (BGACK\*), enabling the VMEbus buffers and local SRAM chip selects. VMEbus DTACK\* is asserted synchronously to terminate the access, after which the VMEbus master withdraws control. Back-to-back and read-modify-write VMEbus accesses are not supported by the local bus arbiter: the 68HC000 executes its firmware in the same SRAM chips accessed by the VMEbus, thus the VMIVME-2540 local CPU is always granted the local bus after a VMEbus access.

### Local Address Decode

The memory map of the board local resources occupies 1 Mbyte of the 16 Mbyte 68HC000 address space, thus only LA[19:1] are decoded. Table 1-1 below and Table 1-2 on page 27 list the local CPU and the local I/O address maps for the VMIVME-2540. The addresses in the tables are **not** accessible from the VMEbus; these are local resources accessed by the local CPU using those addresses. Note that for all local I/O addresses, three signals are decoded: IOSEL\*, IORD\*, and IOWR\*. All local address decode applies to the VMIVME-2540 local CPU only. The VMEbus shared memory is accessible from both the local bus and the VMEbus; however, the local CPU address space used to access this memory has no correlation to the address space used for VMEbus access. This latter address space is user-controlled via switch settings.

| HEX Address    | Function                          |

|----------------|-----------------------------------|

| 00000 to 0FFFF | EPROM Firmware                    |

| 10000 to 7FFFF | Not Used                          |

| 80000 to 8FFFF | I/O Address Space                 |

| 90000 to DFFFF | Not Used                          |

| E0000 to EFFFF | Static RAM - local access only    |

| F0000 to FFFFF | Static RAM – VMEbus-shared access |

Table 1-1 VMIVME-2540 Local CPU Address Map

| HEX Address    | Mnemonic | Function                                       | Comments    |

|----------------|----------|------------------------------------------------|-------------|

| 80000          | RDCFG    | Read board configuration straps                | D14, D15    |

| 80000          | WRENA    | Write master interrupt enable to ID15          | 1 = enabled |

| 80002          | WRLED    | Write status LED value to ID15                 | 1 = on      |

| 80004          | CLRCMD   | Clear VMEbus command interrupt F/F             |             |

| 80006          | MODE     | Quadrature Position Measurement Mode           | Read/Write  |

| 80008          | RDDIR    | Read 16-bit QPM direction latch                |             |

| 8000A          | LDSRB    | Load Slave Response Buffer (Command Status)    | Write-only  |

| 80010          | VA[3:0]  | VMEbus Interrupt Vector 'A' low nibble         | IIIC        |

| 80012          | VA[7:4]  | VMEbus Interrupt Vector 'A' high nibble        | IIIC        |

| 80014          | IRQA     | VMEbus Interrupt 'A' IRQ level                 | IIIC        |

| 80018          | VB[3:0]  | VMEbus Interrupt Vector 'B' low nibble         | IIIC        |

| 8001A          | VB[7:4]  | VMEbus Interrupt Vector 'B' high nibble        | IIIC        |

| 8001C          | IRQB     | VMEbus Interrupt 'B' IRQ level                 | IIIC        |

| 80020          | LTCRD    | Read and Clear Interrupt Controller No.1 IRQs  | TC0 - TC11  |

| 80022          | LMASK    | Write - Load Interrupt Controller No.1 mask    | TC0 - TC11  |

| 80022          | LMRD     | Read - Read Interrupt Controller No.1 mask     | TC0 - TC11  |

| 80024          | UTCRD    | Read and Clear Interrupt Controller No. 2 IRQs | TC12 - TC23 |

| 80026          | UMASK    | Write - Load Interrupt Controller No. 2 mask   | TC12 - TC23 |

| 80026          | UMRD     | Read - Read Interrupt Controller No. 2 mask    | TC12 - TC23 |

| 80028          | TMRRD    | Read and Clear Interrupt Controller No. 3 IRQs | TMR0 - TMR5 |

| 8002A          | TMASK    | Write - Load Interrupt Controller No. 3 mask   | TMR0 - TMR5 |

| 8002A          | TMRD     | Read - Read Interrupt Controller No. 3 mask    | TMR0 - TMR5 |

| 8002C          | CLRDIR   | Clear Direction Change Interrupt Controller    |             |

| 80030 to 8003F | -        | Not used.                                      |             |

| 80040          | STC0D    | STC0 Data Port                                 |             |

| 80042          | STC0C    | STC0 Control Port                              |             |

| 80044          | STC1D    | STC1 Data Port                                 |             |

| 80046          | STC1C    | STC1 Control Port                              |             |

| 80048          | STC2D    | STC2 Data Port                                 |             |

| 8004A          | STC2C    | STC2 Control Port                              |             |

| 8004C          | STC3D    | STC3 Data Port                                 |             |

| 8004E          | STC3C    | STC3 Control Port                              |             |

| 80050          | STC4D    | STC4 Data Port                                 |             |

| 80052          | STC4C    | STC4 Control Port                              |             |

| 80054          | STC5D    | STC5 Data Port                                 |             |

| 80056          | STC5C    | STC5 Control Port                              |             |

| 80058 to 8FFFF | -        | Not used.                                      |             |

#### Table 1-2 VMIVME-2540 Local I/O Address Map

#### Local I/O Functions

The I/O functions accessed by the VMIVME-2540 local CPU are the AM9513A system timing controllers, the VMEbus interrupter modules and local QPM, and configuration and status LED interfaces.

- **a. Configuration Buffer:** The VMIVME-2540 may have one, two, four, or six AM9513A system timing controllers, depending on the ordering option for the board. The number of system timing controllers present on the VMIVME-2540 board is encoded into configuration jumpers E50 and E51 as shown in Table 2-2 on page 41. The VMIVME-2540 local CPU reads these configuration jumpers with a buffer enabled by address \$80000 during initialization.

- **b. Master Interrupt Enable:** The local interrupt controller for the VMIVME-2540 local CPU may be completely disabled by writing a *zero* to address \$80000. This master interrupt enable flip-flop is cleared by the RESET\* signal and set by the VMIVME-2540 local CPU when initialization is complete.

- **c. Status LED:** The front panel status LED is controlled by local I/O address \$80002. The LED is illuminated when the VMIVME-2540 local CPU writes a logic one to this address and extinguished by a logic *zero*. The status LED is illuminated when the local CPU begins powerup/reset self-test, and extinguished when the self-test is completed. Thereafter, the LED will be illuminated if a failure or fatal error is detected. The processor is always halted and interrupts are disabled when a failure occurs and the LED is illuminated. The shared memory area remains accessible by the host for diagnostic information retrieval.

- **d. Clear VMEbus Command Interrupt:** The VMEbus command interrupt flip-flop is cleared when the VMIVME-2540 local CPU asserts I/O address \$80004.

- e. Quadrature Position Measurement Mode Register: The QPM mode register has read/write access at I/O address \$80006. Although the QPM mode register is implemented with two octal devices, only the least significant 12 bits are physically connected to the STC front-end logic.

- **f. QPM Direction Latch:** The current direction of all quadrature channels may be read by the VMIVME-2540 local CPU at address \$80008. As with the QPM Mode Register, this function is implemented with two octal latches, but only the least significant 12 bits contain direction information.

- **g. Command Status Buffer:** The Command Status Buffer is an octal register located at local I/O address \$8000A. Only the local VMIVME-2540 local CPU may write to this location. For the VMEbus host, this is a read-only buffer.

- **h. Intelligent Interface Interrupt Controller (IIIC):** The VMIVME-2540 local CPU may assert VMEbus interrupts by writing vectors and IRQ levels to the Intelligent Interface Interrupt Controller, located at I/O addresses \$80010-\$80014 and \$80018-\$8001C. The IIIC has only a 4-bit read/write data interface to the VMIVME-2540 local CPU, requiring each value to be written in successive nibbles.

- **i. Terminal Count Interrupt Controllers:** The system timing controller outputs TC[0:23] and TMR[0:5] comprise 30 interrupt sources to the VMIVME-2540 local CPU. These terminal count signals are logically arranged into three groups: signals TC[0:11] are conditioned by Interrupt Controller No.1, signals

TC[12:23] are handled by Interrupt Controller No. 2, and signals TMR[0:5] are combined and masked by Interrupt Controller No. 3. For each interrupt controller, the interrupt sources are captured into a register which may be read and cleared automatically by the VMIVME-2540 local CPU. Each interrupt controller also has a read/write mask register. An interrupt source is masked by a zero value and enabled by a logic one.

**j. System Timing Controller Ports:** The system timing controllers are addressed by the VMIVME-2540 local CPU as only two locations each: a control port and a data port. Transfers at the control port allow direct access to the STC command register when writing, and the STC status register when reading. All other STC internal locations are accessed through the data port with the desired location addressed by the STC data pointer register. Refer to the Advanced Micro Devices' **AM9513A/AM9513 Technical Manual** for more information about the system timing controller.

## Local Memory

### **EPROM Firmware**

The VMIVME-2540 local CPU retrieves its startup code and local interrupt vectors from two programmed EPROM ICs. The VMIVME-2540 local CPU fetches instructions and data from memory, word accesses (16 bits). Program execution is started in EPROM at powerup and, after RAM memory test is completed, code is copied to static RAM, program control is passed to RAM, and all program execution is from RAM from that point. The design of the LDTACK wait-state generator for the VMIVME-2540 local CPU dictates that the EPROMs have a data access time of 250 ns or less.

The EPROM firmware contains all programming to support the user programming of the board described in the "Programming" on page 49. The user controls the input/ output operations performed by the system timing controllers using the command/ command status interface and the channel control blocks, as described in Chapter 3 "Programming".

#### Static RAM

The VMIVME-2540 local CPU has zero-wait-state access to 128 Kbyte of static RAM located in four 32 Kbyte x 8 ICs. As shown in Figure 1-4 on page 25, the VMIVME-2540 local CPU accesses this static RAM 16 bits at a time. For each longword in memory, bytes 2 and 3 connect directly to the VMIVME-2540's local CPU 16-bit data bus, while bytes 0 and 1 are accessed through the data transfer transceivers. Strobes LWRSTB\* and UWRSTB\*, decoded from LDS\* and UDS\*, respectively, allow the 68HC000 to modify lower and upper bytes of static RAM independently. The design of the LDTACK wait-state generator for the VMIVME-2540 local CPU requires the use of static RAMs with a data access time of 45 ns or less for zero-wait-state operation.

A portion of the static RAM is interfaced to the VMEbus for sharing with the VMEbus host processor for control and communication. The VMEbus access to the static RAM may be either byte, word, or longword. The local bus arbitration logic only allows the VMEbus host to access the upper 64 Kbyte of the RAM, while the 68HC000 has granted the local bus. During the VMEbus access cycle, the assertion of RAM chip enables and write enables are synchronous to CPUCLK. VMEbus DTACK\* is asserted one clock cycle after the rising edge of RAM write strobe during a VMEbus write cycle, ensuring the integrity of the written data.

# Local Interrupt Controller

The local 68HC000 interrupt controller encodes 32 interrupt sources into seven prioritized interrupt request levels. STC terminal count signals TC[11:0] are grouped into 68HC000 IRQ level 6, signals TC[23:12] are grouped into IRQ level 5, and signals TMR[5:0] are grouped into IRQ level 4. The VMEbus command interrupt asserts IRQ level 7, while the quadrature direction change interrupt is mapped into 68HC000 IRQ level 3. IRQ levels 1 and 2 are not used in the VMIVME-2540 interrupt structure. The QPM direction change interrupt is described in "QPM Direction Change Interrupt Logic" on page 23. The following sections will describe STC and the VMEbus command interrupt sources.

#### **STC Interrupts**

Each system timing controller has five, 16-bit counters with programmable terminal count outputs. Each terminal count output may be programmed either to be high, low, a single clock pulse wide, or square wave output. In each STC, counters one through four are associated with the front panel I/O connectors and are members of the TC[23:0] bus, while the fifth counter output is intended only for creating a *soft* interrupt after a specified time and is a member of the TMR[5:0] bus. The STC terminal count interrupts are masked and edge-detected by 6-bit interrupt controllers, implemented via PLD logic. The logic inside the interrupt controller is shown in Figure 1-5 on page 32.

#### VMEbus Command Interrupt

The VMEbus asserts the command interrupt to the VMIVME-2540 local CPU by writing the command code to offset \$0004 from the base address. PLD logic decodes this address and sets an internal flip-flop during the VMEbus command bus cycle. The VMIVME-2540 local CPU resets the command interrupt flip-flop by asserting local address \$8000A.

Figure 1-5 Interrupt Controller for STC Outputs

## **VMEbus Slave Interface**

#### VMEbus Slave Address Decode

The "Local Bus Arbitration" on page 24, was discussed in a general sense. Figure 1-6 on page 34 shows the actual VMEbus slave address decode logic and address snapshot registers on the VMIVME-2540 board. Comparators assert signals HCMP\*, MCMP\*, and LCMP\* when the VMEbus address and address modifiers match the settings of DIP switches S1, S2, and the code for standard/extended data access.

The VMEbus specification requires that the address and control signals be stable for at least 10 ns prior to the assertion of DS0\*/DS1\*, and held valid a minimum of 30 ns after this assertion. DS0\*/DS1\* is combined to create the signal VSTB, the composite active-high VMEbus data strobe. A sufficient time after the rising edge of VSTB, the signal VACLK takes a snapshot of the VMEbus address comparison signals HCMP\*, MCMP\*, and LCMP\*, control signals LWORD\*, WRITE\*, AM2, and the lower VMEbus address bus. Thus, all of the VMEbus lower address control, and board select information is held constant until the next falling edge of DS0\*/DS1\*.

A delay line is used to shorten the leading edge of VSTB\* so that all registered address and control information is valid going into the local bus arbiter. Once VSTB\* is asserted and all other comparison information is valid, the PLD logic asserts BUSREQ\* asynchronously to the VMIVME-2540 local CPU (the 68HC000), and the VMEbus access proceeds as described in "Local Bus Arbitration" on page 24.

#### **Command Status Code**

When the VMIVME-2540 local CPU has finished processing a commanded action, a command status code is placed in the command status buffer. The VMEbus host can poll this register with minimal delay since it is not arbitrated as a local resource. This command status buffer benefits the VMIVME-2540 local CPU by increasing the portion of the local bus bandwidth dedicated to the VMIVME-2540 local CPU, and not to VMEbus access service. The address decode for the VMEbus polling buffer occurs in two parts: the upper 16 address lines by one PLD device, while the lower sixteen address lines are decoded a second PLD. The second device generates signal SRBSEL\* which is connected to the first PLD device. The first PLD then generates signal SRBOE\* if the VMEbus data access address is offset \$0006 from the base address. Signal SRBOE\* enables the status code data onto the VMEbus interrupter module described in the next section. The VMEbus DTACK\* delay from decode of signal SRBOE\* is one to two 15 MHz clock periods.

Figure 1-6 VMEbus Slave Address Decode

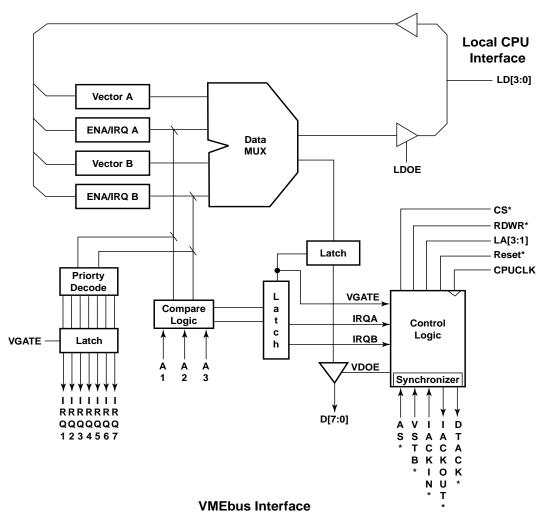

## **VMEbus Interrupter Modules**

The VMIVME-2540 has two interrupt modules implemented in PLD. Figure 1-7 below shows the block diagram of the Intelligent Interface Interrupter Module. This design allows the 68HC000 microprocessor to interrupt a VMEbus master on any two of the seven IRQ levels simultaneously without requiring the arbitration for the local bus during the IACK cycle.

The VMIVME-2540 local CPU programs the interrupter module through a 4-bit bidirectional data port by asserting CS\*, RDWR\* and the 3-bit address of the nibble to be written. Vectors A and B are 8-bit registers which contain the VMEbus interrupt vectors. ENA/IRQA and ENA/IRQB are 4-bit registers which contain the 3-bit VMEbus IRQ level to be asserted and IRQ enable. The status of these registers may be verified at any time by the VMIVME-2540 local CPU through the same local data port. Refer to Table 1-2 on page 27 for address decode information. Note that writing the code 8 to either IRQ/enable control location does not enable a VMEbus IRQ level (there is no IRQ 0).

Figure 1-7 Intelligent Interface Interrupter Module

VMIVME-2540 Intelligent Counter/Controller

# **Configuration and Installation**

# Contents

| Unpacking Procedures                                      | 38 |

|-----------------------------------------------------------|----|

| Configuration                                             | 39 |

| /O Connector Pin Assignments                              | 42 |

| Recommended Discrete Wire Connectors and Terminal Blocks  | 45 |

| TTL/Single-Ended Input Signal Compatibility Configuration | 46 |

|                                                           |    |

# **Unpacking Procedures**

**CAUTION:** Some of the components assembled on VMIC's products may be sensitive to electrostatic discharge and damage may occur on boards that are subjected to a high-energy electrostatic field. When the board is placed on a bench for configuring, etc., it is suggested that conductive material should be inserted under the board to provide a conductive shunt. Unused boards should be stored in the same protective boxes in which they were shipped.

Upon receipt, any precautions found in the shipping container should be observed. All items should be carefully unpacked and thoroughly inspected for damage that might have occurred during shipment. The board(s) should be checked for broken components, damaged printed circuit board(s), heat damage, and other visible contamination. All claims arising from shipping damage should be filed with the carrier and a complete report sent to VMIC together with a request for advice concerning the disposition of the damaged item(s).

# Configuration

The VMIVME-2540 printed circuit board has two 8-position DIP switches and several jumper options, as shown in Figure 2-1 below. The configurations of these options are discussed in the following sections.

Figure 2-1 VMIVME-2540 DIP Switches and Jumper Options

## **DIP Switch Settings**

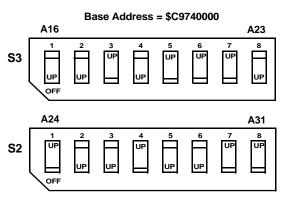

The VMEbus base address of the VMIVME-2540 is set by 8-position DIP switches S2 and S3. The settings of DIP switch S2 correspond to VMEbus address bits A31 through A24, while the settings of DIP switch S3 correspond to VMEbus address bits A23 through A16. Setting an individual switch to the **on** position matches a *zero* address bit value, conversely, a *one* address bit value compares to the **off** position. Figure 2-2 below shows the settings for DIP switches S2 and S3 for a sample VMEbus address range.

Figure 2-2 Example DIP Switch Settings

### **Jumper Options**

The VMIVME-2540 printed circuit board has 51 user-configurable and three fixed jumper options as shown in Figure 2-1 on page 39. Forty-eight of the user-configurable jumper options (E1 through E48) allow the user to remove the RS-422 receiver termination resistors for TTL compatibility. Table 2-1 below shows the correspondence between jumpers E1-E48 and channel 0 to 23 clock and gate receiver termination resistors.

**NOTE:** Proper RS-422 line termination uses only one 120 termination resistor. Line driver damage can result from driving more than one termination resistor.

| Input  | Jumper | Input   | Jumper | Input   | Jumper | Input   | Jumper |

|--------|--------|---------|--------|---------|--------|---------|--------|

| CLOCK0 | E28    | CLOCK6  | E40    | CLOCK12 | E4     | CLOCK18 | E16    |

| GATE0  | E27    | GATE6   | E39    | GATE12  | E3     | GATE18  | E15    |

| CLOCK1 | E26    | CLOCK7  | E38    | CLOCK13 | E2     | CLOCK19 | E14    |

| GATE1  | E25    | GATE7   | E37    | GATE13  | E1     | GATE19  | E13    |

| CLOCK2 | E32    | CLOCK8  | E44    | CLOCK14 | E8     | CLOCK20 | E20    |

| GATE2  | E31    | GATE8   | E43    | GATE14  | E7     | GATE20  | E19    |

| CLOCK3 | E30    | CLOCK9  | E42    | CLOCK15 | E6     | CLOCK21 | E18    |

| GATE3  | E29    | GATE9   | E41    | GATE15  | E5     | GATE21  | E17    |

| CLOCK4 | E36    | CLOCK10 | E48    | CLOCK16 | E12    | CLOCK22 | E24    |

| GATE4  | E35    | GATE10  | E47    | GATE16  | E11    | GATE22  | E23    |

| CLOCK5 | E34    | CLOCK11 | E46    | CLOCK17 | E10    | CLOCK23 | E22    |

| GATE5  | E33    | GATE11  | E45    | GATE17  | E9     | GATE23  | E21    |

| Table 2-1 | RS-422 Receiver | Termination Jumper Options |

|-----------|-----------------|----------------------------|

|           |                 |                            |

Jumper option E49 corresponds to the type of EPROMs installed on the VMIVME-2540 board and is installed at the factory.

Jumper options E51 and E50 correspond to the VMIVME-2540 ordering options and are installed by the factory. Table 2-2 below list the placement of wire jumpers E50 and E51 and the corresponding configurations.

| Dash | E50       | E51       | Configuration        |

|------|-----------|-----------|----------------------|

| -000 | Installed | Installed | Four Channels        |

| -100 | No Jumper | Installed | Eight Channels       |

| -200 | Installed | No Jumper | Sixteen Channels     |

| -300 | No Jumper | No Jumper | Twenty-Four Channels |

Table 2-2 Configuration Jumpers E50 and E51

Jumper option E52 controls whether the VMIVME-2540 responds to standard VMEbus address space (A24) or extended VMEbus address space (A32). With the shunt installed at location E52, the VMIVME-2540 is configured as an A32 VMEbus slave. When location E52 does not have a shunt installed, the board is configured as an A24 VMEbus slave.

Jumper options E53 and E54 determine whether the VMIVME-2540 will occupy supervisory only, nonprivileged only, or both supervisory and nonprivileged VMEbus address spaces. Table 2-3 below list the placements of jumper E52, E53 and E54 with the corresponding responses of the VMIVME-2540 board.

| VMEbus Access Type                           | E52        | E53       | E54       |

|----------------------------------------------|------------|-----------|-----------|

| Supervisory Only-Standard/A24                | No Jumper  | Installed | No Jumper |

| Nonprivileged Only - Standard/A24            | No Jumper  | Installed | Installed |

| Supervisory Only - Extended/A32              | Installed  | Installed | No Jumper |

| Nonprivileged Only - Extended/A32            | Installed  | Installed | Installed |

| Supervisory and Nonprivileged - Standard/A24 | No Jumper  | No Jumper | No Jumper |

| Supervisory and Nonprivileged - Extended/A32 | Installed  | No Jumper | No Jumper |

| VMEbus Response Disabled                     | Don't Care | No Jumper | Installed |

Table 2-3 VMEbus Access Select Jumpers E52, E53 and E54

# I/O Connector Pin Assignments

The VMIVME-2540 front panel connector pin assignments are shown in Table 2-4 below for P3 and Table 2-5 on page 43 for P4. Connector orientation is shown in Figure 2-3 on page 44. P3 and P4 are DIN 41612 Type C 96-pin male connectors with multiple fixing brackets. Each connector supports 12 measurement/control channels consisting of differential clock, gate, and output signals as well as ground and TTL-compatibility voltage (VTTL) pins. The VTTL voltage is a nominal 1.4 V source which may be externally tied to the inverting input of the RS-422 line receivers for TTL input compatibility.

| Pin | Signal | Pin | Signal  | Pin | Signal |

|-----|--------|-----|---------|-----|--------|

| A32 | CLK11- | B32 | GATE11- | C32 | OUT11- |

| A31 | CLK11+ | B31 | GATE11+ | C31 | OUT11+ |

| A30 | VTTL   | B30 | GND     | C30 | VTTL   |

| A29 | CLK10- | B29 | GATE10- | C29 | OUT10- |

| A28 | CLK10+ | B28 | GATE10+ | C28 | OUT10+ |

| A27 | GND    | B27 | VTTL    | C27 | GND    |

| A26 | CLK9-  | B26 | GATE9-  | C26 | OUT9-  |

| A25 | CLK9+  | B25 | GATE9+  | C25 | OUT9+  |

| A24 | CLK8-  | B24 | GATE8-  | C24 | OUT8-  |

| A23 | CLK8+  | B23 | GATE8+  | C23 | OUT8+  |

| A22 | VTTL   | B22 | GND     | C22 | VTTL   |

| A21 | CLK7-  | B21 | GATE7-  | C21 | OUT7-  |

| A20 | CLK7+  | B20 | GATE7+  | C20 | OUT7+  |

| A19 | GND    | B19 | VTTL    | C19 | GND    |

| A18 | CLK6-  | B18 | GATE6-  | C18 | OUT6-  |

| A17 | CLK6+  | B17 | GATE6+  | C17 | OUT6+  |

| A16 | CLK5-  | B16 | GATE5-  | C16 | OUT5-  |

| A15 | CLK5+  | B15 | GATE5+  | C15 | OUT5+  |

| A14 | VTTL   | B14 | GND     | C14 | VTTL   |

| A13 | CLK4-  | B13 | GATE4-  | C13 | OUT4-  |

| A12 | CLK4+  | B12 | GATE4+  | C12 | OUT4+  |

| A11 | GND    | B11 | VTTL    | C11 | GND    |

| A10 | CLK3-  | B10 | GATE3-  | C10 | OUT3-  |

| A9  | CLK3+  | B9  | GATE3+  | C9  | OUT3+  |

| A8  | CLK2-  | B8  | GATE2-  | C8  | OUT2-  |

| A7  | CLK2+  | B7  | GATE2+  | C7  | OUT2+  |

| A6  | VTTL   | B6  | GND     | C6  | VTTL   |

| A5  | CLK1-  | B5  | GATE1-  | C5  | OUT1-  |

| A4  | CLK1+  | B4  | GATE1+  | C4  | OUT1+  |

| A3  | GND    | B3  | VTTL    | C3  | GND    |

| A2  | CLK0-  | B2  | GATE0-  | C2  | OUT0-  |

| A1  | CLK0+  | B1  | GATE0+  | C1  | OUT0+  |

Table 2-4 I/O Connector P3 Pin Assignments

| PIN | SIGNAL | PIN | SIGNAL  | PIN | SIGNAL |  |  |

|-----|--------|-----|---------|-----|--------|--|--|

| A32 | CLK23- | B32 | GATE23- | C32 | OUT23- |  |  |

| A31 | CLK23+ | B31 | GATE23+ | C31 | OUT23+ |  |  |

| A30 | VTTL   | B30 | GND     | C30 | VTTL   |  |  |

| A29 | CLK22- | B29 | GATE22- | C29 | OUT22- |  |  |

| A28 | CLK22+ | B28 | GATE22+ | C28 | OUT22+ |  |  |

| A27 | GND    | B27 | VTTL    | C27 | GND    |  |  |

| A26 | CLK21- | B26 | GATE21- | C26 | OUT21- |  |  |

| A25 | CLK21+ | B25 | GATE21+ | C25 | OUT21+ |  |  |

| A24 | CLK20- | B24 | GATE20- | C24 | OUT20- |  |  |

| A23 | CLK20+ | B23 | GATE20+ | C23 | OUT20+ |  |  |

| A22 | VTTL   | B22 | GND     | C22 | VTTL   |  |  |

| A21 | CLK19- | B21 | GATE19- | C21 | OUT19- |  |  |

| A20 | CLK19+ | B20 | GATE19+ | C20 | OUT19+ |  |  |

| A19 | GND    | B19 | VTTL    | C19 | GND    |  |  |

| A18 | CLK18- | B18 | GATE18- | C18 | OUT18- |  |  |

| A17 | CLK18+ | B17 | GATE18+ | C17 | OUT18+ |  |  |

| A16 | CLK17- | B16 | GATE17- | C16 | OUT17- |  |  |

| A15 | CLK17+ | B15 | GATE17+ | C15 | OUT17+ |  |  |

| A14 | VTTL   | B14 | GND     | C14 | VTTL   |  |  |

| A13 | CLK16- | B13 | GATE16- | C13 | OUT16- |  |  |

| A12 | CLK16+ | B12 | GATE16+ | C12 | OUT16+ |  |  |

| A11 | GND    | B11 | VTTL    | C11 | GND    |  |  |

| A10 | CLK15- | B10 | GATE15- | C10 | OUT15- |  |  |

| A9  | CLK15+ | B9  | GATE15+ | C9  | OUT15+ |  |  |

| A8  | CLK14- | B8  | GATE14- | C8  | OUT14- |  |  |

| A7  | CLK14+ | B7  | GATE14+ | C7  | OUT14+ |  |  |

| A6  | VTTL   | B6  | GND     | C6  | VTTL   |  |  |

| A5  | CLK13- | B5  | GATE13- | C5  | OUT13- |  |  |

| A4  | CLK13+ | B4  | GATE13+ | C4  | OUT13+ |  |  |

| A3  | GND    | B3  | VTTL    | C3  | GND    |  |  |

| A2  | CLK12- | B2  | GATE12- | C2  | OUT12- |  |  |

| A1  | CLK12+ | B1  | GATE12+ | C1  | OUT12+ |  |  |

Table 2-5 I/O Connector P4 Pin Assignments

44

2 VMIVME-2540 Intelligent Counter/Controller

# **Recommended Discrete Wire Connectors and Terminal Blocks**

The VMIVME-2540 has a large amount of front panel I/O which must be broken out by cabling and possibly rack-mounted terminal blocks. If the user wishes to use discrete wire connectors and cables, the suggested manufacturer is *Harting Elektronik, Inc., 2155 Stonington Ave., Suite 212, P.O. Box 95710, Hoffman Estates, Illinois 60195-0710.* The recommended connector components for cabling to P3 and P4 are given in the table below.

| COMPONENT                      | HARTING CATALOG # |

|--------------------------------|-------------------|

| 96-pin Discrete Wire Connector | 0903-096-3214     |

| Female Crimp Contacts          | 0902-000-8484     |

| Connector Shell Housing        | 0903-096-0501     |

| Left-Locking Lever             | 0902-000-9902     |

| Right-Locking Lever            | 0902-000-9903     |

Table 2-6 Recommended Discrete Wire Connectors and Accessories

The RS-422 differential signals should be connected by twisted-pair insulated wires, 24 AWG solid or stranded copper conductors (R < 30/1,000 ft for other conductors) with a maximum cable length of 4,000 feet. Care should be taken to ensure that each signal group is properly grounded for reliable operation.

TTL signals may be connected by flat 96-conductor ribbon cable, 30 AWG insulated copper-stranded conductor. The corresponding female 96-pin DIN connector for flat-ribbon cable is ERNI 913.031 or similar. It is recommended that the total cable length be 50 feet or less for the TTL application with attention given to maximum signal transition rate and signal degradation over distance. RS-422 differential interface is clearly superior for longer cable lengths.

If the user wishes the I/O signals from the VMIVME-2540 front panel to be broken out at terminal blocks, the VMIACC-BT04 Dual 96-pin Transition Panel is suggested. The VMIACC-BT04 is a 19-inch rack-mountable panel which breaks all 192 signals out from two DIN 96-pin connectors to standard terminal blocks. Connection between the VMIACC-BT04 and the VMIVME-2540 front panel is made by 96-conductor ribbon cables, three foot length recommended.

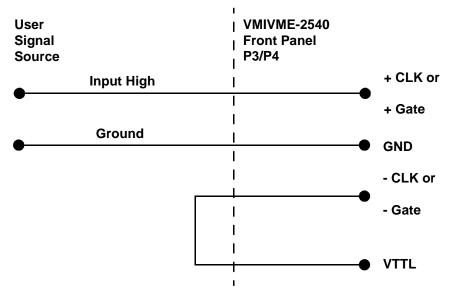

# **TTL/Single-Ended Input Signal Compatibility Configuration**

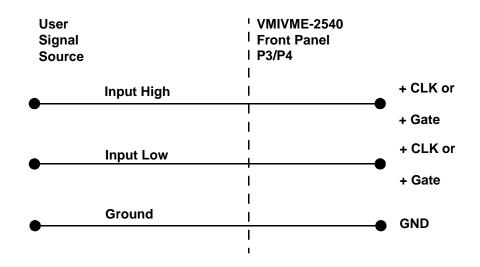

The VMIVME-2540 can be configured for single-ended input signals on a channel-by-channel basis by removing jumper shunts and externally wiring the TTL compatibility voltage (VTTL) to the corresponding inverting input of the RS-422 line receiver (inputs with a (-) suffix). Connection of the VTTL input to the (-) input will establish the VTTL voltage level as the threshold for the single-ended input signal at the (+) input. This input signal is connected to the noninverting input of the RS-422 line receiver (inputs with a (+) suffix). Care must be taken to limit the voltage range of the input signal when the jumper shunts are removed. Also, exercise caution in the connection of the VTTL signal to the (-) input(s) to avoid damage to the VTTL voltage generation circuitry of the VMIVME-2540. Select the channels which are to be configured for TTL operation, remove the associated gate and clock jumpers for those channels. Make the associated wiring changes for VTTL-to-input on the P3 and/or P4 front panel connectors.Table 2-7 below is the TTL/Single-Ended signal configuration. Figure 2-4 on page 47 is a typical RS-422 Signal connection and Figure 2-5 is the typical TTL signal connection.

| Clock<br>Input | Remove<br>Jumper | Gate<br>Input | Remove<br>Jumper | VTTL<br>Feedback | Ground<br>Reference |

|----------------|------------------|---------------|------------------|------------------|---------------------|

| CLOCK0         | E28              | GATE0         | E27              | P3-B3            | P3-A3               |

| CLOCK1         | E26              | GATE1         | E25              | P3-A6            | P3-C3               |

| CLOCK2         | E32              | GATE2         | E31              | P3-C6            | P3-B6               |

| CLOCK3         | E30              | GATE3         | E29              | P3-B11           | P3-A11              |

| CLOCK4         | E36              | GATE4         | E35              | P3-A14           | P3-C11              |

| CLOCK5         | E34              | GATE5         | E33              | P3-C14           | P3-B14              |

| CLOCK6         | E40              | GATE6         | E39              | P3-B19           | P3-A19              |

| CLOCK7         | E38              | GATE7         | E37              | P3-A22           | P3-C19              |

| CLOCK8         | E44              | GATE8         | E43              | P3-C22           | P3-B22              |

| CLOCK9         | E42              | GATE9         | E41              | P3-B27           | P3-A27              |

| CLOCK10        | E48              | GATE10        | E47              | P3-A30           | P3-C27              |

| CLOCK11        | E46              | GATE11        | E45              | P3-C30           | P3-B30              |

| CLOCK12        | E4               | GATE12        | E3               | P4-B3            | P4-A3               |

| CLOCK13        | E2               | GATE13        | E1               | P4-A6            | P4-C3               |

| CLOCK14        | E8               | GATE14        | E7               | P4-C6            | P4-B6               |

| CLOCK15        | E6               | GATE15        | E5               | P4-B11           | P4-A11              |

| CLOCK16        | E12              | GATE16        | E11              | P4-A14           | P4-C11              |

| CLOCK17        | E10              | GATE17        | E9               | P4-C14           | P4-B14              |

| CLOCK18        | E16              | GATE18        | E15              | P4-B19           | P4-A19              |

| CLOCK19        | E14              | GATE19        | E13              | P4-A22           | P4-C19              |

| CLOCK20        | E20              | GATE20        | E19              | P4-C22           | P4-B22              |

| CLOCK21        | E18              | GATE21        | E17              | P4-B27           | P4-A27              |

| CLOCK22        | E24              | GATE22        | E23              | P4-A30           | P4-C27              |

| CLOCK23        | E22              | GATE23        | E21              | P4-C30           | P4-B30              |

Table 2-7 TTL/Single-Ended Input Signal Compatibility Configuration

**NOTE:** \*Clock (CLK) or Gate input connections vary depending on the measurements to be performed. See Chapter 3 "Programming" for details.

Figure 2-5 Typical TTL-Compatible Signal Connections

**NOTE:** \*Clock (CLK) or Gate input connections vary depending on the measurements to be performed. See Chapter 3 "Programming" for details.

VMIVME-2540 Intelligent Counter/Controller

# Programming

# Contents

| VMEbus Interface Memory Map               | 51  |

|-------------------------------------------|-----|

| Command Interface                         | 60  |

| Command Status Codes                      | 63  |

| Modes of Operation                        | 64  |

| Format of the Operation Mode Select Flag: | 69  |

| Command Descriptions                      | 70  |

| Getting Started                           | 102 |

# Introduction

The user controls the operation of the VMIVME-2540 via the local CPU through a shared memory interface, which provides a command-driven system. The shared memory is a 64 Kbyte contiguous block of memory and is structured within the local CPU program to satisfy the definitions shown in Table 3-1 on page 51. This structure definition provides the command register, command status reporting, measurement interface, and I/O channel control blocks (CCBs) for the exchange of data between the local CPU and the user's host processor.

Input and output operations are initiated by writing the parameters for the operation to the desired CCB, selecting a channel via the channel select register (byte offset \$000A) and sending the associated command to the local CPU by writing the command to the command register (word at offset \$0004; byte offset at \$0005), and monitoring the command status buffer (word at offset \$0006; byte offset at \$0007).

The command word at offset \$0004 and the command status buffer at offset \$0006 have special attributes and handling properties for the local CPU and are the primary synchronization method for the VMEbus host program. When the VMEbus host writes a command word to offset \$0004 (or byte to offset \$0005) from the base address, an interrupt is generated for the VMIVME-2540 local CPU.

The VMIVME-2540 local CPU responds to the command interrupt by reading the command and channel ID locations, performs the commanded action defined by the command and the parameters in the CCB of the selected channel, and writes the command status code to the command status buffer. The command status buffer is a read-only register and cannot be cleared by writing a zero to the register. The command status register can be cleared by writing the clear command status command code (\$1C) to the command register, which will cause the local processor to clear the command status byte. The host should verify that this register is clear (zero) prior to initiating a command.

The VMEbus host can poll the command status buffer to wait for a nonzero response code, or the command status IRQ and command status vector locations can be initialized with a VMEbus IRQ level and vector, and host interrupt processing used for command status reporting.

The VMIVME-2540 performs a variety of the input and output operations under command control of the host processor. Input operations for signal measurement processes can be interrupt-driven, polled through the measurement queue interface, polled via the channel status buffer of the CCB, or polled via the channel's data validity flag.

Channels can also be set up to measure continuously through the continuous-discrete descriptor (offset \$000B from the base address). The VMEbus-shared memory addresses, command codes, command status codes, and channel control blocks entries will be discussed in the following sections.

# **VMEbus Interface Memory Map**

The memory map for the VMIVME-2540 resources, accessible by the VMEbus host is given in Table 3-1. The contents of the shared memory area are initialized to zero (0) at powerup/reset/initialization unless otherwise noted in the following descriptions.

**NOTE**: The following formats are presented in terms of the vmebus with byte accesses shown in terms of the data bus lines on which they are accessed; that is, odd bytes are accessed on bus data lines D0 through D7, and even bytes are accessed on data lines D8 through D15. All byte-width data, once moved to the internal registers of most host processors, will be bit-accessed using Bit 0 through Bit 7 for bit manipulation operations.

| Offset | Function                        | Access      | Size           |

|--------|---------------------------------|-------------|----------------|

| \$0000 | Board ID/Configuration          | *Read/Write | Word           |

| \$0002 | Firmware Revision Level         | *Read/Write | Word           |

| \$0004 | Command                         | Read/Write  | Word/Byte***   |

| \$0006 | Command Status                  | Read        | Word/Byte***   |

| \$0008 | Command Status IRQ Level        | Read/Write  | Byte           |

| \$0009 | Command Status Interrupt Vector | Read/Write  | Byte           |

| \$000A | Channel ID                      | Read/Write  | Byte           |

| \$000B | Continuous/Discrete Flag        | Read/Write  | Byte           |

| \$000C | Measurement Flag                | Read/Write  | Byte           |

| \$000E | Measurement Channel             | Read/Write  | Byte           |

| \$000F | Measurement Status              | Read/Write  | Byte           |

| \$0010 | Ch 0 Channel Control Block      | Read/Write  | **See CCB DESC |

| \$0020 | Ch 1 Channel Control Block      | Read/Write  | **See CCB DESC |

| \$0030 | Ch 2 Channel Control Block      | Read/Write  | **See CCB DESC |

| \$0040 | Ch 3 Channel Control Block      | Read/Write  | **See CCB DESC |

| \$0050 | Ch 4 Channel Control Block      | Read/Write  | **See CCB DESC |

| \$0060 | Ch 5 Channel Control Block      | Read/Write  | **See CCB DESC |

| \$0070 | Ch 6 Channel Control Block (1)  | Read/Write  | **See CCB DESC |

| \$0080 | Ch 7 Channel Control Block (1)  | Read/Write  | **See CCB DESC |

| \$0090 | Ch 8 Channel Control Block (2)  | Read/Write  | **See CCB DESC |

| \$00A0 | Ch 9 Channel Control Block (2)  | Read/Write  | **See CCB DESC |

| \$00B0 | Ch 10 Channel Control Block (2) | Read/Write  | **See CCB DESC |

| \$00C0 | Ch 11 Channel Control Block (2) | Read/Write  | **See CCB DESC |

| \$00D0 | Ch 12 Channel Control Block (2) | Read/Write  | **See CCB DESC |

| \$00E0 | Ch 13 Channel Control Block (2) | Read/Write  | **See CCB DESC |

| \$00F0 | Ch 14 Channel Control Block (2) | Read/Write  | **See CCB DESC |

| \$0100 | Ch 15 Channel Control Block (2) | Read/Write  | **See CCB DESC |

| \$0110 | Ch 16 Channel Control Block (3) | Read/Write  | **See CCB DESC |

| \$0120 | Ch 17 Channel Control Block (3) | Read/Write  | **See CCB DESC |

| \$0130 | Ch 18 Channel Control Block (3) | Read/Write  | **See CCB DESC |

| \$0140 | Ch 19 Channel Control Block (3) | Read/Write  | **See CCB DESC |

#### Table 3-1 VMIVME-2540 VMEbus I/F Addresses

| Offset        | Function                        | Access      | Size             |

|---------------|---------------------------------|-------------|------------------|

| \$0150        | Ch 20 Channel Control Block (3) | Read/Write  | **See CCB DESC   |

| \$0160        | Ch 21 Channel Control Block (3) | Read/Write  | **See CCB DESC   |

| \$0170        | Ch 22 Channel Control Block (3) | Read/Write  | **See CCB DESC   |

| \$0180        | Ch 23 Channel Control Block (3) | Read/Write  | **See CCB DESC   |

| \$0190        | Timer 0 Control Block           | Read/Write  | ***See TCCB DESC |

| \$01A0        | Timer 1 Control Block (1)       | Read/Write  | ***See TCCB DESC |

| \$01B0        | Timer 2 Control Block (2)       | Read/Write  | ***See TCCB DESC |

| \$01C0        | Timer 3 Control Block (2)       | Read/Write  | ***See TCCB DESC |

| \$01D0        | Timer 4 Control Block (3)       | Read/Write  | ***See TCCB DESC |

| \$01E0        | Timer 5 Control Block (3)       | Read/Write  | ***See TCCB DESC |

| \$01F0-\$0207 | Continuous-Discrete Flags       | *Read/Write | Byte             |

| \$0208-\$021F | Measurement Data Validity Flags | Read/Write  | Byte             |

| \$0220-\$03DF | Internal Flags/Reserved         | *Read/Write | Byte/Word/Long   |

| \$03E0-\$03FF | Firmware Release Information    | *Read/Write | Byte/Word/Long   |

| \$0400-\$3FFF | Diagnostic/Utility Buffer       | *Read/Write | Byte/Word/Long   |

| \$4000-\$FFFF | Scratch Pad/Reserved            | *Read/Write | Byte/Word/Long   |

Table 3-1 VMIVME-2540 VMEbus I/F Addresses (Continued)

**NOTE:** \* User should not write to this area: value initialized/used by local CPU.

\*\* CCB is the Channel Control Block described in the *Channel Control Block Registers* on page 57. \*\*\* TCCB is the Timer Channel Control Block described in the *Timer Channel Control Block* on page 57. (1) Usable on options 100, 200, and 300 only.

(2) Usable on options 200 and 300 only.

(3) Usable on option 300 only.

#### **Board ID/Configuration Buffer**

The ID/Configuration buffer (Table 3-2 below) contains the board ID at offset \$0000 and the board configuration at offset \$0001. The board ID is always \$25 for the VMIVME-2540, and the configuration byte is the number of 16-bit channels available on the board. The buffer is updated upon completion of powerup or front panel reset initialization and self-test, and should not by altered by the user. The ID buffer value corresponding to the VMIVME-2540 ordering options is given in Table 3-3 below. During reset initialization or self-test, the board ID location value is undefined.

| Bit 15 |                                     | Bit 0 |

|--------|-------------------------------------|-------|

|        | 16-bit Board ID/Configuration Value |       |

| Order Option | Configuration        | ID Buffer Value |

|--------------|----------------------|-----------------|

| -000         | Four Channels        | \$2500          |

| -100         | Eight Channels       | \$2501          |

| -200         | Sixteen Channels     | \$2502          |

| -300         | Twenty-Four Channels | \$2503          |

Table 3-3 VMIVME-2540 ID/Configuration Values

## **Firmware Revision Level**

The Firmware Revision Level code is a 4-digit hexadecimal value initialized at completion of self-test. The firmware revision code has *major* and *minor* levels formatted as bytes, that is, \$0118 is interpreted as version 1.24. During powerup or front panel reset initialization and self-test, the firmware revision code is undefined.