# VMIVME-3119 16-Channel, 16-bit Scanning Analog-to-Digital Board with Programmable Gain and Filter

**Product Manual**

12090 South Memorial Parkway Huntsville, Alabama 35803-3308, USA (256) 880-0444 • (800) 322-3616 • Fax: (256) 882-0859

500-003119-000 Rev.E

A GE Fanuc Company

© Copyright 2003. The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

AMXbus, BITMODULE, COSMODULE, DMAbus, IOMax, IOWorks Foundation, IOWorks Manager, IOWorks Server, MAGICWARE, MEGAMODULE, PLC ACCELERATOR (ACCELERATION), Quick Link, RTnet, Soft Logic Link, SRTbus, TESTCAL, "The Next Generation PLC", The PLC Connection, TURBOMODULE, UCLIO, UIOD, UPLC, Visual Soft Logic Control(ler), *VMEaccess*, VMEbus Access, *VMEmanager*, *VMEmonitor*, VMEnet, VMEnet II, and *VMEprobe* are trademarks and The I/O Experts, The I/O Systems Experts, The Soft Logic Experts, and The Total Solutions Provider are service marks of VMIC.

(I/O man figure)

(IOWorks man figure)

The I/O man figure, IOWorks, IOWorks man figure, UIOC, Visual IOWorks and the VMIC logo are registered trademarks of VMIC.

ActiveX, Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, Windows NT, and XENIX are registered trademarks of Microsoft Corporation.

Celeron and MMX are trademarked, Intel and Pentium are registered trademarks of Intel Corporation.

PICMG and CompactPCI are registered trademarks of PCI Industrial Computer Manufacturers' Group.

Other registered trademarks are the property of their respective owners.

# FCC STATEMENT

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy. If the equipment is not installed and used in accordance with the instruction manual, it may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

# **Table of Contents**

| List of Figures                                      | 10 |

|------------------------------------------------------|----|

| List of Tables                                       | 12 |

| Overview                                             | 14 |

| Features                                             | 14 |

| Functional Description                               | 15 |

| Overvoltage and Open Input Protection                | 15 |

| 48 kHz Passive Low Pass Filter                       | 15 |

| Input/BIT Switches                                   | 15 |

| Programmable Gain Amplifier                          | 15 |

| Active 4TH-Order Low Pass Filter                     | 17 |

| Channel Multiplexer (MUX)                            | 17 |

| 16-bit Analog-to-Digital Converter (ADC)             | 17 |

| Digital Signal Processor (DSP)                       | 17 |

| Data Buffer                                          | 17 |

| Control/Status Registers                             | 17 |

| Analog-to-Digital Converter (ADC) Timing and Control |    |

| VMEbus Foundation Logic                              |    |

| VMEbus Interrupter                                   |    |

| Reference Voltages                                   |    |

| DC-to-DC Converter                                   |    |

| Front Panel LED                                      |    |

| Reference Material List                              | 19 |

| Safety Summary                                       | 20 |

| Warnings, Cautions and Notes                         |    |

| Chapter 1 - Theory of Operation | 22 |

|---------------------------------|----|

| Configuration Jumpers           | 23 |

| VMEbus Base Address             | 23 |

| VMEbus Access Mode              | 23 |

| VMEbus Address Mode             | 23 |

| VMEbus Memory Size              | 23 |

| VMEbus Interrupt Level          | 24 |

| Self-Test Disable               | 24 |

| Analog Inputs                   | 25 |

| Control Parameters              | 26 |

| Data Ready                      | 26 |

| Data Format                     | 26 |

| Scan Modes                      | 26 |

| Trigger Mode                    | 32 |

| VMEbus Interrupt                | 32 |

| Sample Period                   | 32 |

| Channel Gain                    | 33 |

| Channel Filter Cutoff Frequency | 33 |

| Buffer Size                     | 33 |

| Status Parameters               | 34 |

| Configuration Complete Flag     | 34 |

| Data Ready Flag                 | 34 |

| Trigger Armed Status            | 34 |

| Scan Triggered Status           | 34 |

| Error Code Status               | 34 |

| VMEbus Interrupt Level Status   | 35 |

| Memory Size Status              | 35 |

| Self-Test Disable Status        | 35 |

| Commands                        | 36 |

| Clear Flag Command              | 36 |

| Abort/Restart Scan Command      | 36 |

| Software Trigger Command        | 36 |

| Channel Calibration Command     | 36 |

| Self-Test Command               | 36 |

| Reset Command                   | 36 |

| Scan Table                      | 37 |

| Sample Buffer RAM               | 38 |

| User-Defined RAM                | 39 |

| External Triggers                                | 0 |

|--------------------------------------------------|---|

| Calibration Coefficients                         | 1 |

| Front Panel LED                                  | 2 |

| Reference Output and Control Switches43          | 3 |

| Chapter 2 - Configuration and Installation       | 6 |

| Unpacking Procedures                             | 7 |

| Physical Installation                            |   |

| Before Applying Power: Checklist                 |   |

| Base Address and Board Configuration             | 9 |

| System Connections                               | 5 |

| Chapter 3 - Programming                          | 0 |

| VMEbus Slave Interface                           | 1 |

| VMIVME-3119 Memory Map62                         | 2 |

| Board ID Register (BID)64                        | 4 |

| Firmware Revision Register (FRR)                 |   |

| Global Control Register (GCR)66                  | 6 |

| Global Status Register (GSR)68                   |   |

| Sample Clock Prescale Register (PSR)             | 0 |

| Sample Clock Period Register (SPR)7              |   |

| IRQ Control Register (ICR)                       | 2 |

| IRQ Status Register (ISR)                        | 3 |

| Low Channel Gain Register (LGR)74                | 4 |

| High Channel Gain Register (HGR)                 | 5 |

| Low Channel Filter Register (LFR)70              | 6 |

| High Channel Filter Register (HFR)77             | 7 |

| Buffer Size Register (BSR)                       | 8 |

| Clear Flag Command Register (CFR)79              | 9 |

| Calibration Channel Select Register (CSR)80      |   |

| Calibration Configuration Select Register (CCR)8 | 1 |

| Reset Command Register (RST)82                   | 2 |

| Calibration Command Register (CAL)83             | 3 |

| Self-Test Command Register (STC)84               | 4 |

| Self-Test Status Register (TSR)                  |   |

| Software Trigger Command Register (TRG)86        | 6 |

| Abort/Restart Scan Command Register (ABT)8       | 7 |

| DSP Peek Address Register (PAR)88                | 8 |

| DSP Peek Data Register (PDR)                     | 9 |

VMIVME-3119 16-Channel, 16-bit Scanning Analog-to-Digital Board with Programmable Gain and Filter

| LED Control Register (LCR)                                     | 90 |

|----------------------------------------------------------------|----|

| Reference Calibration Mode Register (RCM)                      | 91 |

| Reference Calibration Code Register (RCC)                      | 92 |

| Reference Calibration Status Register (RCS)                    | 93 |

| Reference Calibration Enable HW and LW Registers (REH and REL) | 94 |

| Scan Table (SCN)                                               | 95 |

| User Calibration Coefficients                                  | 96 |

| Example:                                                       | 98 |

| Sample Buffer (SPL)                                            | 00 |

| Maintenance1                                                   | 02 |

| Maintenance                                                    | 02 |

| Maintenance Prints                                             | 03 |

# List of Figures

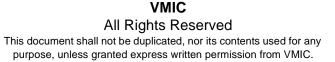

| Figure 1   | VMIVME-3119 Block Diagram              | 16 |

|------------|----------------------------------------|----|

| Figure 1-1 | Data Ready Operational Flowchart       | 27 |

| Figure 1-2 | Continuous Scan Mode Flowchart         | 28 |

| Figure 1-3 | Single Scan Mode Flowchart             | 29 |

| Figure 1-4 | Single Scan and Rearm Flowchart        | 30 |

| Figure 1-5 | Advance Scan on Trigger Flowchart      | 31 |

| Figure 2-1 | VMIVME-3119 Board Layout               | 50 |

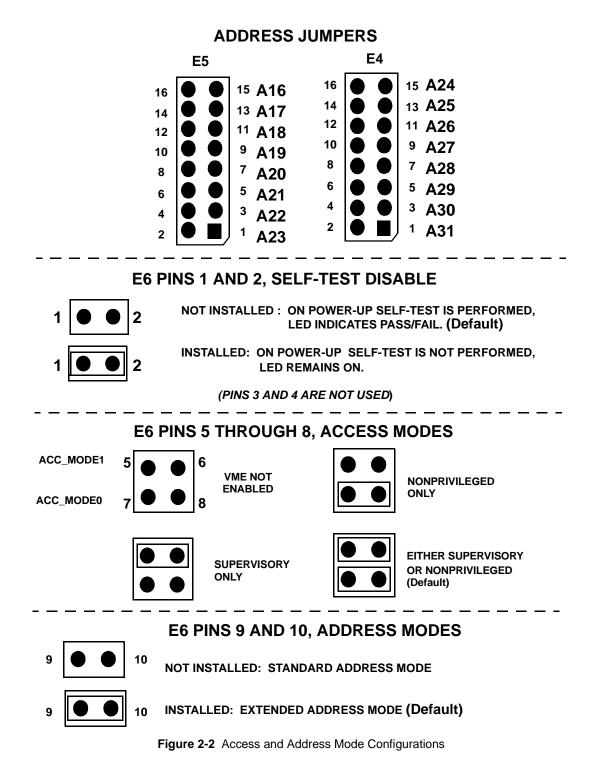

| Figure 2-2 | Access and Address Mode Configurations | 51 |

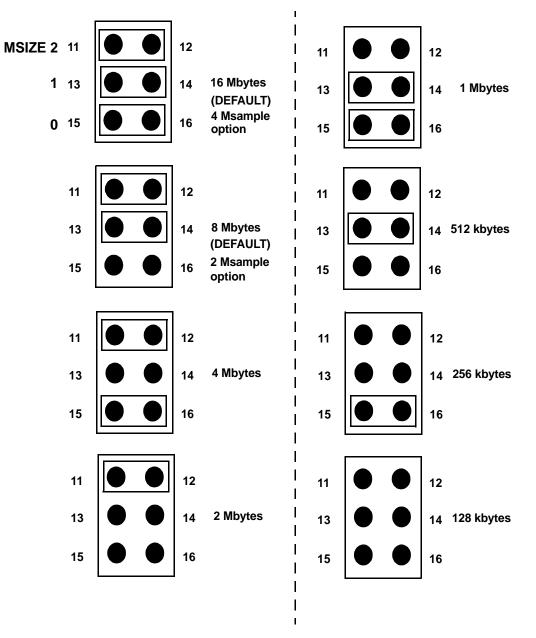

| Figure 2-3 | Memory Size Configurations             | 52 |

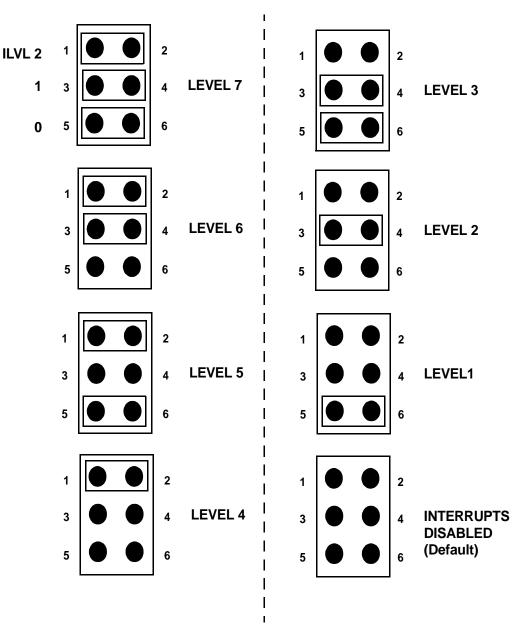

| Figure 2-4 | Jumper E7 Interrupts Configuration     | 53 |

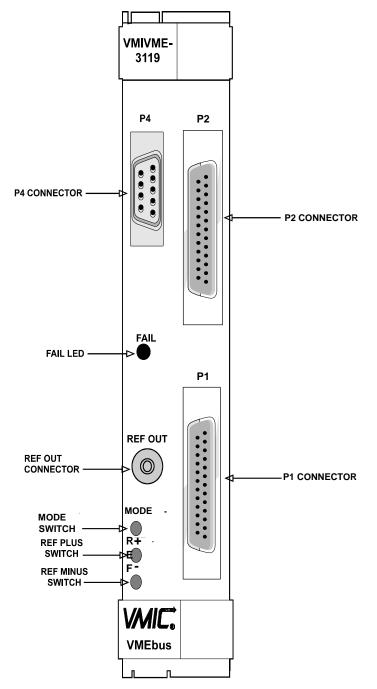

| Figure 2-5 | Front Panel for the VMIVME-3119        | 56 |

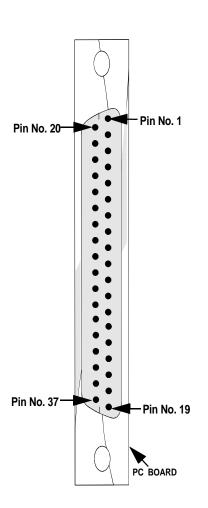

| Figure 2-6 | P7 and P8 Connector                    | 57 |

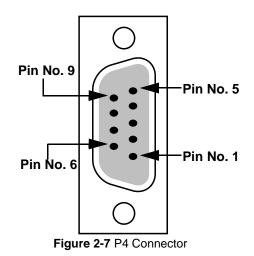

| Figure 2-7 | P4 Connector                           | 58 |

VMIVME-3119 16-Channel, 16-bit Scanning Analog-to-Digital Board with Programmable Gain and Filter

# List of Tables

| Calibration Reference Voltages.                          | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P7 Connector Pinout                                      | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P8 Connector Pinout                                      | . 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VMIVME-3119 Memory Map                                   | . 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Board ID Register Bit Map                                | . 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Filter Options                                           | . 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Firmware Revision Register Bit Map                       | . 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Global Control Register Bit Map                          | . 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Scan Modes (SM[2:0])                                     | . 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Trigger Modes                                            | . 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Global Status Register Bit Map                           | . 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Error Codes (ERR[3:0]).                                  | . 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Sample Clock Prescale Register Bit Map                   | . 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Sample Clock Period Register Bit Map                     | . 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IRQ Control Register Bit Map                             | . 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IRQ Status Register Bit Map                              | . 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IRQ Status Interrupt Level [2:0]                         | . 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Low Channel Gain Register Bit Map                        | . 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Low Channel Gain Bit Definitions (CHx G[1:0])            | . 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| High Channel Gain Register Bit Map                       | . 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| High Channel Gain Bit Definitions (CHx G[1:0])           | . 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Low Channel Filter Register Bit Map                      | . 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Low Channel Filter Register Bit Definitions (CHx G[1:0]) | . 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| High Channel Filter Register Bit Definitions             | . 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| High Channel Filter Register Bit Definitions             | . 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Buffer Size Register Bit Map                             | . 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Buffer Size Register Bit Definitions (BS[4:0])           | . 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                          | Calibration Reference Voltages.<br>P7 Connector Pinout.<br>P8 Connector Pinout.<br>VMIVME-3119 Memory Map.<br>Board ID Register Bit Map.<br>Filter Options<br>Firmware Revision Register Bit Map.<br>Global Control Register Bit Map.<br>Scan Modes (SM[2:0]).<br>Trigger Modes.<br>Global Status Register Bit Map.<br>Error Codes (ERR[3:0]).<br>Sample Clock Prescale Register Bit Map.<br>Sample Clock Prescale Register Bit Map.<br>IRQ Control Register Bit Map.<br>IRQ Control Register Bit Map.<br>IRQ Status Register Bit Map.<br>IRQ Status Interrupt Level [2:0].<br>Low Channel Gain Register Bit Map.<br>High Channel Gain Register Bit Map.<br>High Channel Gain Bit Definitions (CHx G[1:0]).<br>High Channel Filter Register Bit Map.<br>Low Channel Filter Register Bit Definitions.<br>High Channel Filter Register Bit Definitions.<br>Buffer Size Register Bit Map.<br>Buffer Size Register Bit Map. |

| Table 3-25 | Clear Flag Command Register Bit Map79                                                      |

|------------|--------------------------------------------------------------------------------------------|

| Table 3-26 | Calibration Channel Select Register Bit Map80                                              |

| Table 3-27 | Calibration Configuration Select Register Bit Map81                                        |

| Table 3-28 | Reset Command Register Bit Map                                                             |

| Table 3-29 | Calibration Command Register Bit Map83                                                     |

| Table 3-30 | Self-Test Command Register Bit Map                                                         |

| Table 3-31 | Self-Test Status Register Bit Map85                                                        |

| Table 3-32 | Software Trigger Command Register Bit Map86                                                |

| Table 3-33 | Abort/Restart Scan Command Register Bit Map87                                              |

| Table 3-34 | DSP Peek Address Register Bit Map                                                          |

| Table 3-35 | DSP Peek Data Register Bit Map                                                             |

| Table 3-36 | LED Control Register Bit Map90                                                             |

| Table 3-37 | Reference Calibration Mode Register Bit Map91                                              |

| Table 3-38 | Reference Calibration Code Register Bit Map92                                              |

| Table 3-39 | Reference Calibration Status Register Bit Map93                                            |

| Table 3-40 | Reference Calibration Enable HW and LW Registers, Bit Map94                                |

| Table 3-41 | Scan Table                                                                                 |

| Table 3-42 | Scan Table Bit Map                                                                         |

| Table 3-43 | User Calibration Coefficients                                                              |

| Table 3-44 | User Gain Coefficient                                                                      |

| Table 3-45 | User Offset Coefficient                                                                    |

| Table 3-46 | Sample Buffer Register Map                                                                 |

| Table 3-47 | Sample Buffer Bit Map                                                                      |

| Table 3-48 | Example: Bipolar Input Voltages and Data Representation (Two's Complement Data Format) 100 |

| Table 3-49 | Example: Bipolar Input Voltages and Data Representation (Offset Binary Data Format) 100    |

# **Overview**

# Introduction

The VMIVME-3119 Analog Input board provides 16 high accuracy differential analog input channels with high throughput 16-bit Analog-to-Digital conversion. Each input is equipped with a dedicated Programmable Gain Amplifier (PGA), software-selectable fourth-order low pass filter, and autocalibration.

## Features

The VMIVME-3119 has many unique features as listed below:

- · Sixteen differential analog input channels

- Software programmable gain per channel (x1, x10, x100, and x1,000)

- Input signal range from  $\pm 10 \text{ mV}$  to  $\pm 10 \text{ V}$

- Software programmable fourth-order low pass filter (1 Hz, 10 Hz, 10 Hz, 1 kHz) factory option of Bessel or Butterworth response

- Autocalibration per channel utilizing DSP technology

- 16-bit Analog-to-Digital conversion; high accuracy

- Software programmable sample rate from 305 Hz to 100 kHz aggregate, even lower rates can be obtained using prescaler

- Software programmable scan table

- · Large data buffer retains up to four million data samples

- Overvoltage input protection

- Flexible triggering: internal, external, or multiboard synchronous

- VMEbus interrupts at mid scan or end scan

- Two-slot VMEbus configuration

- UIOC<sup>®</sup> capability

- Self-test

- Extensive on-board diagnostic testing capability

- Implements precision internal reference voltages

- Independent of field connections

# **Functional Description**

The VMIVME-3119 has on-board autocalibration correction for offset and gain errors in real-time. Calibration correction values are determined at user-controlled calibration intervals without removing the board from the system. Individual channel correction is accomplished by DSP technology in real-time for every A/D conversion. Calibration can be verified at any time by implementing the self-test feature. Self-test uses internal precision voltages, which are applied to all channels simultaneously to verify signal path integrity.

The VMIVME-3119 can be jumper configured for either standard or extended address space, and can be jumper configured to occupy 16, 8, 4, 2, and 1 Mbyte, also 512, 256, or 128 Kbyte of address space.

The VMIVME-3119 has a software configurable sample buffer which begins at the base address of the Data RAM (address P, as shown in Table 3-1 on page 62). The size of the sample buffer determines the number of samples to be stored per scan. A user-configurable scan table determines which channels are scanned and in what order they are scanned. The sample buffer size can be configured in any power-of-2 from 1 sample to 4 Megasamples.

A functional block diagram is provided in Figure 1 on page 16.

#### **Overvoltage and Open Input Protection**

The input filter resistors provides for current limiting in the event of an overvoltage. The inputs are protected up to  $\pm 40$  V sustained.

Each input LO side has a 22 M $\Omega$  resistor connected to ground. This resistor pulls an open or floating LO side to ground to keep the channel from saturating and causing crosstalk effects on adjacent channels. The HI side **does not** have a pull-down resistor. Care should be exercised in making sure this line is connected to a source or ground.

#### 48 kHz Passive Low Pass Filter

Each input has a passive single-pole RC filter with a cut off frequency of 48 kHz. This filter is intended to limit input noise and bandwidth.

#### Input/BIT Switches

The field inputs and the Built-in-Test (BIT) voltages go through an analog switch. A control signal on the switch determines if the output of the switch will be the field inputs or the BIT voltages. The switch makes it possible to do BIT and calibration without having to remove the field connections. Also, the BIT voltages follow the same path as the field inputs right at the front panel connector ensuring any component error in the signal path will be corrected. The output of this switch drives the Programmable Gain Amplifier.

#### **Programmable Gain Amplifier**

The Programmable Gain Amplifier (PGA) provides differential to signal-ended conversion, common-mode rejection, and selectable gains of 1, 10, 100, and 1,000. The gain is user programmable. The output of the PGA drives the active filter.

Figure 1 VMIVME-3119 Block Diagram

## **Active 4TH-Order Low Pass Filter**

A four-pole selectable cut off active filter eliminates noise and frequencies which are undesired. The selectable cut off frequencies are 1 Hz, 10 Hz, 100 Hz, and 1 kHz. Each cut off frequency is available and is user programmable. The filter response is a factory option of either Butterworth or Bessel. The output of the filter for each channel is multiplexed to the Analog-to-Digital Converter (ADC).

## **Channel Multiplexer (MUX)**

The VMIVME-3119 is a multiplexed scanning board. There are two multiplexers for all 16 channels, each one supporting 8 channels. The appropriate logic enables each multiplexer to output a specific channel in the correct sequence.

## 16-bit Analog-to-Digital Converter (ADC)

The VMIVME-3119 utilizes a 100 KS/s switched capacitor/charge redistribution 16-bit ADC with an on-chip sample-hold. The converted data is transmitted serially to the DSP. The DSP is interrupted when the data transmission is complete.

# **Digital Signal Processor (DSP)**

The DSP serves four primary functions which are command interpretation, calibration, self-test, and real-time data correction. Upon user command, the DSP can perform calibration of each channel in all possible configurations. These calibration coefficients are stored in EEPROM. When a scan is active, the DSP receives samples from the 16-bit ADC and applies gain and offset correction before storing these samples in the Sample Buffer. The DSP continually monitors the Control/Status Registers for any change in configuration and configures the hardware for the desired mode of operation.

#### **Data Buffer**

The Data Buffer is an 8 Mbyte DRAM (or 4 Mbyte depending on ordering option) which can hold up to 4 million corrected samples. VMEbus block transfers (BLTs) are an efficient way of reading large numbers of samples from this buffer. This RAM can be allocated by setting the buffer size parameter, as either Sample Buffer RAM or user-defined RAM.

# **Control/Status Registers**

The Control/Status Registers are implemented using a 32 Kbyte SRAM. This memory contains all control and status registers, provides a 256-byte scan table, and allows user access to calibration coefficients.

NOTE: Do not use blt operations to access these SRAM-based registers.

# Analog-to-Digital Converter (ADC) Timing and Control

The ADC sample rate is user selectable (100 KHz maximum). The DSP internal timer is used for this sample clock and each time this timer expires an ADC sample pulse is issued. The ADC Timing and Control circuit issues an interrupt to the DSP when the ADC input has been sampled. This causes the DSP to advance the Channel MUX to the next channel to be sampled.

# **VMEbus Foundation Logic**

The VMEbus interface is implemented using the Cypress CY7C960 and four CYCC964s. A local bus arbiter directs traffic to and from the Control/Status Register and the Data Buffer. To prevent loss of data, the priority is from the highest to the lowest, DRAM refresh, DSP (data samples), and VMEbus.

## **VMEbus Interrupter**

An interrupt can be issued on any level (jumper selectable) and a single byte vector will be placed on the VMEbus when acknowledged. There is one Release-On-Acknowledge (ROAK) interrupt for the board and it can be generated when the data buffer is 50 percent (Mid Scan) or 100 present (End Scan) filled.

# **Reference Voltages**

All calibration and self-test functions of the VMIVME-3119 are based on several precision reference voltages which can be user calibrated using the three front panel push button switches or using the Control/Status Registers. These voltages are output from a precision DAC under control of the DSP. When the Reference Voltages are calibrated, the DSP calculates gain and offset coefficients for each of the voltage ranges.

# **DC-to-DC Converter**

There are three DC-to-DC converters on the VMIVME-3119 (two on the daughter board and one on the motherboard). Each of these is powered from the VMEbus +5 V supply. Each converter is fused to protect the circuitry it powers.

# **Front Panel LED**

The front panel LED serves two purposes. First, the LED is used to indicate the progression of certain DSP operations such as self-test and at the end of these operations indicates pass/fail by the state of this LED. Second, the user has access to control this LED for any user-defined function. At the completion of self-test the front panel LED will begin to blink in a continuing pattern of three blinks and then cuts off. This indicates that reference calibration has begun.

VMIVME-3119 16-Channel, 16-bit Scanning Analog-to-Digital Board with Programmable Gain and Filter

# **Reference Material List**

For a detailed explanation of the VMEbus and its characteristics, refer to "The VMEbus Specification" available from:

VITA

VMEbus International Trade Association

7825 East Gelding Drive, No. 104

Scottsdale, Arizona 85260

(602) 951-8866

FAX: (602) 951-0720

www.vita.com

Physical Description and Specifications: Refer to Product Specification, 800-003119-000 available from:

VMIC

12090 South Memorial Pkwy.

Huntsville, AL 35803-3308, USA

(256) 880-0444

(800) 322-3616

Fax: (256) 882-0859

www.vmic.com

# Safety Summary

The following general safety precautions must be observed during all phases of the operation, service and repair of this product. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture and intended use of this product.

VMIC assumes no liability for the customer's failure to comply with these requirements.

## Ground the System

To minimize shock hazard, the chassis and system cabinet must be connected to an electrical ground. A three-conductor AC power cable should be used. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet.

## Do Not Operate in an Explosive Atmosphere

Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.

#### Keep Away from Live Circuits

Operating personnel must not remove product covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### Do Not Service or Adjust Alone

Do not attempt internal service or adjustment unless another person capable of rendering first aid and resuscitation is present.

#### Do Not Substitute Parts or Modify System

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to VMIC for service and repair to ensure that safety features are maintained.

#### **Dangerous Procedure Warnings**

Warnings, such as the example below, precede only potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

**WARNING:** Dangerous voltages, capable of causing death, are present in this system. Use extreme caution when handling, testing and adjusting.

# Warnings, Cautions and Notes

**STOP** informs the operator that a practice or procedure should not be performed. Actions could result in injury or death to personnel, or could result in damage to or destruction of part or all of the system.

**WARNING** denotes a hazard. It calls attention to a procedure, practice or condition, which, if not correctly performed or adhered to, could result in injury or death to personnel.

**CAUTION** denotes a hazard. It calls attention to an operating procedure, practice or condition, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the system.

**NOTE** denotes important information. It calls attention to a procedure, practice or condition which is essential to highlight.

# **Theory of Operation**

# Contents

| Configuration Jumpers                       |  |

|---------------------------------------------|--|

| Analog Inputs                               |  |

| Control Parameters                          |  |

| Status Parameters                           |  |

| Commands                                    |  |

| Scan Table                                  |  |

| Sample Buffer RAM 38                        |  |

| User-Defined RAM 39                         |  |

| External Triggers                           |  |

| Calibration Coefficients 41                 |  |

| Front Panel LED                             |  |

| Reference Output and Control Switches    43 |  |

|                                             |  |

# Introduction

This section describes the operational modes of the VMIVME-3119 board, and describes in terms of the user interface how these operational modes are achieved. The user interface to the VMIVME-3119 can be described by the following and are addressed in this order:

- 1. Configuration Jumpers

- 2. Analog Inputs

- 3. Control Parameters

- 4. Status Parameters

- 5. Commands

- 6. Scan Table

- 7. Sample Buffer RAM

- 8. User-Defined RAM

- 9. External Triggers

- 10. Calibration Coefficients

- 11. Front Panel LED

- 12. Reference Voltage Output

# **Configuration Jumpers**

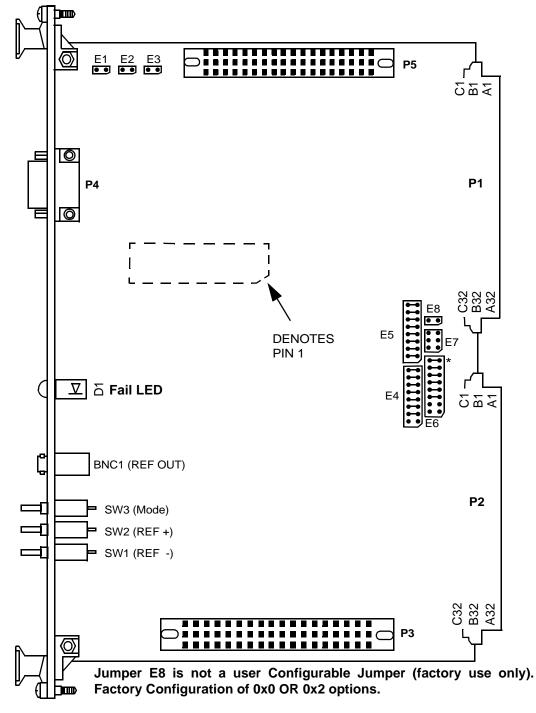

The configuration jumpers are one of the first things that must be considered when installing a VMIVME-3119. The configuration jumpers are discussed in detail in Chapter 2. However, since they are such an important part of the user interface, their use is summarized here.

#### VMEbus Base Address

Jumpers E4 and E5 determine the base address of the VMIVME-3119. The installation of a jumper causes the associated VMEbus address bit to be compared to a logical "0." Omitting the jumper causes a comparison to a logical "1." For the extended address mode, both E4 and E5 must be configured. For the standard address mode only E5 needs be configured.

#### VMEbus Access Mode

Jumper E6 allows the user to configure the VMIVME-3119 to respond to VMEbus Extended Data Accesses or Standard Data Accesses.

#### VMEbus Address Mode

Jumper E6 allows the user to configure the VMIVME-3119 to respond to Nonprivileged Data Access or Supervisory Data Accesses.

#### VMEbus Memory Size

The VMEbus address space occupied by the VMIVME-3119 can be user configured depending upon the application. The address space can be configured using jumper E6 as follows:

- 128 kbytes

- 256 kbytes

- 512 kbytes

- 1 Mbyte

- 2 Mbytes

- 4 Mbytes

- 8 Mbytes

- 16 Mbytes

The lower half of the VMEbus address space is occupied by Configuration, Status, and Command registers, the Scan Table, user-accessible calibration coefficients, and some reserved memory. The upper half of the VMEbus address space is occupied by the Sample Buffer RAM and User-Defined RAM. The size of the Sample Buffer RAM is set by the Buffer Size parameter. The amount of user-defined memory available is:

Size of user-defined memory = 1/2 (VMEbus Memory Size) - Sample Buffer RAM

# **VMEbus Interrupt Level**

The VMIVME-3119 can be configured to request a VMEbus interrupt at the mid point of an scan or at the end of an active scan. The desired interrupt level is configured by jumper E7.

# Self-Test Disable

Jumper field E6 contains a jumper that when installed causes the VMIVME-3119 to not perform self-test on power up or VMEbus reset. When this jumper is installed the front panel LED will remain on after power up or reset indicating to the user that self-test has not been performed. In most systems this jumper will never be installed.

# **Analog Inputs**

The VMIVME-3119 accepts either 8 or 16 analog inputs through two front panel DB37 male connectors. These inputs can be either differential or single-ended. In addition, each input has a guard pin tied to analog ground through a 470  $\Omega$  resistor.

Each input has a passive RC filter with a cut off frequency of, 34 kHz to limit the input bandwidth and reduce input noise. The resistors for the filter also act as current limiters to the input switch in ease of overvoltage. Each input Low side has a 22 M $\Omega$  resistor to ground to stop the channel from saturating, if the Low side cabling gets disconnected.

The input switch allows either the input signal or a Built-in-Test (BIT) signal to be digitized by the ADC. The switch is automatically set into the BIT position for calibration and self-test. In the BIT position, a precision reference section generates the required voltages for calibration and self-test.

A software programmable gain amplifier (PGA) provides the required gain to fully realize each range. The appropriate gain is applied by the board logic corresponding to the range selected by the user in the Low and High Channel Gain registers. This PGA also converts differential inputs to single-ended and provides common-mode rejection.

The output of the PGA is routed to the input of the active filter. This filter is a four-pole active low pass. The available filter responses are Butterworth and Bessel.

Each channel has its own components mentioned above. The range and filter frequency are individually programmable. The output of each filter is routed to a multiplexer, which allows one channel through at a time to be digitized by the ADC. The timing for the multiplexer is handled by the board logic.

If the input range is exceeded, the output data will read either full-scale positive or negative, depending on the polarity of the input signal.

Careful consideration should be placed on the cabling from the field to the inputs to get optimum results. Ribbon cable is suitable for high-level signals, but will cause signal degradation of low level signals. Twisted-shielded pair is recommended for the ranges below  $\pm 10$  volts.

# **Control Parameters**

The following control parameters, which are described further in Chapter 3, allow the user to control the operational modes of the VMIVME-3119.

# **Data Ready**

This parameter determines if the Data Ready Flag or VMEbus interrupt (if enabled), is generated at the midpoint of an active scan or at the end of an active scan.

# **Data Format**

This parameter determines the data format for the Sample Data RAM. Both two's complement and offset binary data formats are supported.

# **Scan Modes**

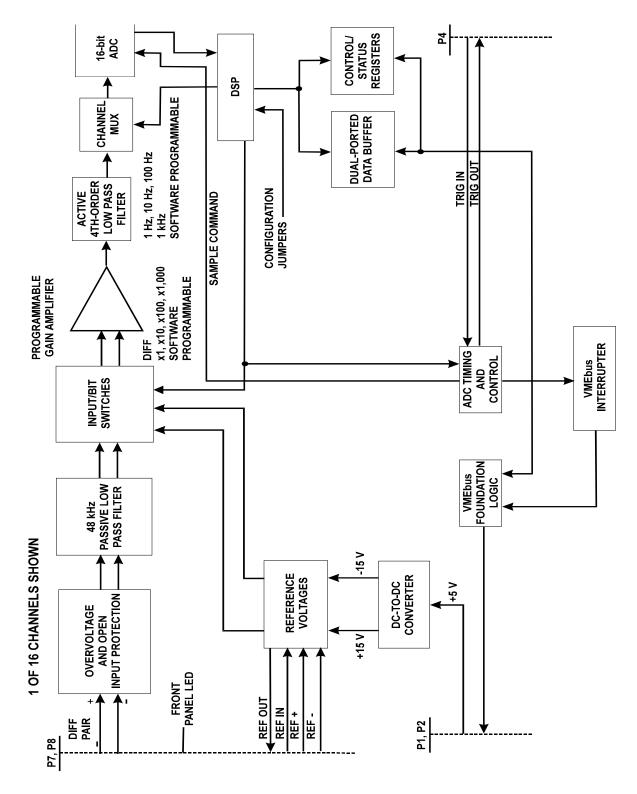

There are four scan modes supported by the VMIVME-3119. The operation of the Data Ready Flag and interrupt is the same in all scan modes and can be described by the flowchart (Figure 1-1 on page 27).

Figure 1-1 Data Ready Operational Flowchart

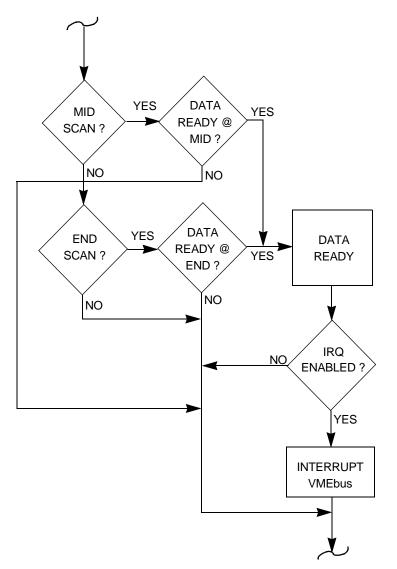

In the Continuous Scan Mode, each selected channel is continuously sampled at the effective sample rate. When the end of the Sample Data RAM is reached, the scan is automatically retriggered. This operation is described by the following flowchart.

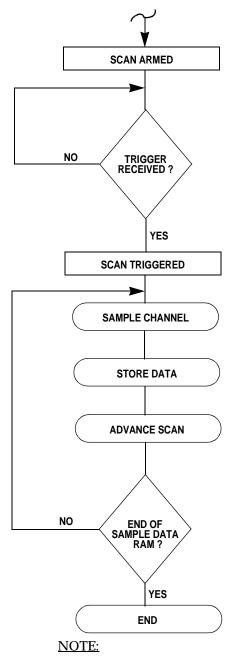

Figure 1-2 Continuous Scan Mode Flowchart

In the Single Scan Mode, a trigger event causes each selected channel to be sampled at the effective sample rate. When the end of the Sample Data RAM is reached, the scan is terminated. This mode, which cannot be retriggered, can be used to mask an unwanted external trigger. This mode is rearmed by the Abort/Restart Scan command. The Single Scan mode is described by the flowchart on page 3-6.

SINGLE SCAN MODE WILL NOT BE REARMED UNTIL AN ABORT/RESTART SCAN COMMAND IS RECEIVED.

Figure 1-3 Single Scan Mode Flowchart

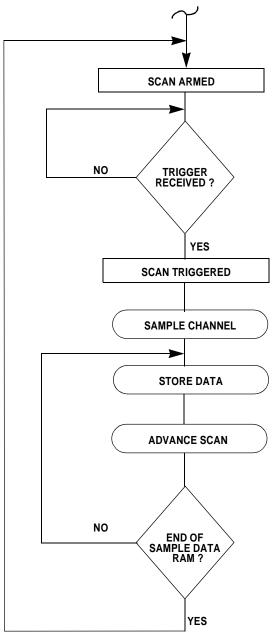

The Single Scan and Rearm Mode is much like the Single Scan mode except that when the end of the Sample Data RAM is reached, the scan is rearmed. This mode is described by the following flowchart:

Figure 1-4 Single Scan and Rearm Flowchart

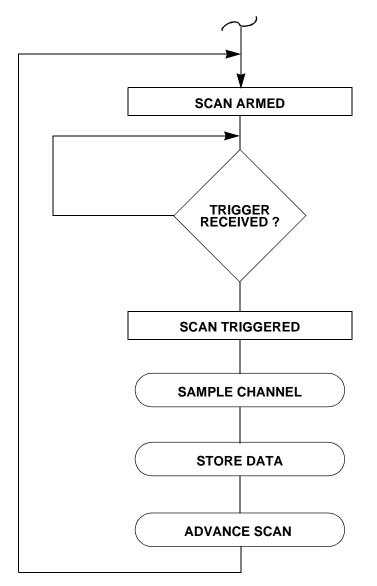

In the Advance Scan on Trigger Mode, the scan is advanced to the next selected channel each time a trigger occurs. This mode is described by the following flowchart:

Figure 1-5 Advance Scan on Trigger Flowchart

## **Trigger Mode**

There are six supported trigger modes for the VMIVME-3119. The operation of the Continuous Scan Mode is not affected by the Trigger Mode, however, all other scan modes require one or more trigger events.

When the Trigger Mode is disabled, no trigger events can occur.

The Single-Board Software Trigger Mode allows the VMIVME-3119, when armed, to be triggered by a Software Trigger Command.

The Single-Board Single-Ended External Trigger Mode allows the VMIVME-3119, when armed, to be triggered by a TTL-level high-to-low transition on Pin 8 (EXT\_TRIG\_L) of P4.

In the Multiboard Master Software Trigger Mode, a Software Trigger Command causes the configured scan mode, when armed, to be triggered and a differential trigger is output on Pins 5 and 9 of P4.

In the Multiboard Master External Trigger Mode, a TTL-level high-to-low transition on EXT\_TRIG\_L causes the configured scan mode, when armed, to be triggered and a differential trigger is output on Pins 5 and 9 of P4.

In the Multiboard Slave Differential Trigger Mode, a differential trigger received from the Master VMIVME-3119 on Pins 5 and 9 of P4 causes the configured scan mode, when armed, to be triggered.

#### VMEbus Interrupt

Before a VMEbus Interrupt can be used to indicate Data Ready, the Desired IRQ Vector must be programmed in the IRQ Vector Register. This register also contains an enable which can be used to enable or disable the interrupt request on a Data Ready condition.

#### **Sample Period**

The period of the sample clock is programmed through two registers, the Sample Clock Prescale Register and the Sample Clock Period Register.

Sample Period = (Sample Clock Period + 1) x (Sample Clock Prescale + 1) x (50 nsec)

The VMIVME-3119 has one ADC which is shared among all active channels, therefore, the sample period for an individual channel is not necessarily the programmed Sample Period. The Effective Sample Period depends on the programmed Sample Period and the number of channels being scanned.

Consider, as an example, that the following Scan Table is active {x00, x01, x00, x02, x00, x03, x00, x84}.

Effective Sample Period (Channel 0) = Sample Period x (8 / 4) = Sample Period x 2

Effective Sample Period (Channels 1, 2, 3, 4) = Sample Period x ( 8 / 1 ) = Sample Period x 8

# **Channel Gain**

The VMIVME-3119 supports input ranges of  $\pm 10$  V,  $\pm 1$  V,  $\pm 100$  mV, and  $\pm 10$  mV. The Low Channel Gain Register and High Channel Gain Register are used to program each channel of the VMIVME-3119 to the desired input range.

# **Channel Filter Cutoff Frequency**

A VMIVME-3119 with either the Bessel filter option or the Butterworth filter option can be programmed for filter cut-off frequencies of 1 KHz, 100 Hz, 10 Hz, and 1 Hz. The Low Channel Filter Register and High Channel Filter Register are used to program each channel of the VMIVME-3119 to the desired input range.

# **Buffer Size**

The Buffer Size parameter determines the size of the Sample Buffer RAM. The Buffer Size can be programmed, in powers of 2, from 1 sample (2 byte) to 4 Msamples (4,194,304 samples or 8,388,608 bytes) but cannot be more than 1/2 the VMEbus Memory Size set by Jumper Field E6.

# **Status Parameters**

The following status parameters, which are described further in Chapter 3, allow the user to determine the current state of the VMIVME-3119.

#### **Configuration Complete Flag**

The Configuration Complete Flag can be used as a handshake between the user and the on-board DSP. When the DSP detects a change in a control parameter, the scan is aborted and reconfigured. When this reconfiguration is complete, the Configuration Complete Flag is set. This flag is cleared by the Clear Flag Command or by the Abort/Restart Scan Command.

The following programming sequence for changing the configuration of the VMIVME-3119 is highly recommended.

Write all desired Control Parameters. Write Abort/Restart Scan Command. Read Abort/Restart Scan Command until equal 0. Read Configuration Complete Flag until equal 1.

#### Data Ready Flag

The Data Ready Flag indicates to the user that the Sample corresponding to the mid point or end point of the active scan has been written to the Sample Buffer RAM. If a VMEbus interrupt request is enabled, it will be generated when this flag is set. This Flag is cleared by the Clear Flag Command or the Abort/Restart Scan Command.

#### **Trigger Armed Status**

This status bit is set to a logical 1 whenever a scan is armed and ready for triggering. This status bit will be set to a logical 0 whenever a valid trigger is received.

#### Scan Triggered Status

This status bit is set to a logical 1 whenever a valid trigger is received. This bit is set to a logical 0 when the programmed scan ends, when the DSP detected a change in configuration, or when the Abort/Restart Scan Command is received.

#### **Error Code Status**

The Error Code Status is used to indicate invalid user-programmed control parameters and self-test failures. If the Channel Failure error code is returned, any channels that have failed self-test are indicated in the Self-Test Status Register. The Error Code Status is cleared when all error conditions are resolved.

VMIVME-3119 16-Channel, 16-bit Scanning Analog-to-Digital Board with Programmable Gain and Filter

# **VMEbus Interrupt Level Status**

There are three status bits that indicate to the user the state of the Interrupt Level configuration jumpers.

## **Memory Size Status**

There are three status bits that indicate to the user the state of the Memory Size configuration jumpers.

# Self-Test Disable Status

This Status Bit indicates to the user the state of the Self-Test Disable configuration jumper.

# Commands

Each of the commands is described in detail in Chapter 3. Each command is issued by writing a logical 1 to bit 0 of the associated register. The DSP acknowledges the command by returning this bit to a logical 0.

# **Clear Flag Command**

This command allows the user to clear the Configuration Complete and Data Ready Flags.

## **Abort/Restart Scan Command**

Although the DSP monitors command parameters and changes configuration when new user parameters are detected, it is recommended that the Abort/Restart Scan Command be used as a handshake between the user and the DSP. When the Abort/Restart Scan Command is issued, the Configuration Complete Flag indicates to the user that all programmed configuration changes have been completed.

## Software Trigger Command

This command allows the user to trigger a scan under software control. The Trigger Armed Status indicates that the VMIVME-3119 is ready to be triggered. The Scan Triggered Status indicates that the trigger has been received and the scan is in progress.

# **Channel Calibration Command**

This command, in conjunction with the Calibration Channel Select Register and the Calibration Configuration Select Register, allows the user to calibrate any group of channels in all possible range and filter configurations. It should be noted that the time required to calibrate the VMIVME-3119 will depend on the number of channels and filters selected. The calibration coefficients are stored in nonvolatile EEPROM.

# Self-Test Command

This command allows the user to initiate self-test of the VMIVME-3119. Pass/Fail of user-initiated self-test is indicated in the Error Code Register and the Self-Test Status Register.

#### Reset Command

This command allows the user, under software control, to return all VMIVME-3119 parameters to their default state. This command does not cause the reset of any hardware circuits.

## Scan Table

The scan table is one of the most powerful features of the VMIVME-3119. The Scan table is read by the DSP each time the Abort/Restart Scan Command is issued. The following is a list of possible uses of the Scan Table:

- The effective sample rate of individual channels can be controlled. As an example, assume only the first three channels are to be scanned. Assume also the Scan Table is set as follows: { x00, x01, x00, x82 }. In this case, the effective sample rate of channel 0 is twice that of channel 1 or channel 2. Note that the HEX code x82 indicates channel 2 and the end of the scan table.

- Unused channels can be disabled.

- Channels can be scanned in any order.

# Sample Buffer RAM

The Sample Buffer RAM contains the corrected samples collected during a scan. The data format of these samples is programmed by the user to be either two's complement or offset binary. The Data Ready Flag and/or the VMEbus Interrupt can be programmed to indicate to the user that a current sample has been stored at the midpoint or end point of the Sample Buffer RAM. The size of the Sample Buffer RAM is determined by the Memory Size configuration jumpers and the Buffer Size control parameter.

# **User-Defined RAM**

All of the upper half of the VMEbus memory space of the VMIVME-3119 that has been enabled by the Memory Size configuration jumpers and not dedicated to the Sample Buffer RAM by the Buffer Size parameter is available as User-Defined RAM.

# **External Triggers**

There are two external trigger sources for the VMIVME-3119. To trigger a scan with either of these sources, the Enable Trigger bit of the Global Configuration Register must be written to a logical 1. The VMIVME-3119 can be triggered by a single ended TTL level high-to-low transition on Pin 8 of P4. If the VMIVME-3119 is configured as a slave, it may be triggered from a master VMIVME-3119 by the differential trigger signals on Pins 5 and 9 of P4.

### **Calibration Coefficients**

In most applications, the user will not need to directly modify the calibration coefficients, however, it is possible for the user to modify the gain and offset applied to an input signal. Whenever the VMIVME-3119 is calibrated, the calibration coefficients are stored in EEPROM, which is not directly accessible by the user. On power up or reset, these coefficients are written to a user-accessible area of memory. Each time the Abort/Restart Scan Command is issued, these coefficients are moved from user-accessible memory to DSP internal memory where they are retrieved each time a data sample is corrected.

**NOTE:** Modifying these registers will alter the performance of the VMIVME-3119. Care must be taken not to inadvertently overwrite these registers.

# Front Panel LED

The front panel LED serves two purposes. First the LED is used to indicate the progression of certain DSP operations such as self-test and at the end of these operations indicates pass/fail by the its state. Second, the user has program control of this LED for any user-defined function.

### **Reference Output and Control Switches**

Calibration of the VMIVME-3119 is based on a precision on-board voltage reference. This reference can be user calibrated either under software control or from the front panel push-button switches. Initiating reference calibration under software control requires a 32-bit software key.

There are three commands which must be used to calibrate the VMIVME-3119. When using the front panel switches, these commands correspond directly to the switches. The commands are Reference Output Advance, Reference Increment, and Reference Decrement. The Reference Output Advance command will advance the reference calibration to the next voltage and, when all voltages have been calibrated, terminate the reference calibration. The Reference Increment and Reference Decrement commands increment or decrement the digital reference by 1-bit weight. The reference voltages in Table 1-1 are listed in the order inwhich they are calibrated.

| Reference Voltage | Status Code Read from<br>Reference Calibration Status Register |

|-------------------|----------------------------------------------------------------|

| 0.3125000 V       | x100                                                           |

| 5.0000000 V       | x101                                                           |

| 9.9218750 V       | x102                                                           |

| 0.0312500 V       | x200                                                           |

| 0.5000000 V       | x201                                                           |

| 0.9921875 V       | x202                                                           |

| 3.1250000 mV      | x300                                                           |

| 50.000000 mV      | x301                                                           |

| 99.218750 mV      | x302                                                           |

| 0.3125000 mV      | x400                                                           |

| 5.0000000 mV      | x401                                                           |

| 9.9218750 mV      | x402                                                           |

|                   | •                                                              |