## **VMIVME-3123**

## 16-bit High Throughput Analog Input Board,16 Channels with Simultaneous Sample-and-Hold Inputs

**Product Manual**

12090 South Memorial Parkway Huntsville, Alabama 35803-3308, USA (256) 880-0444 ◆ (800) 322-3616 ◆ Fax: (256) 882-0859

500-003123-000 Rev. E

12090 South Memorial Parkway Huntsville, Alabama 35803-3308, USA (256) 880-0444 ◆ (800) 322-3616 ◆ Fax: (256) 882-0859 © Copyright 2000. The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

AMXbus, BITMODULE, COSMODULE, DMAbus, IOMax, IOWorks Foundation, IOWorks Manager, IOWorks Server, MAGICWARE, MEGAMODULE, PLC ACCELERATOR (ACCELERATION), Quick Link, RTnet, Soft Logic Link, SRTbus, TESTCAL, "The Next Generation PLC", The PLC Connection, TURBOMODULE, UCLIO, UIOD, UPLC, Visual Soft Logic Control(ler), *VMEaccess*, VMEbus Access, *VMEmanager, VMEmonitor*, VMEnet, VMEnet II, and *VMEprobe* are trademarks and The I/O Experts, The I/O Systems Experts, The Soft Logic Experts, and The Total Solutions Provider are service marks of VMIC.

(I/O man figure)

(IOWorks man figure)

The I/O man figure, IOWorks, IOWorks man figure, UIOC, Visual IOWorks, the VMIC logo, and *WinUIOC* are registered trademarks of VMIC.

ActiveX, Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, Windows NT, and XENIX are registered trademarks of Microsoft Corporation.

Celeron and MMX are trademarks, and Intel and Pentium are registered trademarks of Intel Corporation.

PICMG and CompactPCI are registered trademarks of PCI Industrial Computer Manufacturers' Group.

Other registered trademarks are the property of their respective owners.

12090 South Memorial Parkway Huntsville, Alabama 35803-3308, USA (256) 880-0444 ◆ (800) 322-3616 ◆ Fax: (256) 882-0859

# **Table of Contents**

| List of Figures                               | 9  |

|-----------------------------------------------|----|

| List of Tables                                | 11 |

| Overview                                      | 13 |

| General Description                           | 13 |

| VMIVME-3123 Features                          | 14 |

| Functional Description                        | 15 |

| Reference Material List                       |    |

| Physical Description and Specifications       | 17 |

| Safety Summary                                |    |

| Ground the System                             |    |

| Do Not Operate in an Explosive Atmosphere     |    |

| Keep Away from Live Circuits                  |    |

| Do Not Service or Adjust Alone                |    |

| Do Not Substitute Parts or Modify System      |    |

| Dangerous Procedure Warnings                  |    |

| Safety Symbols Used in This Manual            | 19 |

| Chapter 1 - Theory of Operation               |    |

| Analog Input Circuitry                        |    |

| Built-In-Test (BIT) Circuitry                 |    |

| Input Switching and Instrumentation Amplifier |    |

| Fourth-order Active Filter                    |    |

| Analog-to-Digital Converter                   |    |

| Sample Clock Sources                          | 23 |

| Trigger Sources                               | 25 |

| Correction of Digitized Data                  |    |

|                                               |    |

VMIVME-3123 16-Bit High Throughput Analog Input Board, 16 Channels with Simultaneous Sample-and-Hold Inputs

| DRAM Buffer Memory                                          | 29  |

|-------------------------------------------------------------|-----|

| VMEbus Interface                                            | 30  |

| VMEbus Interrupter                                          | 32  |

| Power Converters                                            | 33  |

| Chapter 2 - Configuration and Installation                  | .35 |

| Unpacking Procedures                                        | 36  |

| Physical Installation.                                      | 36  |

| Before Applying Power: Checklist                            | 36  |

| Operational Configuration                                   | 37  |

| Factory-Installed Jumpers                                   | 37  |

| Access Modes                                                | 39  |

| Board Address                                               | 40  |

| RS-422 Termination Resistor                                 | 40  |

| Calibration                                                 | 41  |

| Auto-Calibration                                            | 41  |

| Built-In-Test (BIT) Reference Voltage Calibration Procedure | 41  |

| Connector Descriptions                                      | 41  |

| Connector Functions                                         | 41  |

| VMEbus Connectors, P1 and P2                                | 41  |

| Analog Input Connectors, P3 and P4                          | 42  |

| External Trigger and Sample Clock Connector, P5             | 42  |

| External Trigger HI (P5, Pin 5)                             | 43  |

| External Trigger LO (P5, Pin 9)                             | 43  |

| External Sample CLK In                                      | 43  |

| Multi-Board Sample CLK 0 (P5, Pin 1)                        | 43  |

| Multi-Board Sample CLK 1 (P5, Pin 6)                        | 43  |

| Multi-Board Trigger (P5, Pin3)                              | 43  |

| Chapter 3 - Programming                                     | .49 |

| Register Descriptions                                       | 50  |

| Board Identification Register (BID)                         | 52  |

| Firmware Revision Register (REV)                            | 52  |

| Control/Status Register 0 (CSR0)                            | 53  |

| Operating Mode Descriptions                                 | 54  |

| Control/Status Register 1(CSR1)                             | 55  |

| Interrupt Vector Register (IVR)                             | 57  |

| Trigger Configuration Register (TRIG)                       | 57  |

| Trigger Delay Register (TDEL)                               | 59  |

| Trigger Threshold Register (TTHLD)                        | . 60 |

|-----------------------------------------------------------|------|

| DSP Trigger Options/Buffer Configuration Register (DTOBC) | . 61 |

| Data Buffer Address Register (DBAR)                       | . 62 |

| Memory Configuration Register (MCR)                       | . 63 |

| Analog Configuration Register (AC)                        | . 64 |

| Analog Channel Enable Register (CHEN)                     | . 65 |

| Analog Conversion Rate Register (RATE)                    | . 66 |

| Test Select/Status Register (TEST)                        | . 67 |

| Error Register (ERROR)                                    | . 68 |

| Buffer Start Address Registers (MSB and LSB)              | . 69 |

| Buffer End Address Registers (MSB and LSB)                | .70  |

| Trigger Address Registers (MSB and LSB)                   | .71  |

| Gain & Offset Correction Factors (Channels 0-15)          | . 72 |

| Analog Channel Errors Register (Channels 0 through 15)    | . 74 |

| Operating Modes                                           | . 75 |

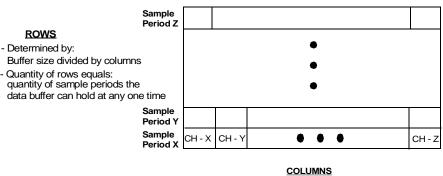

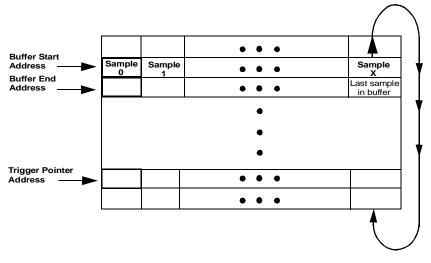

| Data Buffer Operation                                     | . 78 |

| Power Up and Resets                                       | . 81 |

| Triggers and Sample Clocks                                | . 82 |

| Setting Multi-Board and Master Bits                       | . 82 |

| Trigger Select                                            | . 82 |

| Sample Clock Select                                       | . 83 |

| Interrupts                                                | . 84 |

| Typical Programming Examples                              | . 85 |

| Example 1                                                 | . 85 |

| Example 2                                                 | . 85 |

| Example 3                                                 | . 86 |

| Chapter 4 - Maintenance.                                  | . 89 |

| Maintenance                                               | . 89 |

| Maintenance Prints                                        | . 90 |

| Appendix A - Calibration Data                             | 91   |

| Raw Calibration Data                                      | . 92 |

|                                                           |      |

VMIVME-3123 16-Bit High Throughput Analog Input Board, 16 Channels with Simultaneous Sample-and-Hold Inputs

# List of Figures

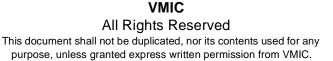

| Figure 1   | VMIVME-3123 Functional Block Diagram                                               | 16 |

|------------|------------------------------------------------------------------------------------|----|

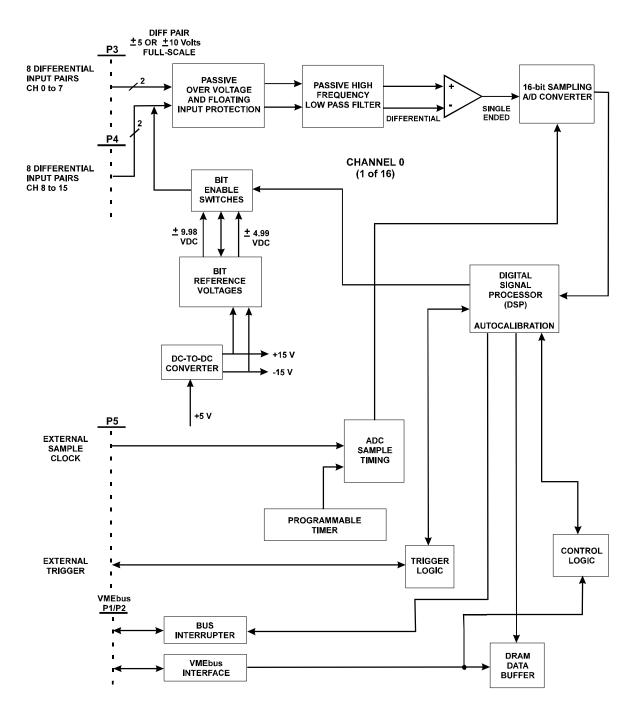

| Figure 1-1 | VMIVME-3123 Sample Clocks                                                          | 24 |

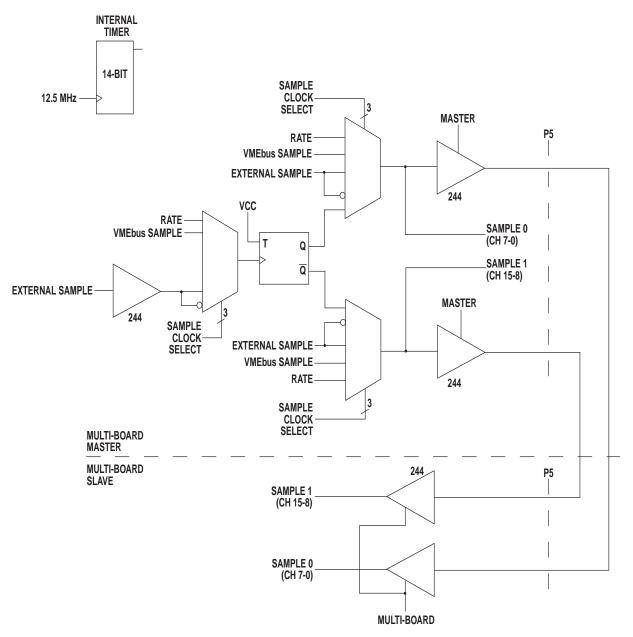

| Figure 1-2 | VMIVME-3123 Trigger Operation                                                      | 26 |

| Figure 1-3 | Trigger Timing Wave Forms                                                          | 27 |

| Figure 1-4 | DRAM Buffer Memory Block Diagram                                                   | 29 |

| Figure 1-5 | VMIVME-3123 VMEbus Interface Block Diagram                                         | 31 |

| Figure 1-6 | VMEbus Interrupter Circuitry                                                       | 32 |

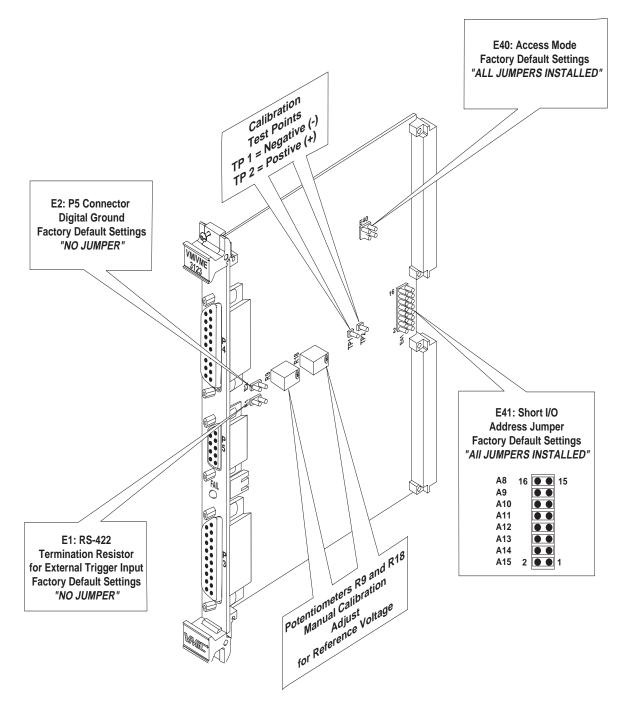

| Figure 2-1 | Locations of User Configurable Jumpers, Calibration Potentiometers and Test Points | 38 |

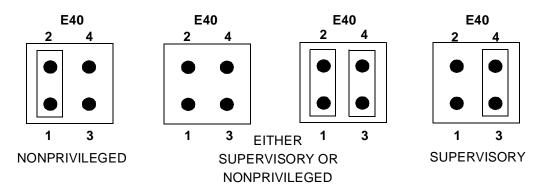

| Figure 2-2 | Supervisory, Nonprivileged Access Mode, and Jumper Locations for Short I/O Space   | 39 |

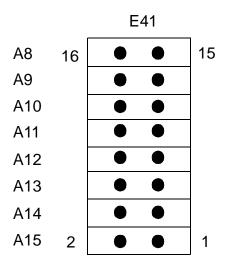

| Figure 2-3 | Board Configuration Jumper                                                         | 40 |

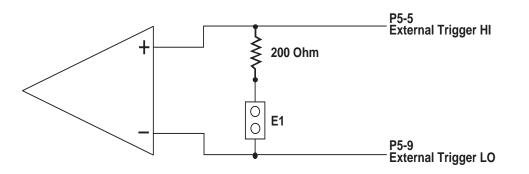

| Figure 2-4 | RS-422 Termination Resistor                                                        | 40 |

| Figure 2-5 | P5 Connector and Pinout                                                            | 42 |

| Figure 2-6 | P1 Connector and Pinout                                                            | 44 |

| Figure 2-7 | P2 Connector and Pinout                                                            | 45 |

| Figure 2-8 | P3 Connector and Pinout                                                            | 46 |

| Figure 2-9 |                                                                                    | 47 |

| Figure 3-1 | Data Buffer Array Configuration                                                    | 79 |

| Figure 3-2 | Data Buffer Pointers, Mid-Trigger Selected                                         | 79 |

VMIVME-3123 16-Bit High Throughput Analog Input Board, 16 Channels with Simultaneous Sample-and-Hold Inputs

## List of Tables

| . 39 |

|------|

| . 50 |

| . 52 |

| . 52 |

| . 53 |

| . 54 |

| . 55 |

| . 56 |

| . 57 |

| . 57 |

| . 58 |

| . 59 |

| . 59 |

| . 60 |

| . 61 |

| . 61 |

| . 62 |

| . 62 |

| . 63 |

| . 63 |

| . 64 |

| . 64 |

| . 65 |

| . 66 |

| . 67 |

| . 68 |

| . 69 |

|      |

VMIVME-3123 16-Bit High Throughput Analog Input Board, 16 Channels with Simultaneous Sample-and-Hold Inputs

| Table 3-27 | Buffer Start Address Register LSB Bit Map 69              |

|------------|-----------------------------------------------------------|

| Table 3-28 | Buffer End Address Register MSB Bit Map70                 |

| Table 3-29 | Buffer End Address Register LSB Bit Map70                 |

| Table 3-30 | Trigger Address MSB Bit Map71                             |

| Table 3-31 | Trigger Address LSB Bit Map                               |

| Table 3-32 | ±10 V Gain Correction Factors CH 0 through 15 Bit Map72   |

| Table 3-33 | ±10 V Offset Correction Factors CH 0 through 15 Bit Map72 |

| Table 3-34 | ±5 V Gain Correction Factors CH 0-15 Bit Map73            |

| Table 3-35 | ±5 V Offset Correction Factors CH 0-15 Bit Map73          |

| Table 3-36 | Analog Channel Errors Register CH 0-15 Bit Map74          |

| Table 3-37 | Buffer Size Values                                        |

| Table A-1  | Precision Reference Voltages                              |

| Table A-2  | Channels 0 through 15                                     |

## Overview

## Contents

| VMIVME-3123 Features               | . 14 |

|------------------------------------|------|

| Functional Description             | . 15 |

| Reference Material List            | . 17 |

| Safety Summary                     | . 18 |

| Safety Symbols Used in This Manual | . 19 |

### Introduction

#### **General Description**

The VMIVME-3123 board is a member of VMIC's extensive family of analog input/output products for the VMEbus. The board boasts 16-bit digitizing resolution on 16-channels, simultaneous sample/hold, software programmable channel select and sampling rate, and a data buffer up to 8 Mbytes. The VMIVME-3123 board provides exceptional dynamic range and high aggregate sampling rate. Various operating modes are supported including transient capture (burst mode) and continuous sample modes, both of which can be configured with internal or external synchronization.

The VMIVME-3123 performs a calibration upon host command of all the analog input channels and stores the corresponding gain and offset correction values in memory. These correction values are then applied to the individual data samples before they are loaded into the DRAM data buffer. Multiple boards can be synchronized together to enable as many as three boards to sample simultaneously. An Interval Timer, Bus Interrupter, DRAM and status flags simplify the monitoring of data within the dual port data buffer. The broad range of system applications that can benefit from the VMIVME-3123 capabilities include factory automation, process control, data acquisition systems, training simulators and laboratory instrumentation.

## VMIVME-3123 Features

The following brief overview of principal features illustrates the flexibility and performance available with the VMIVME-3123 board:

- 16 differential analog inputs

- 16-bit A/D conversion, one converter per channel

- Simultaneous sample-and-hold

- 381 Hz to 100 kHz selectable sampling rate from internal timer

- Auto calibration upon host demand (no channel trimmers)

- Analog input channel ranges of  $\pm$  5 V,  $\pm$  10 V

- 1 or 4 Mbyte sample data buffer (2 or 8 Mbytes)

- Control registers in short I/O (A16), DRAM data buffer in standard (A24) or extended (A32) data space

- · Host controlled data buffer size

- · Optional low pass anti-aliasing input filters

- Transient capture (burst) and continuous sampling modes

- · Choice of external or internal clocking of data samples

- Bus interrupter for buffer control and status

- Board self-test using built-in-test circuitry. Internal reference applied to channel inputs and all active devices tested

## **Functional Description**

The VMIVME-3123 (Figure 1) is a high speed, high-resolution, 16-bit, 16-channel analog digitizing input board with simultaneous sample and hold for VMEbus system applications. A large DRAM data buffer, programmable on-board timer, calibration, and VMEbus interrupter module enable the VMIVME-3123 board to support extensive analog input traffic with a minimum of host processor involvement.

All 16 analog input channels are simultaneously sampled and digitized. During this time, the previous sample (sample n-1) is read from the ADC's, corrected, and stored in the data buffer (if the channel is enabled). The data may then be accessed anytime from the VMEbus. Data correction consists of applying a gain and offset value determined during calibration to the digitized sample. The analog input voltage ranges are software selectable as  $\pm 5$  and  $\pm 10$  V.

The user has control of the analog conversion timing by way of the VMEbus. The A/D converter sample clock source can be chosen from a programmable timer on the VMIVME-3123 or an external sample clock supplied through the P5 front panel connector. The trigger (indicates when board is to store samples in the data buffer) source can be software selectable from a hardware I/O register (host controlled), the P5 front panel connector (external), or from the Digital Signal Processor (DSP checking for a threshold value on a particular input channel). The VMIVME-3123 can operate as a stand alone digitizer, or in tandem with other VMIVME-3123's in a master/slave configuration.

The digitized samples are placed in a DRAM data buffer available in 2 or 8 Mbyte sizes which hold 1 and 4 Mword samples, respectively. The actual buffer size used is dependent upon the number of channels sampled and the programmed buffer size. When using the transient capture mode, the store trigger position is software selectable to allow pre -, mid -, or post-collection of data.

When using the continuous sample mode of operation, the board's VMEbus interrupter module provides a buffer half-full and a buffer full flag that can be used in a polling manner or to generate VMEbus interrupts.

The VMIVME-3123's VMEbus interface locates the board's registers in short I/O space and the DRAM data buffer in standard/extended addressing space. The registers consist of four hardware registers which are available at all times to the host, and DSP controlled firmware registers which are available only during IDLE mode. The DRAM data buffer can be enabled/disabled via host software allowing multiple boards to reside in the same addressing space. The VMEbus data interface supports block transfer (BLT) accesses to aid the user in high speed transfer of large quantities of data.

Figure 1 VMIVME-3123 Functional Block Diagram

## **Reference Material List**

For a detailed explanation of the VMEbus and its characteristics, refer to "The VMEbus Specification" available from:

VITA VMEbus International Trade Association 7825 East Gelding Dr., No. 104 Scottsdale, AZ 85260 (602) 951-8866 FAX: (602) 951-0720 www.vita.com

#### **Physical Description and Specifications**

Refer to Product Specification, 800-003123-000 available from:

VMIC 12090 South Memorial Pkwy. Huntsville, AL 35803-3308, USA (256) 880-0444 (800) 322-3616 FAX: (256) 882-0859 www.vmic.com

#### Safety Summary

The following general safety precautions must be observed during all phases of the operation, service and repair of this product. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture and intended use of this product.

VMIC assumes no liability for the customer's failure to comply with these requirements.

#### Ground the System

To minimize shock hazard, the chassis and system cabinet must be connected to an electrical ground. A three-conductor AC power cable should be used. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet.

#### Do Not Operate in an Explosive Atmosphere

Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.

#### Keep Away from Live Circuits

Operating personnel must not remove product covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### Do Not Service or Adjust Alone

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### Do Not Substitute Parts or Modify System

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to VMIC for service and repair to ensure that safety features are maintained.

#### **Dangerous Procedure Warnings**

Warnings, such as the example below, precede only potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

**STOP:** Dangerous voltages, capable of causing death, are present in this system. Use extreme caution when handling, testing and adjusting.

## Safety Symbols Used in This Manual

Indicates dangerous voltage (terminals fed from the interior by voltage exceeding 1000 V are so marked). Protective conductor terminal. For protection against electrical shock in case of a fault. ⊥\_ OR (-Used with field wiring terminals to indicate the terminal which must be connected to ground before operating equipment. Low-noise or noiseless, clean ground (earth) terminal. Used for a signal common, as well as providing protection against electrical shock in case of a fault. Before operating the equipment, terminal marked with this symbol must be connected to ground in the manner described in the installation (operation) manual. Frame or chassis terminal. A connection to the frame (chassis) of the equipment which normally includes all exposed metal structures. Alternating current (power line). Direct current (power line). Alternating or direct current (power line). **STOP**: Informs the operator that a practice or procedure should not be performed. Actions could result in injury or death to personnel, or could result in damage to or destruction of part or all of the system. WARNING: Denotes a hazard. It calls attention to a procedure, a practice or a condition, which, if not correctly performed or adhered to, could result in injury or death to personnel. CAUTION: Denotes a hazard. It calls attention to an operating procedure, a practice or a condition, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the system.

**NOTE:** Calls attention to a procedure, a practice, a condition or the like, which is essential to highlight.

VMIVME-3123 16-bit High Throughput Analog Input Board, 16 Channels with Simultaneous Sample-and-Hold Inputs

# Theory of Operation

## Contents

| Sample Clock Sources         | . 23 |

|------------------------------|------|

| Frigger Sources              | . 25 |

| Correction of Digitized Data | . 28 |

| DRAM Buffer Memory           | . 29 |

| VMEbus Interface             | . 30 |

| VMEbus Interrupter           | . 32 |

| Power Converters             | . 33 |

|                              |      |

## Introduction

This section describes the internal organization of the VMIVME-3123 board and reviews the general principles of operation. The major board functions are summarized in the remainder of Chapter 1 and supplemented by programming details in Chapter 3.

The VMIVME-3123 board contains the following principal hardware functions:

- Analog input circuitry and digitizing

- Sample clock sources

- Trigger sources

- Correction of digitized data

- DRAM buffer memory

- VMEbus interface

- VMEbus interrupter

- Power converters

#### **Analog Input Circuitry**

The analog circuitry is responsible for interfacing to the external field wiring, for signal conditioning, and for digitizing the samples. Several blocks make up the analog circuitry and will be described in detail. These blocks are:

- Built-in-Test Circuit (BIT)

- Input switching and instrumentation amplifier

- Fourth-order active filter

- Analog-to-Digital Converter (ADC)

#### **Built-In-Test (BIT) Circuitry**

The Built-In-Test (BIT) circuit contains a precision reference which supplies the input circuitry with a known voltage for calibration of each channel. The available voltages from the BIT circuit are  $\pm 9.98$ ,  $\pm 4.99$ , and 0.00 volts. The desired voltage is selected using four bits available in the Analog Configuration register on page 64.

#### Input Switching and Instrumentation Amplifier

Each input contains a passive RC filter followed by a quad SPDT (single pole, double throw) switch. The switch is used to disconnect the field inputs and apply the BIT voltages during calibration. The switch is also used to control the gain of the input depending on the input range selected. The input range is selected by the Analog Configuration register. Each input contains an Instrumentation Amplifier (IA) which converts the differential input signal to single-ended for further processing and digitizing. The IA also provides common-mode rejection.

#### Fourth-order Active Filter

Each input contains a fourth-order active filter with factory-optional Butterworth or Bessel response. The frequency cut-off is also factory-optional as listed in the Specification.

#### **Analog-to-Digital Converter**

Each input has its own Analog-to-Digital Converter (ADC). The ADC is a 16-bit No Missing Codes successive-approximation device. It has its own internal reference and track/hold circuitry and requires only a convert and clock signal. The ADC outputs the previously converted data in a serial two's complement format while the present sample is being converted. The serial data is converted to parallel for input to the DSP for gain and offset correction.

## Sample Clock Sources

The VMIVME-3123 board uses sample clock sources to start the ADC conversion process. The host may choose from an internal 14-bit timer derived from a 12.5 MHz clock, VMEbus I/O command, or an external host supplied clock signal.

The chosen clock source is divided into two clock signals, sample 0 and sample 1, which provide the sampling signals for analog input channels 7-0 and 15-8, respectively. The VMIVME-3123 also allows the user to choose a clock doubling feature which routes the input clock source through a phase splitting flip-flop and staggers the sampling of channels 7 through 0 and 15 through 8. Channels 0 and 8, 1 and 9, etc. become paired and should be connected to the same input signal. The sample clock input source can now be increased above 100 kHz (up to 200 kHz) and the effective sample rate of the channel increases to that rate while the actual sampling rate on the individual ADC does not go beyond 100 kHz.

The user can choose to use multiple boards in parallel. The host should set the multi-board bit (bit 3) to a logic "1" in the Trigger Configuration register on all the boards and set the master bit (in the same register) to a logic "1" on the master board and to a logic "0" on the slave boards. This configures all the boards to receive the clock source selected on the master board.

Figure 1-1 VMIVME-3123 Sample Clocks

### **Trigger Sources**

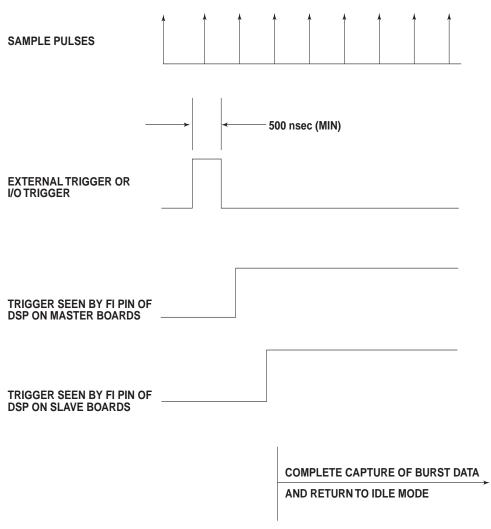

The VMIVME-3123 board uses trigger sources as an indication of when to conclude data capture during the Transient Capture mode of operation. The trigger sources are only used during Transient Capture mode. Figure 1-2 on page 26 shows the structure of the trigger circuitry, including a second board set-up as a slave if a multi-board configuration is needed. First, the host should set the multi-board bit (Bit 3) and the master bit (Bit 4) of the Trigger Configuration register to initialize the buffers used in multi-board operation. When the multi-board bit is a logic "0", the buffer receiving the bussed trigger signal is off. When the multi-board bit is a logic "1" and the master bit is a logic "0", the board will receive the bussed trigger signal. If both the multi-board and master bits are set to a logic "1", both the receiving and driving buffer will be enabled.

The trigger select bits are used to select the desired trigger from a choice of a differential RS-422 external source (both positive or negative pulse), an I/O trigger bit from the CSR1, or the DSP trigger which compares a host selected input channel with a host selected threshold value. When using an external source, the trigger pulse should be greater than 500 nanoseconds. During the course of correcting and storing the sampled data, the DSP monitors the Flag In (FI) pin connected to the trigger circuitry output. Upon receiving a trigger signal from the trigger output circuitry, the Flag Out (FO) pin will be set. The DSP will then proceed to either stop processing sampled data and return to IDLE mode if the pre-trigger setup was selected, or finish collecting and storing data and return to IDLE mode if mid- or post-trigger options were selected. See Chapter 3 for more information on triggering.

**NOTE:** The board must be initialized prior to entering Transient Capture mode. Before beginning the sampling process, the board clears the trigger circuitry. This process takes approximately 1.27 msec. The user needs to make sure the trigger event does not occur sooner than 1.27 msec after the board is put into Transient Capture mode.

Figure 1-2 VMIVME-3123 Trigger Operation

Figure 1-3 Trigger Timing Wave Forms

## **Correction of Digitized Data**

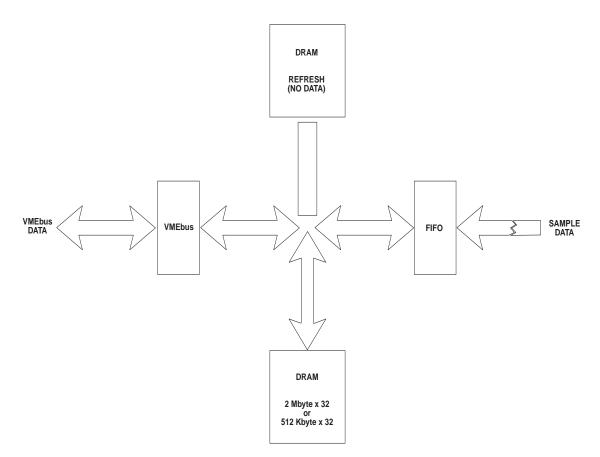

Correction of the digitized data is performed by an on-board Digital Signal Processor (DSP). The digitized data from the previous sample period (n-1) is output serially from each of the ADCs and parallel to serial conversion is performed to format the data for reception by the DSP. The DSP sequentially reads the digitized parallel data and performs a gain and offset correction using coefficients determined during the calibration mode. After correcting the data, the DSP checks for channel enables in determining which channel's data will be placed in DRAM, checks for buffer half-full and full conditions, and performs other assorted firmware tasks. The DSP then writes the corrected samples to a FIFO and informs an on-board state machine to load the data into the DRAM. The state machine requests the DRAM from the memory bus arbiter and bursts the samples into DRAM when the memory bus is granted to it.

## **DRAM Buffer Memory**

The DRAM Buffer Memory consists of either a 2 Mbyte x 32 (8 Mbyte) or 512 K x 32 (2 Mbyte) SIMM module loaded on the VMIVME-3123 board. There are three functions that use the memory and need to be arbitrated. The highest priority function is the DSP's sample data load. The DSP loads data into a FIFO and then instructs a hardware state machine to burst load the data from the FIFO to the DRAM. This data load operation may hold-off a VMEbus DTACK up to 1.5  $\mu$ sec. This operation occurs at the same rate the channels are being sampled. The second highest priority function is DRAM refresh. A refresh will occur every 16  $\mu$ sec and will hold the memory occupied for approximately 500 nanoseconds. VMEbus accesses by the host have the lowest priority. The VMIVME-3123 must use the same size SIMM module it was configured with originally because internal programming of the EPLD's must match the installed SIMM module. See Figure 1-4 for the DRAM Buffer Memory Block Diagram.

Figure 1-4 DRAM Buffer Memory Block Diagram

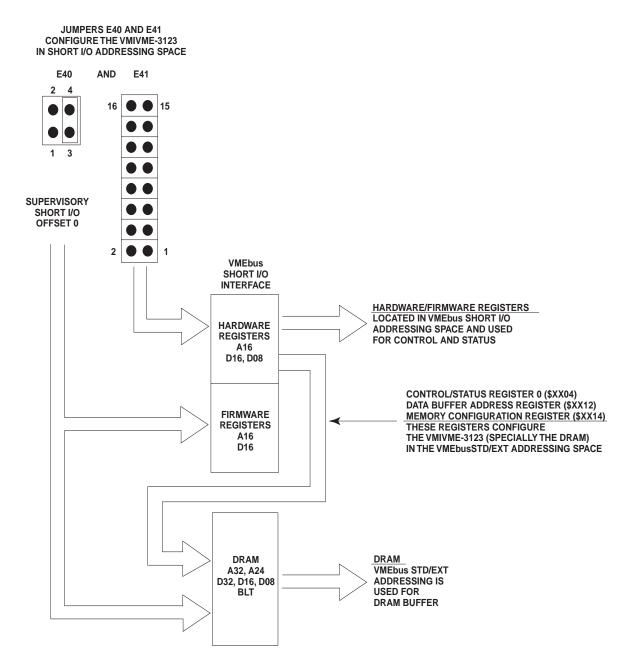

#### VMEbus Interface

The VMIVME-3123 VMEbus slave interface consists of a VMEbus short I/O interface used for communicating with the Control and Status registers, and a VMEbus standard/extended interface used to read the accumulated data samples (see Figure 1-5 on page 31). The short I/O interface communicates with four hardware registers and numerous firmware. The hardware registers are physically located in programmable logic and their contents are available at all times. The access times for these registers are in the order of hundreds of nanoseconds because no firmware interaction is involved. The firmware registers are physically located in the DSP's SRAM and are only available when the VMIVME-3123 board is operating in IDLE mode. IDLE mode allows the firmware enough time to service the VMEbus requests. The access times of the firmware registers is in the order of 1.5 to 3 msec due to the fact that the DSP firmware is involved with servicing these requests.

The VMIVME-3123 board's VMEbus standard and extended interface is used to retrieve the stored sample data contained in the DRAM, and is under host control. The access to the interface is controlled by the CSR0, the Data Buffer Address register and the Memory Configuration register. The buffer enable bit located in CSR0 either enables or disables the entire memory from access by the VMEbus. The Data Buffer Address register allows the host to choose either standard (A24) or extended (A32) addressing space, the access type and the address offset desired. The Memory Configuration register is a read-only register allowing the host to determine the size of the DRAM used with the board.

Data can be read/written as either 32, 16 or 8 bits and includes VMEbus BLT (block transfers) support as well. The VMEbus BLT hardware allows the board to use the enhanced page mode feature of the DRAM on VMEbus read cycles, thereby increasing the VMEbus data rate by pre-reading the next piece of data (if requested). On VMEbus BLT write accesses, the page mode operation does not result in faster access times. Refer to the VMIVME-3123 Specification for actual access times.

**NOTE:** The firmware registers are word (16-bit) oriented which allows them to be read in a byte or word format but written to in a word format only. Byte writes to firmware registers will return a DTACK\* to the host but leave the contents of the register unchanged. The short I/O interface uses hardware jumpers to set-up its configuration in VMEbus space.

VMEbus Interface

Figure 1-5 VMIVME-3123 VMEbus Interface Block Diagram

### **VMEbus Interrupter**

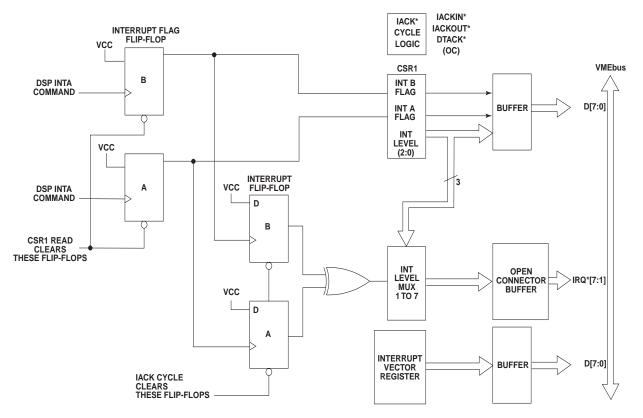

The VMIVME-3123 Interrupter circuit is shown in Figure 1-6. The Control and Status Register 1 and the Interrupt Vector register are used in controlling interrupt operations. The interrupt flags A and B located in CSR1 are controlled by the action of the DSP and are set according to the operating mode chosen. The flag can be polled by reading CSR1. The act of reading CSR1 clears the interrupt A and B flags. An additional set of flip-flops are latched when an interrupt A or B flag is set and generates a VMEbus interrupt according to the interrupt level bits if the interrupt level bits in CSR1 are non-zero. At this point, the host hardware generates a VMEbus IACK cycle which clears the interrupt generating flip-flops and returns a pre-programmed interrupt vector to the host. The host should then clear the interrupt flags in its interrupt service routine by reading CSR1. Hardware circuitry handles the IACKIN\*/IACKOUT\* daisy chain, as well as generating the DTACK\* signal.

Figure 1-6 VMEbus Interrupter Circuitry

## **Power Converters**

The VMIVME-3123 uses DC to DC converters on-board to convert +5 VDC logic power from the VMEbus into isolated and regulated  $\pm 15$  and +5 VDC for the analog networks. This method allows the user to disregard the optional  $\pm 12$  VDC on the VMEbus backplane.

VMIVME-3123 16-bit High Throughput Analog Input Board, 16 Channels with Simultaneous Sample-and-Hold Inputs

# **Configuration and Installation**

## Contents

| Unpacking Procedures      | 36 |

|---------------------------|----|

| Operational Configuration | 37 |

| Calibration               | 41 |

## Introduction

This chapter describes the installation and configuration of the board. Cable configuration and board layout are illustrated in this chapter.

### **Unpacking Procedures**

**CAUTION:** Some of the components assembled on VMIC's products may be sensitive to electrostatic discharge and damage may occur on boards that are subjected to a high-energy electrostatic field. When the board is placed on a bench for configuring, etc., it is suggested that conductive material should be inserted under the board to provide a conductive shunt. Unused boards should be stored in the same protective boxes in which they were shipped.

Upon receipt, any precautions found in the shipping container should be observed. All items should be carefully unpacked and thoroughly inspected for damage that might have occurred during shipment. The board(s) should be checked for broken components, damaged printed circuit board(s), heat damage, and other visible contamination. All claims arising from shipping damage should be filed with the carrier and a complete report sent to VMIC together with a request for advice concerning the disposition of the damaged item(s).

#### **Physical Installation**

WARNING: Do not install or remove boards while power is applied.

De-energize the equipment and insert the board into an appropriate slot of the chassis. While ensuring that the board is properly aligned and oriented in the supporting card guides, slide the board smoothly forward against the mating connector until firmly seated.

#### **Before Applying Power: Checklist**

Before applying power to the VMEbus chassis in which the board is installed, execute the following checklist to ensure that the board has been correctly prepared for operation.

- 1. Verify that the sections pertaining to Chapter 3 have been reviewed and applied to system requirements.\_\_\_\_\_

- 2. Review the *Operational Configuration* on page 37 and Table 2-1 on page 39 to verify that all jumpers are configured correctly for the application. \_\_\_\_\_

- 3. Verify that the I/O cables are properly terminated for the input/output connectors. Refer to *Connector Descriptions* on page 41. \_\_\_\_\_

- 4. Physical installation should have been completed as described in that section.

- 5. Ensure that all system cable connections are correct.\_\_\_\_

- 6. Ensure that no empty slots are between the system controller and the VMIVME-3123 or that the interrupt daisy chain jumpers are properly installed.

### **Operational Configuration**

The VMIVME-3123 is designed to minimize the number of field programmable jumpers to be set by the user. VMEbus Short I/O address offset and access modes are controlled by field replaceable jumpers. In addition to these jumpers, the board contains a RS-422 termination resistor jumper. This section describes the use of these jumpers, and their effects on board performance. Locations and functions of all VMIVME-3123 jumpers are shown in Figure 2-1 on page 38 and Table 2-1 on page 39.

### **Factory-Installed Jumpers**

Each VMIVME-3123 board is configured at the factory with its Short I/O (A16) jumpers configured for the following:

- Board Identification is located at \$0000 in the Short I/O space.

- The board access is jumpered to respond to either supervisory or nonprivileged.

- The external trigger's RS-422 receiver termination resistor is off.

- Digital ground is not provided to connector P5 (E2 is removed).

VMIVME-3123 16-Bit High Throughput Analog Input Board, 16 Channels with Simultaneous Sample-and-Hold Inputs

Figure 2-1 Locations of User Configurable Jumpers, Calibration Potentiometers and Test Points

| <b>റ</b> |  |

|----------|--|

| Ζ        |  |

| Jumper IDENT | Function (Installed)                      | Factory CONFIG |

|--------------|-------------------------------------------|----------------|

| E1 -1, 2     | RS-422 Termination Resistor (EXT Trigger) | Removed        |

| E2 -1, 2     | Connector P5 Digital Ground               | Removed        |

| E40 -1, 2    | Access Mode, Nonprivileged*               | Installed      |

| E40 -3, 4    | Access Mode, Supervisory*                 | Installed      |

|              |                                           |                |

| E41-1, 2     | Address Bit A15 = 0                       | Installed      |

| E41-3, 4     | Address Bit A14 = 0                       | Installed      |

| E41-5, 6     | Address Bit A13 = 0                       | Installed      |

| E41-7, 8     | Address Bit A12 = 0                       | Installed      |

| E41-9, 10    | Address Bit A11 = 0                       | Installed      |

| E41-11, 12   | Address Bit A10 = 0                       | Installed      |

| E41-13, 14   | Address Bit A9 = 0                        | Installed      |

| E41-15, 16   | Address Bit A8 = 0                        | Installed      |

Table 2-1 Programmable Jumper Functions

\* See "Access Modes" below for more details.

**NOTE:** To be consistent with conventional VMEbus development system nomenclature, hexadecimal numbers in this document are designated a "\$" prefix unless otherwise indicated. Decimal numbers are presented without a prefix.

### **Access Modes**

Short I/O address space, supervisory (privileged) and user (nonprivileged) access are selected by jumper E40. Figure 2-2 shows the jumper location and access mode.

Figure 2-2 Supervisory, Nonprivileged Access Mode, and Jumper Locations for Short I/O Space

### **Board Address**

The board's short I/O address is configured by jumper E41. The jumper corresponding to the address bits are shown in Figure 2-3.

Figure 2-3 Board Configuration Jumper

The board address is programmed by installing shorting plugs at all "zero" or LOW address bit positions in jumper block E41, and by omitting the shorting plugs at the "one" or HIGH positions. Address bit A8 is the least significant address bit that can be jumper-selected, and has a weight of 256 bytes.

#### **RS-422 Termination Resistor**

The External Trigger circuitry includes a RS-422 differential receiver to accommodate trigger sources some distance from the board. The host may jumper E1 to include the 200W termination resistor located on its differential input side of the receiver when the application warrants it. (see Figure 2-4).

Figure 2-4 RS-422 Termination Resistor

### Calibration

### Auto-Calibration

The VMIVME-3123 features a host controlled auto-calibration. The calibration coefficients are stored in volatile memory on auto-calibration. Therefore, the host is required to initiate an auto-calibration after power-up. The VMIVME-3123's uncalibrated performance may only run approximately 1 percent. The host has the option of performing calibration, reading the coefficients from the VMIVME-3123 board, and storing them in nonvolatile memory of its own. The host can then load the coefficients into the proper locations on the VMIVME-3123 in lieu of performing an auto-calibration.

### **Built-In-Test (BIT) Reference Voltage Calibration Procedure**

- 1. Attach the voltmeter's positive lead to TP2 and negative lead to TP1 (see Figure 2-1 on page 38 for location of test points and adjustment potentiometers).

- 2. Write hexadecimal value 0x4000 to the Analog Configuration register at offset address 0x0016.

- 3. Adjust potentiometer R18 for a reading of  $9.980000 \pm .000200$  VDC.

- 4. Write hexadecimal value 0x6000 to the Analog Configuration register at offset address 0x0016.

- 5. Adjust potentiometer R9 for a reading of  $4.990000 \pm .000150$  VDC.

- 6. Repeat steps 2 through 5 as many times as required for calibration accuracy.

- 7. Apply "Red GLPT Insulating Varnish" available from GC Electronics P/N 10-9002 (or equivalent) to potentiometers R18 and R9.

### **Connector Descriptions**

#### **Connector Functions**

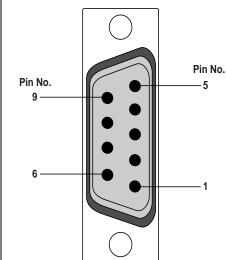

Electrical connections to the VMIVME-3123 Board are made through two 96-pin DIN connectors (P1 and P2), two 25-pin D-Subminiature connectors (P3 and P4), and one 9-pin D-Subminiature connector (P5). The P1 and P2 connectors attach the VMIVME-3123 Board to the VMEbus backplane, and contain power, address, data, control lines and all additional signals necessary to control VMEbus functions related to the board. Connectors P3 and P4 include the differential analog inputs for channels 0 thru 15. Connector P5 contains the external trigger and sample clock signals as well as the multi-board synchronization signals.

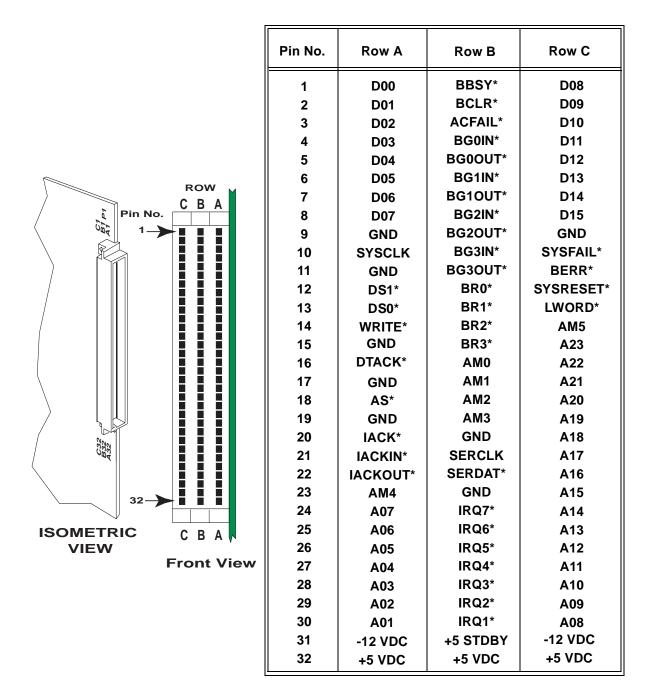

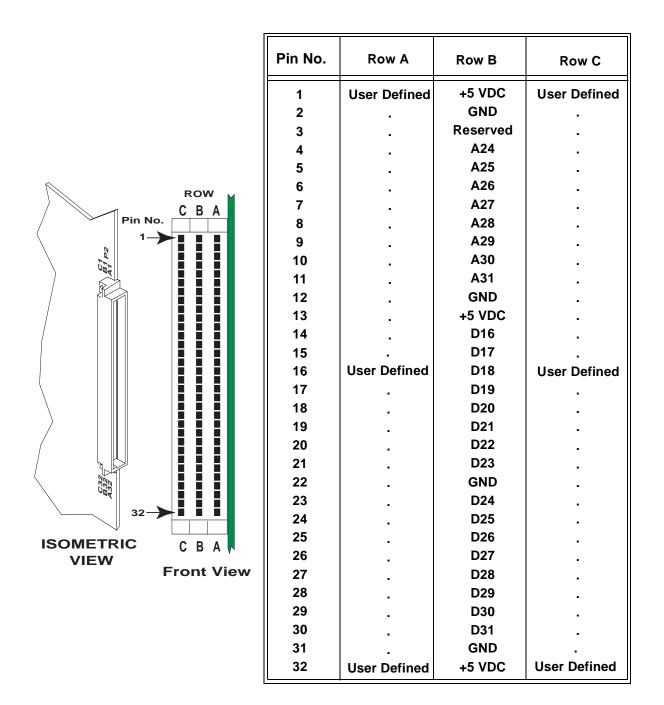

#### VMEbus Connectors, P1 and P2

The signal names and connectors are shown in Figure 2-6 on page 44 for the P1 connector, and Figure 2-7 on page 45 for the P2 connector.

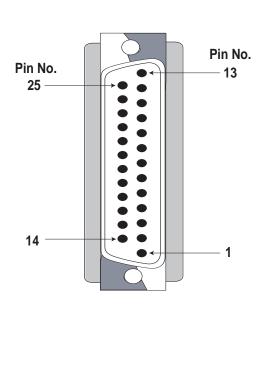

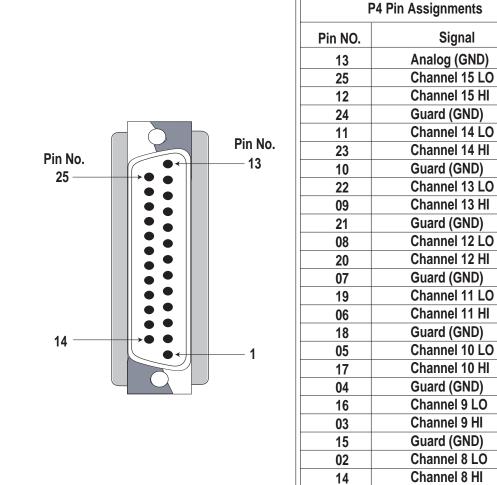

### Analog Input Connectors, P3 and P4

The signal names for connectors P3 and P4 are shown in Figure 2-8 on page 46 and Figure 2-9 on page 47. These are female 25-pin D-Subminiature connectors whose shells are connected via the board to the front panel allowing the user to continue the connection to the chassis if desired.

Connector P3 contains the analog input signals for channels 7 through 0 and connector P4 contains the analog input signals for channels 15 through 8.

It is recommended that all unused analog input channels be properly grounded. Proper grounding can be achieved by connecting HI to LO to Guard for each unused channel.

For some input signals, it may be necessary to connect the Guard pin to the LO pin. This is absolutely necessary for isolated input signal sources.

### **External Trigger and Sample Clock Connector, P5**

The signal names and connector P5 are shown below. This connector is a female 9-pin D-Subminiature connector whose shell is connected via the board to the front panel allowing the user to continue the connection to the chassis.

| P5 Pin Assignments |                                       |  |

|--------------------|---------------------------------------|--|

| Pin No.            | Signal                                |  |

| 5                  | External Trigger HI                   |  |

| 9                  | External Trigger LO                   |  |

| 4                  | *No Connect/Digital GND               |  |

| 8                  | External Sample CLK IN                |  |

| 3                  | Multi-Board Trigger                   |  |

| 7                  | *No Connect/Digital GND               |  |

| 2                  | *No Connect/Digital GND               |  |

| 6                  | Multi-Board Sample CLK1               |  |

| 1                  | Multi-Board Sample CLK 0              |  |

| Each of the pages. | signals is described on the following |  |

Figure 2-5 P5 Connector and Pinout

### External Trigger HI (P5, Pin 5) External Trigger LO (P5, Pin 9)

The External Trigger HI and LO signals are differential inputs to a RS-422 receiver that continues into the board's triggering circuitry. The user may connect the optional 200W termination resistor (See "RS-422 Termination Resistor" on page 40) if the application warrants it. The Trigger Configuration register's Bits 5 and 6 are used to select this trigger input if desired.

### **External Sample CLK In**

The External Sample CLK In signal is a TTL type input used to accept an external clocking source. The length of the connection from the external clocking source to the VMIVME-3123's P5 connector should be kept as short as possible. The Trigger Configuration Register's Bits 2, 1, and 0 are used to select this sample clock source if desired. The maximum clock frequency allowed is 200 kHz when channel doubling is selected. The effective sampling rate will be doubled by utilizing both edges of the clock.

### Multi-Board Sample CLK 0 (P5, Pin 1) Multi-Board Sample CLK 1 (P5, Pin 6)

The Multi-Board Sample CLK 0 and 1 are TTL level signals that should be bussed across all boards used in a multi-board configuration. The host will initialize the master board which will drive the signals as outputs. The host will also initialize the slave or slaves which will receive the signals as inputs.

### Multi-Board Trigger (P5, Pin3)

The Multi-Board Trigger is a TTL level signal that should be bussed across all boards used in a multi-board configuration. The host will initialize the master board which will drive the signal as an output. The host will also initialize the slaves which will receive the signal as an input.

Figure 2-6 P1 Connector and Pinout

Figure 2-7 P2 Connector and Pinout

| P3      | Pin Assignments |

|---------|-----------------|

| Pin NO. | Signal          |

| 13      | Analog (GND)    |

| 25      | Channel 7 LO    |

| 12      | Channel 7 HI    |

| 24      | Guard (GND)     |

| 11      | Channel 6 LO    |

| 23      | Channel 6 HI    |

| 10      | Guard (GND)     |

| 22      | Channel 5 LO    |

| 09      | Channel 5 HI    |

| 21      | Guard (GND)     |

| 08      | Channel 4 LO    |

| 20      | Channel 4 HI    |

| 07      | Guard (GND)     |

| 19      | Channel 3 LO    |

| 06      | Channel 3 HI    |

| 18      | Guard (GND)     |

| 05      | Channel 2 LO    |

| 17      | Channel 2 HI    |

| 04      | Guard (GND)     |

| 16      | Channel 1 LO    |

| 03      | Channel 1 HI    |

| 15      | Guard (GND)     |

| 02      | Channel 0 LO    |

| 14      | Channel 0 HI    |

| 01      | Guard (GND)     |

Figure 2-8 P3 Connector and Pinout

Signal

Guard (GND)

Figure 2-9 P4 Connector and Pinout

01

VMIVME-3123 16-Bit High Throughput Analog Input Board, 16 Channels with Simultaneous Sample-and-Hold Inputs

# Programming

### Contents

| Register Descriptions        | 50 |

|------------------------------|----|

| Operating Modes              | 75 |

| Data Buffer Operation        | 78 |

| Power Up and Resets          | 81 |

| Triggers and Sample Clocks   | 82 |

| Interrupts                   | 84 |

| Typical Programming Examples | 85 |

### Introduction

This section of the manual deals with the VMEbus software interface to the VMIVME-3123 board. Programming the VMIVME-3123 assumes a properly installed board accessed from an appropriate VMEbus system controller. Installation and hardware jumper configuration requirements are described in Chapter 2.

The VMIVME-3123 is physically addressed in two places within VMEbus addressing space: configuration, status and control activity takes place through the registers in A16 short I/O space, while the converted data is available through a much larger DRAM data buffer in A24 standard or A32 extended address space. The base address location for the control registers in A16 short I/O is programmed with hardware jumpers described in Chapter 2. The address, size and addressing mode of the data buffer, however, must be programmed via the short I/O registers. A bus interrupter is also available to generate interrupt requests, although interrupts are not necessary.

Software configuration is necessary before using the VMIVME-3123. After powerup or hardware reset, the VMIVME-3123 enters IDLE mode, without generating converted analog signal data but, making all registers and software control structures available. Host software can configure the board while IDLE, select the appropriate analog conversion mode, and begin reading data from the data buffer. If enabled, interrupts are handled via hardware registers without halting data conversion. Software returns the board to IDLE mode only to interact with various firmware registers, such as when re-configuring the board.

### **Register Descriptions**

The VMIVME-3123 Configuration and Control registers occupy 256 bytes of VMEbus short I/O address space, although some of this space is unused. The register's base address and VMEbus access mode within short I/O space are set by hardware jumper fields described in Chapter 2.

Table 3-1 details the register map, including register names, sizes and access restrictions. Note that most registers are implemented by the board's firmware. Although hardware registers are always valid and available, firmware registers are only valid when the board's operating mode is set to IDLE (See Control/Status Register 0 for details on setting the operating mode). *Unless the VMIVME-3123 operating mode is IDLE, any values written to or read from firmware registers are meaningless.*

| Short I/O<br>Offset<br>Address | Size | Access     | Register Name                                        | Туре     | Suggested<br>Mnemonic |

|--------------------------------|------|------------|------------------------------------------------------|----------|-----------------------|

| \$0000                         | Word | Read-Only  | Board Identification Register                        | Firmware | BID                   |

| \$0002                         | Word | Read-Only  | Firmware Revision Register                           | Firmware | REV                   |

| \$0004                         | Word | Read/Write | Control/Status Register 0                            | Hardware | CSR0                  |

| \$0006                         | Word | Read/Write | Control/Status Register 1                            | Hardware | CSR1                  |

| \$0008                         | Word | Read/Write | Interrupt Vector Register                            | Hardware | IVR                   |

| \$000A                         | Word | Read/Write | Trigger Configuration Register                       | Hardware | TRIG                  |

| \$000C                         | Word | Read/Write | Trigger Delay Register                               | Firmware | TDEL                  |

| \$000E                         | Word | Read/Write | Trigger Threshold Register                           | Firmware | TTHLD                 |

| \$0010                         | Word | Read/Write | DSP Trigger Options/Buffer<br>Configuration Register | Firmware | DTOBC                 |

| \$0012                         | Word | Read/Write | Data Buffer Address Register                         | Firmware | DBAR                  |

| \$0014                         | Word | Read/Write | Memory Configuration Register                        | Firmware | MCR                   |

| \$0016                         | Word | Read/Write | Analog Configuration Register                        | Firmware | AC                    |

| \$0018                         | Word | Read/Write | Analog Channel Enable Register                       | Firmware | CHEN                  |

| \$001A                         | Word | Read/Write | Analog Conversion Rate Register                      | Firmware | RATE                  |

| \$001C                         | Word | Read/Write | Test Select/Status Register                          | Firmware | TEST                  |

| \$001E-\$0020                  |      |            | Reserved                                             |          |                       |

| \$0022                         | Word | Read-Only  | Error Register                                       | Firmware | ERROR                 |

| \$0024                         | Word | Read-Only  | Buffer Start Address Register LSB                    | Firmware | BSARL                 |

| \$0026                         | Word | Read-Only  | Buffer Start Address Register MSB                    | Firmware | BSARM                 |

| \$0028                         | Word | Read-Only  | Buffer End Address Register LSB                      | Firmware | BEARL                 |

| \$002A                         | Word | Read-Only  | Buffer End Address Register MSB                      | Firmware | BEARM                 |

| Table 3-1 | \/MI\/ME_3123 Board Pegister Man |

|-----------|----------------------------------|

| Table 3-1 | VMIVME-3123 Board Register Map   |

| Short I/O<br>Offset<br>Address | Size      | Access     | Register Name                                      | Туре     | Suggested<br>Mnemonic |

|--------------------------------|-----------|------------|----------------------------------------------------|----------|-----------------------|

| \$002C                         | Word      | Read-Only  | Trigger Address LSB                                | Firmware | TAL                   |

| \$002E                         | Word      | Read-Only  | Trigger Address MSB                                | Firmware | TAM                   |

| \$0030-\$003E                  |           |            | Reserved                                           |          |                       |

| \$0040-\$005E                  | Word(X16) | Read/Write | ±10 V Gain Correction Factors<br>(Channels 0-15)   | Firmware | GCFHI00-<br>GCFHI15   |

| \$0060-\$007E                  | Word(X16) | Read/Write | ±10 V Offset Correction Factors<br>(Channels 0-15) | Firmware | OCFHI00-<br>OCFHI15   |

| \$0080-\$009E                  | Word(X16) | Read/Write | ±5 V Gain Correction Factors<br>(Channels 0-15)    | Firmware | GCFLO00-<br>GCFLO15   |

| \$00A0-<br>\$00BE              | Word(X16) | Read/Write | ±5 V Offset Correction Factors<br>(Channels 0-15)  | Firmware | OCFLO00-<br>OCFLO15   |

| \$00C0-<br>\$00DE              | Word(X16) | Read-Only  | Analog Channel Errors Register                     | Firmware | AERR00-<br>AERR15     |

| \$00E0-<br>\$00FE              |           |            | Reserved                                           |          |                       |

**NOTES: Short I/O Offset Addresses** are offset relative to the base address defined by a jumper field. See Chapter 2 for jumper details. **Size** is the binary size of the register. Hardware registers can be read and written to as bytes or words. Firmware Registers can be only written to as a word. Byte writes to firmware registers will leave the register unchanged. Firmware registers can be read as a byte or word. **Access** indicates intended function only: most firmware "read-only" registers may actually be written, but any data written is volatile. **Type** describes how the register is implemented. Hardware registers are always available. Firmware registers are only valid in IDLE mode (see the Control/Status Register 0 for mode details). **In any mode** *except IDLE mode, values written to or read from firmware registers are meaningless.* **Reserved** bits and registers will read indeterminate values. If a bit marked Reserved must be written, it should always be cleared (binary 0).

### **Board Identification Register (BID)**

The Board Identification Register is a read only firmware word at offset \$0000. It contains the fixed value \$3DXX, which uniquely identifies this product from other VMIC VMEbus boards. Like all Firmware registers, this register is only valid in IDLE mode. Table 3-2 details this register's bit map.

| Board ID Register (Offset \$0000) Read-Only Firmware, Word |        |        |        |        |        |        |        |

|------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| Bit 15                                                     | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 09 | Bit 08 |

| 0                                                          | 0      | 1      | 1      | 1      | 1      | 0      | 1      |

| Bit 07 Bit 06 Bit 05 Bit 04 Bit 03 Bit 02 Bit 01 Bit 00    |        |        |        |        |        |        |        |

| Table 3-2 | Board ID | Register | Bit Map |

|-----------|----------|----------|---------|

|           |          |          |         |

Bit 07

Bit 06

Bit 05

Bit 04

Bit 03

Bit 02

Bit 01

Bit 00

Power-up/Reset Default = \$3DXX

### Firmware Revision Register (REV)

The Firmware Revision Register is a read-only firmware word at offset \$0002. It contains a single value which identifies the on-board firmware revision number. Like all firmware registers, this register is only valid in IDLE mode. Table 3-3 details the register's bit map.

Table 3-3 Firmware Revision Register Bit Map

|        | Firmwa | re Revision R | egister (Offse | t \$0002) Read | -Only Firmwar | e, Word |        |

|--------|--------|---------------|----------------|----------------|---------------|---------|--------|

| Bit 15 | Bit 14 | Bit 13        | Bit 12         | Bit 11         | Bit 10        | Bit 09  | Bit 08 |

| Rev 7  | Rev 6  | Rev 5         | Rev 4          | Rev 3          | Rev 2         | Rev 1   | Rev 0  |

| Bit 07 | Bit 06 | Bit 05        | Bit 04         | Bit 03         | Bit 02        | Bit 01  | Bit 00 |

| 2.1.07 | 2.1.00 | 2.1.00        |                | rved           | 2             | 2       | 211 00 |

Power-up/Reset Default = \$RR00 RR = Revision

### Control/Status Register 0 (CSR0)

Control/Status Register 0 is a read/write hardware word at offset \$0004. It contains several flags and bit fields which indicate and control various overall aspects of board operation. Perhaps most importantly, this register controls the general operating mode of the entire board. Like all hardware registers, this register is always valid and available to the host. Table 3-4 details this register's bit map.

| Control/Status Register 0 (Offset \$0004) Read/Write Hardware, Word |                                                                                                                 |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Bit 15                                                              | Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 09         Bit 08 |  |  |  |  |  |  |  |  |

| Reserved                                                            |                                                                                                                 |  |  |  |  |  |  |  |  |

| ар |

|----|

| a  |

| Bit 07  | Bit 06 | Bit 05            | Bit 04           | Bit 03             | Bit 02   | Bit 01   | Bit 00   |

|---------|--------|-------------------|------------------|--------------------|----------|----------|----------|

| LED Off | Halt   | Hardware<br>Reset | Memory<br>Enable | Board Not<br>Ready | OpMode 2 | OpMode 1 | OpMode 0 |

Power-up/Reset Default = \$XX00

|         | Controvolatus Register o Dit Deminions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 07: | <b>LED Off</b> - A logical "1" written to this bit location causes the front<br>panel status LED to turn off. A logical "0" written to this bit location<br>causes the front panel status LED to be turned on. (Default is<br>logic "0").                                                                                                                                                                                                                                                                                                       |

| Bit 06: | <b>Halt</b> - A logical "1" written to this write-only bit stops data<br>conversion and returns the board to IDLE mode. After issuing a halt,<br>host software should poll the OpMode bits (described below) and<br>wait until they are all clear (indicating IDLE mode) before<br>proceeding. At that time, the Halt bit is also cleared. It should not<br>take the board longer than 5 msec to return to IDLE mode after Halt is<br>set. If a "1" is written to this bit when the board is in IDLE mode, the<br>Halt bit will not be cleared. |

| Bit 05: | Hardware Reset - A logical "1" written to this write-only bit performs<br>a total hardware reset of the board. All power-up functions are<br>performed, just as if the VMEbus SYSRESET had been toggled. After<br>issuing a hardware reset, host software should poll the Board Not<br>Ready bit (described below) to determine when the reset has<br>completed. Reset should not take more than 5 msec.                                                                                                                                        |

| Bit 04: | <b>Memory Enable</b> - A logical "1" written to this bit location will enable<br>the DRAM buffer to become available. A logical "0" written to this bit<br>location causes the DRAM buffer to be disabled to host VMEbus<br>accesses. When disabled, VMEbus accesses to the DRAM area will<br>not DTACK*. Turning this bit on/off does not affect the DRAM<br>address/data.                                                                                                                                                                     |

| Bit 03: | <b>Board Not Ready</b> - This is a read-only status bit which indicates the VMIVME-3123 is powered up and ready to respond to the host. A logical "1" indicates the board is not ready to respond to host accesses. After the on-board DSP has powered-up and initialized, it will clear this bit to a logic "0".                                                                                                                                                                                                                               |

Control/Status Register 0 Bit Definitions

#### Control/Status Register 0 Bit Definitions (Continued)

**Bits 02 through 00: OpMode [2:0]** - Operating Mode control bits. Write a value to this field to place the VMIVME-3123 into the desired operating mode according to Table 3-5. Note that in any operating mode except IDLE, these mode bits are read-only, indicating the current mode. Refer to Operating Modes below for a more detailed discussion of the operating modes.

**NOTE:** All other applicable registers must be programmed prior to entering the desired operation mode.

| Operating Mode and Number | OpMode2 | OpMode1 | OpMode0 | Operating Mode<br>and Number |

|---------------------------|---------|---------|---------|------------------------------|

| IDLE                      | 0       | 0       | 0       | 0                            |

| Transient Capture         | 1       | 0       | 0       | 1                            |

| Continuous Sample         | 2       | 0       | 1       | 0                            |

| Reserved                  | 3       | 0       | 1       | 1                            |

| Calibration               | 4       | 1       | 0       | 0                            |

| Self-Test                 | 5       | 1       | 0       | 1                            |

| Reserved                  | 6       | 1       | 1       | 0                            |

| Reserved                  | 7       | 1       | 1       | 1                            |

#### **Operating Mode Descriptions**

**IDLE (Mode 0)** - IDLE mode is the power-up/reset default mode and is the only mode in which firmware registers can be accessed. IDLE mode is used by the host for configuration of the other registers prior to commanding the board to run in one of the functional modes. After completing a functional mode, hardware reset or halt, the board returns to IDLE mode without disturbing the other registers contents. Note that unlike the other modes, the user should never attempt to enter IDLE mode by writing to these mode bits. Use the Halt bit instead, and poll the mode bits. The mode bits will all be clear when IDLE mode is achieved.

**Transient Capture (Mode 1)** - Transient Capture mode is generally used to capture a transient event. In this mode, the board looks for a trigger marking an event (pre-programmed according to the Trigger Configuration Register and related registers), fills the DRAM sample buffer, and then returns to IDLE mode.

**Continuous Sample (Mode 2)** - Continuous Sampling mode is used when the host wants to collect a continuous stream of data. The data is stored in the DRAM buffer sequentially and the buffer rolls over when full (that is, the data buffer becomes a continuous ring buffer).

**Calibration (Mode 4)** - Calibration mode is used to generate the gain and offset correction values for the board. A board calibration is **NOT** performed on power-up. The user may perform calibration after power-up (from IDLE mode) or download pre-determined gain and offset values into DSP memory.

**Self-Test (Mode 5)** - Self-Test mode performs the selected tests in the Test Select/ Status Register and stores the results in the status portion of the same register.

Reserved Modes (Modes 3, 6 & 7) - These modes are reserved for future expansion.

### Control/Status Register 1(CSR1)

Control/Status Register 1 is a read/write hardware word at offset \$0006. It contains several flags and bit fields which indicate and control various overall aspects of board operation, especially regarding interrupts and sample triggering. Like all hardware registers, this register is always valid and available to the host. Table 3-6 details this register's bit map.

| Control/Status Register 1 (Offset \$0006) Read/Write, Hardware, Word |        |        |        |        |        |        |        |  |

|----------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--|

| Bit 15                                                               | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 09 | Bit 08 |  |

| Reserved                                                             |        |        |        |        |        |        |        |  |

| Table 3-6 | Control/Status | Register 1 | Bit Map |

|-----------|----------------|------------|---------|

|-----------|----------------|------------|---------|

| Bit 07                     | Bit 06      | Bit 05                 | Bit 04      | Bit 03      | Bit 02               | Bit 01               | Bit 00               |

|----------------------------|-------------|------------------------|-------------|-------------|----------------------|----------------------|----------------------|

| Filling<br>Upper<br>Buffer | I/O Trigger | I/O<br>Sample<br>Clock | Interrupt B | Interrupt A | Interrupt<br>Level 2 | Interrupt<br>Level 1 | Interrupt<br>Level 0 |

Power-up/Reset Default = \$XX00

|         | <u>controlled to gitter i pit pointtone</u>                                                                                                                                                                                                                                                                                                                                                                                |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 07: | <b>Filling Upper Buffer</b> - This read only bit indicates which buffer is<br>presently being filled. A logical "0" indicates the lower-half of the<br>DRAM data buffer is being filled and a logical "1" indicates that the<br>upper-half is being filled. This bit is meant to be used with<br>Continuous Sample mode only.                                                                                              |

| Bit 06: | <b>I/O Trigger</b> - A logical "1" written to this write only bit causes a trigger strobe to occur when the I/O Trigger source is selected in the Trigger Configuration register.                                                                                                                                                                                                                                          |

| Bit 05: | <b>I/O Sample CLK</b> - A logical "1" written to this write only bit creates a sample clock strobe to occur when the I/O Sample Clk source is selected in the Trigger Configuration Register.                                                                                                                                                                                                                              |

| Bit 04: | <b>Interrupt B</b> - This read only bit is used to indicate when the DSP has filled the data buffer during Continuous Sample mode as well as other functions. An interrupt will be generated if enabled. If interrupts are disabled this bit can be used in a polling manner to determine when the data buffer is full. A read of CSR1 will clear this bit. The following lists the functions that generate a B interrupt: |

|         | a. Transient Capture Mode - data buffer full, mode completed                                                                                                                                                                                                                                                                                                                                                               |

|         | b. Continuous Sample Mode - data buffer is full                                                                                                                                                                                                                                                                                                                                                                            |

|         | c. Calibration mode - Calibration completed, mode completed                                                                                                                                                                                                                                                                                                                                                                |

|         | d. Self-Test Mode - Self-Test complete, mode completed                                                                                                                                                                                                                                                                                                                                                                     |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                            |

### Control/Status Register 1 Bit Definitions

#### **Control/Status Register 1 Bit Definitions (Continued)**

Bit 03:

**Interrupt A** - This read only bit is used to indicate the following:

- a. Transient Capture Mode data buffer full, mode completed

- b. Continuous Sample Mode data buffer is half-full

- c. Calibration Mode Calibration completed, mode completed

- d. Self-Test Mode Self-Test complete, mode completed

As with interrupt B, this bit can be used to generate an interrupt or it can be polled by the host. A read of CSR1 will clear this bit.

**Bits 02 through 00:** Interrupt Level - Interrupt Level configuration bits. (Default is logic \$000). This field is used to select the VMEbus interrupt request level as shown below:

| VMEbus Interrupt Level | Interrupt Level 2 | Interrupt Level 1 | Interrupt Level<br>0 |

|------------------------|-------------------|-------------------|----------------------|

| Disable Interrupts     | 0                 | 0                 | 0                    |

| IRQ 1                  | 0                 | 0                 | 1                    |

| IRQ 2                  | 0                 | 1                 | 0                    |

| IRQ 3                  | 0                 | 1                 | 1                    |