## VMIVME-3126

## HIGH RESOLUTION, ISOLATED ANALOG-TO-DIGITAL CONVERTER BOARD

#### PRODUCT MANUAL

DOCUMENT NO. 500-003126-000 B

Revised July 30, 1997

VME MICROSYSTEMS INTERNATIONAL CORPORATION 12090 SOUTH MEMORIAL PARKWAY HUNTSVILLE, ALABAMA 35803-3308 (205) 880-0444 (800) 322-3616 FAX NO.: (205) 882-0859

#### COPYRIGHT AND TRADEMARKS

© Copyright January 1996. The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

AMXbus™, BITMODULE™, COSMODULE™, DMAbus™, IOWorks™, IOWorks Access™, IOWorks Foundation™, IOWorks man figure™, IOWorks Manager™, IOWorks Server™, MAGICWARE™, MEGAMODULE™, PLC ACCELERATOR (ACCELERATION)™, Quick Link™, RTnet™, Soft Logic Link™, SRTbus™, TESTCAL™, "The Next Generation PLC™M, The PLC Connection™, TURBOMODULE™, UCLIO™, UIOD™, UPLC™, Visual IOWorks™, Visual Soft Logic Control(ler)™, VMEaccess™, VMEmanager™, VMEmonitor™, VMEnet™, VMEnet II™, and VMEprobe™ are trademarks of VME Microsystems International Corporation.

(I/O man figure)

**UIOC®**

The I/O man figure, UIOC®, the VMIC logo, and WinUIOC® are registered trademarks of VME Microsystems International Corporation.

WinUIOC®

Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, and XENIX are registered trademarks and Windows NT is a trademark of Microsoft Corporation.

MMX is a trademark and Pentium is a registered trademark of Intel Corporation.

Other registered trademarks are the property of their respective owners.

#### VME Microsystems International Corporation All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless granted express written permission from VMIC.

## RECORD OF REVISIONS

| REVISION<br>LETTER | DATE                                             | PAGES INVOLVED                         | CHANG   | GE NUMBE |

|--------------------|--------------------------------------------------|----------------------------------------|---------|----------|

| Α                  | 04/11/96                                         | Release                                | 96-0    | 265      |

| В                  | 07/30/97                                         | Cover, Pages ii, and 4-10 through 4-12 | 97-0    | )555     |

|                    |                                                  |                                        |         |          |

|                    |                                                  |                                        |         |          |

|                    |                                                  |                                        |         |          |

|                    |                                                  |                                        |         |          |

|                    |                                                  |                                        |         |          |

|                    |                                                  |                                        |         |          |

|                    |                                                  |                                        |         |          |

|                    |                                                  |                                        |         |          |

|                    |                                                  |                                        |         |          |

|                    |                                                  |                                        |         |          |

|                    |                                                  |                                        |         |          |

|                    |                                                  |                                        |         |          |

| 00 South Memo      | TEMS INT'L C<br>orial Parkway<br>03-3308 • (205) | DOC NO 500-003126-000                  | REV LTR | PAGE NO  |

## VMIC SAFETY SUMMARY

THE FOLLOWING GENERAL SAFETY PRECAUTIONS MUST BE OBSERVED DURING ALL PHASES OF THE OPERATION, SERVICE, AND REPAIR OF THIS PRODUCT. FAILURE TO COMPLY WITH THESE PRECAUTIONS OR WITH SPECIFIC WARNINGS ELSEWHERE IN THIS MANUAL VIOLATES SAFETY STANDARDS OF DESIGN, MANUFACTURE, AND INTENDED USE OF THIS PRODUCT. VME MICROSYSTEMS INTERNATIONAL CORPORATION ASSUMES NO LIABILITY FOR THE CUSTOMER'S FAILURE TO COMPLY WITH THESE REQUIREMENTS.

#### GROUND THE SYSTEM

To minimize shock hazard, the chassis and system cabinet must be connected to an electrical ground. A three-conductor AC power cable should be used. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet.

## DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE

Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.

#### KEEP AWAY FROM LIVE CIRCUITS

Operating personnel must not remove product covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### DO NOT SERVICE OR ADJUST ALONE

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

## DO NOT SUBSTITUTE PARTS OR MODIFY SYSTEM

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to VME Microsystems International Corporation for service and repair to ensure that safety features are maintained.

## DANGEROUS PROCEDURE WARNINGS

Warnings, such as the example below, precede only potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

WARNING

DANGEROUS VOLTAGES, CAPABLE OF CAUSING DEATH, ARE PRESENT IN THIS SYSTEM. USE EXTREME CAUTION WHEN HANDLING, TESTING, AND ADJUSTING.

## SAFETY SYMBOLS

# GENERAL DEFINITIONS OF SAFETY SYMBOLS USED IN THIS MANUAL Instruction manual symbol: the product is marked with this symbol when in

4

Instruction manual symbol: the product is marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect against damage to the system.

Indicates dangerous voltage (terminals fed from the interior by voltage exceeding 1000 volts are so marked).

Protective conductor terminal. For protection against electrical shock in case of a fault. Used with field wiring terminals to indicate the terminal which must be connected to ground before operating equipment.

Low-noise or noiseless, clean ground (earth) terminal. Used for a signal common, as well as providing protection against electrical shock in case of a fault. Before operating the equipment, terminal marked with this symbol must be connected to ground in the manner described in the installation (operation) manual.

Frame or chassis terminal. A connection to the frame (chassis) of the equipment which normally includes all exposed metal structures.

Alternating current (power line).

\_\_\_

Direct current (power line).

Alternating or direct current (power line).

The WARNING sign denotes a hazard. It calls attention to a procedure, a practice, a condition, or the like, which, if not correctly performed or adhered to, could result in injury or death to personnel.

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, a practice, a condition, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the system.

NOTE:

The NOTE sign denotes important information. It calls attention to a procedure, a practice, a condition or the like, which is essential to highlight.

## VMIVME-3126

## HIGH RESOLUTION, ISOLATED ANALOG-TO-DIGITAL CONVERTER BOARD

## TABLE OF CONTENTS

|            |                      |                                | Page               |

|------------|----------------------|--------------------------------|--------------------|

| SECTIO     | N 1.                 | INTRODUCTION                   |                    |

| 1.1<br>1.2 | FEATUR<br>REFERE     | RES                            |                    |

| SECTIO     | N 2.                 | PHYSICAL DESCRIPTION AND SPE   | ECIFICATIONS       |

| SECTIO     | N 3.                 | THEORY OF OPERATION            |                    |

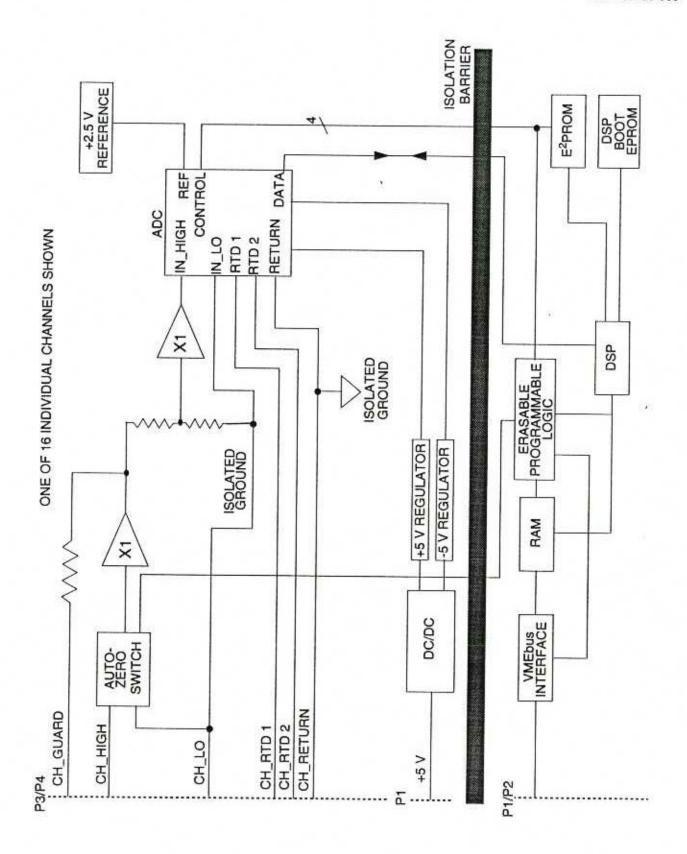

| 3.1        | INTROD               | UCTION                         | 3-1                |

| 3.2        | VMFbus               | INTERFACE                      | 2.1                |

| 3.2.1      | Control a            | and Status Registers (CSRs)    | 2.1                |

| 3.2.2      | Data Rec             | gisters                        | 2.1                |

| 3.2.3      | Modes of             | Operation                      | 2.2                |

| 3.2.4      | Normal M             | Mode                           | 2.0                |

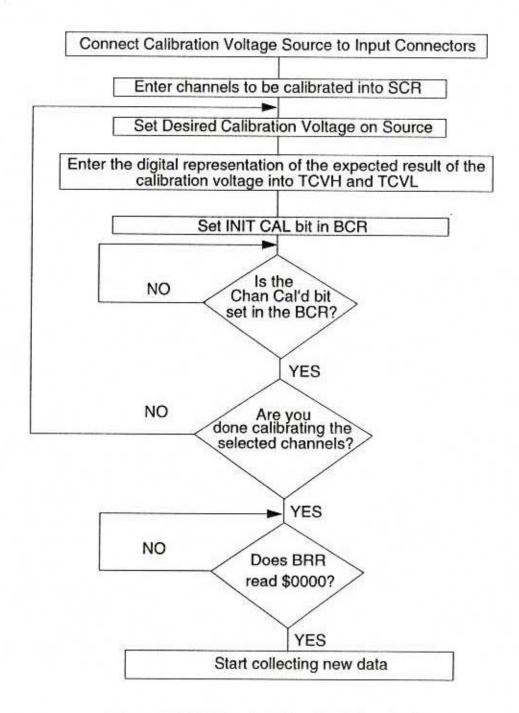

| 3.2.5      | Calibratio           | on Mode                        | 2.2                |

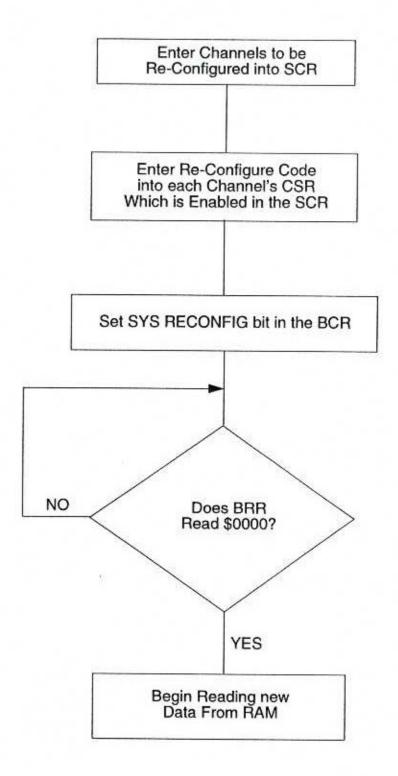

| 3.2.6      | Reconfig             | uration Mode                   | 3.4                |

| 3.2.7      | Autozero             | Mode                           | 2.5                |

| 3.3        | DIGITAL              | SIGNAL PROCESSOR (DSP)         | 2.5                |

| 3.4        | ELECTR               | ICALLY PROGRAMMABLE READ-ONLY  | MEMORY (EPROM) 3.8 |

| 3.5        | ELECTR               | ICALLY ERASABLE PROGRAMMABLE R | FAD-ONLY MEMORY    |

|            | (E <sup>2</sup> PROM | M),                            | 2-8                |

| 3.6        | CONTRO               | LOGIC                          | 3.0                |

| 3.7        | ANALOG               | INPUTS                         | 2-8                |

| 3.7.1      | Analog-to            | p-Digital Converter (ADC)      | 3.0                |

| 3.7.1.1    | ADC Con              | trol Interface                 | 3-0                |

| 3.7.1.2    | Programm             | nable Gain Amplifier (PGA)     | 3-0                |

| 3.7.2      | RTD Exc              | tation                         | 3-0                |

| 3.7.3      | Open Tra             | nsducer Detection              | 3-10               |

| 3.7.4      | Filtering .          |                                | 3-10               |

| 3.7.5      | OPTO Iso             | plation                        | 3-10               |

| 3.7.6      | DC-to-DC             | Power Converters               | 3-10               |

| 3.7.7      | Current L            | oop Termination Option         | 3-11               |

| 3.7.8      | Increased            | Input Voltage Range Option     | 3-11               |

|            |                      |                                |                    |

## TABLE OF CONTENTS (CONTINUED)

|        |            |                           |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page |

|--------|------------|---------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| SECTIO | ON 4.      | PROGRAMMING               |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 4.1    | INTROD     | JCTION                    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-1  |

| 4.2    | GENERA     | L CONTROL FEATUR          | RES             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-1  |

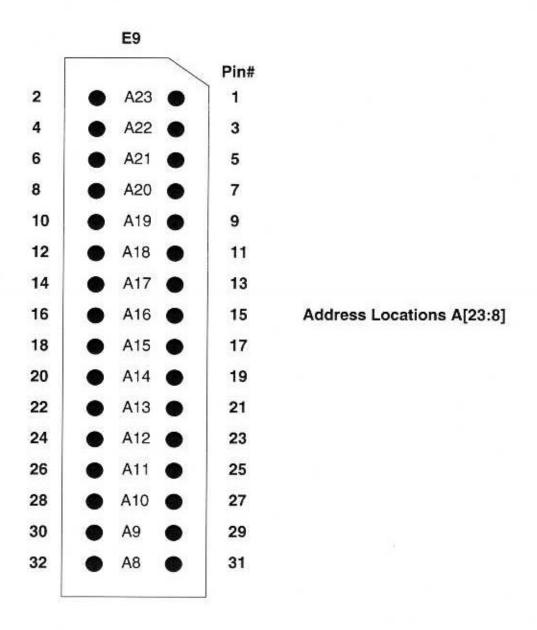

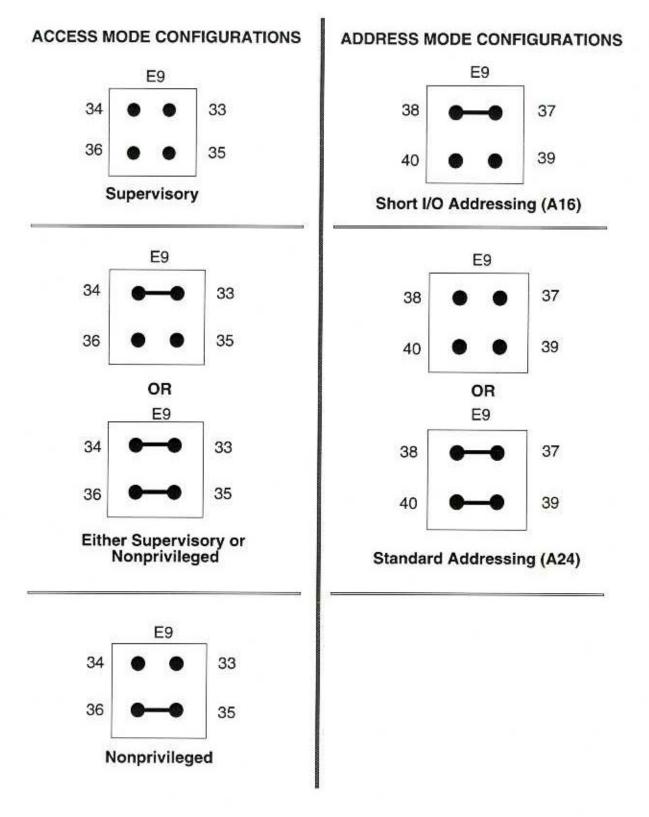

| 4.2.1  | Addressi   | ng Modes and Board L      | ocations        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-1  |

| 4.2.2  | Data Tra   | nsfers                    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-1  |

| 4.2.3  | Reset Op   | erations and Initializat  | ion             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-2  |

| 4.3    | CONTRO     | L REGISTERS               |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-2  |

| 4.3.1  | Board Ide  | entification Register (Bl | R)              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-3  |

| 4.3.2  | Board Re   | ady Register (BRR) .      |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-3  |

| 4.3.3  | Board Co   | ntrol Register (BCR).     |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-4  |

| 4.3.4  | Select Ch  | annel Register (SCR)      |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-6  |

| 4.3.5  | Channel    | Pass/Fail Status Regis    | ter (PFS)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-7  |

| 4.3.6  | Target Ca  | libration Voltage Regi    | ster (TVC)      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-7  |

| 4.3.7  | Firmware   | Revision Register (FR     | (R)             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-9  |

| 4.3.8  | EEPROM     | Writes Registers (ÈW      | R1 and EWR0)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-9  |

| 4.3.9  | Control a  | nd Status Register (Ch    | annel 0 Example | e)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-10 |

| 4.3.10 | Offset Co  | efficients                |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-12 |

| 4.3.11 | Gain Coe   | fficients                 |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-12 |

| 4.3.12 | Data Reg   | ister                     |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-12 |

| SECTIO | N 5.       | CONFIGURATION             | AND INSTALL     | ATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| 5.1    | LINDACK    | NG PROCEDURES             |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

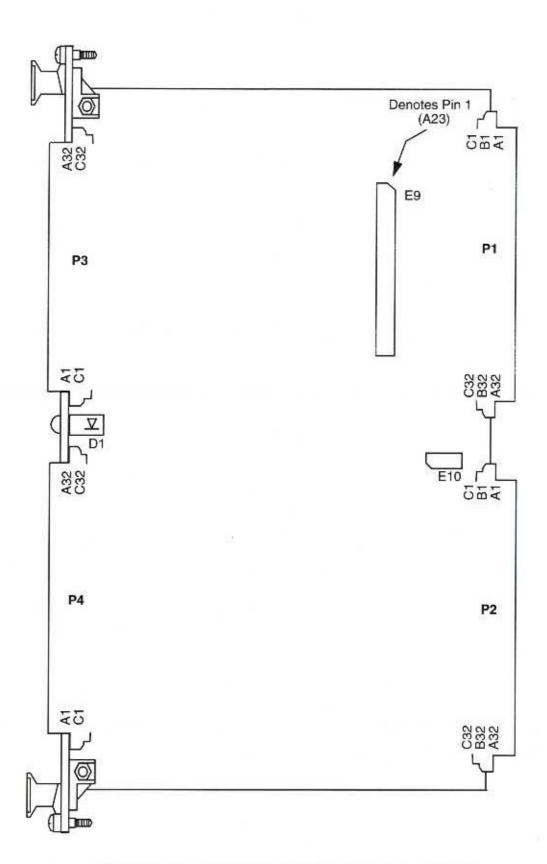

| 5.2    | PHYSICA    | L INSTALLATION            |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 5.3    | BASE AD    | DRESS CONFIGURA           | TION            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-1  |

| 5.4    | LIIOC IIII | MPER                      | 110N            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-1  |

| 5.5    | SYSTEM     | CONNECTIONS               |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 5.6    | CALIBBA    | TION                      |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 5.7    | BTD APP    | LICATIONS AND CON         | IFIGURATIONS    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 5.7.1  | Three-Wii  | e RTD Configuration .     | II IGOTIATIONS  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-0  |

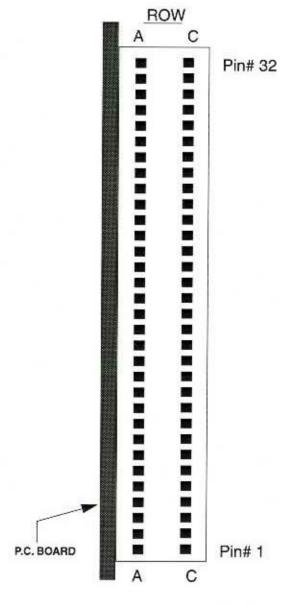

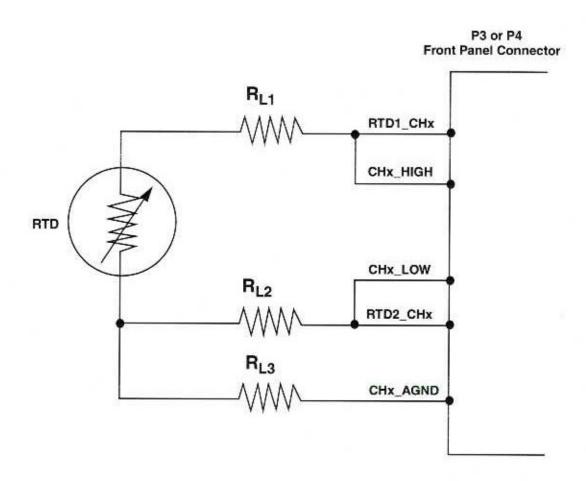

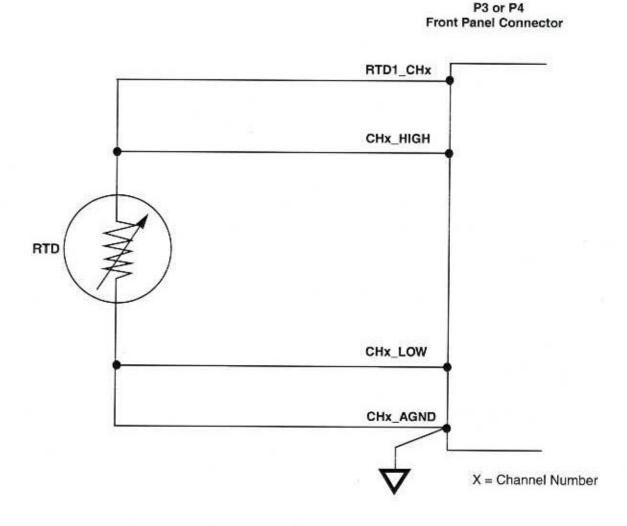

| 5.7.2  | Four-Wire  | RTD Configuration         |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-9  |