# VMIVME-4905 Digital-to-Synchro/Resolver Converter Board

**Product Manual**

A GE Fanuc Company

#### COPYRIGHT AND TRADEMARKS

© Copyright 2002. The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

AMXbus, BITMODULE, COSMODULE, DMAbus, IOMax, IOWorks Foundation, IOWorks Manager, IOWorks Server, MAGICWARE, MEGAMODULE, PLC ACCELERATOR (ACCELERATION), Quick Link, RTnet, Soft Logic Link, SRTbus, TESTCAL, "The Next Generation PLC", The PLC Connection, TURBOMODULE, UCLIO, UIOD, UPLC, Visual Soft Logic Control(ler), *VMEaccess*, VMEbus Access, *VMEmanager*, *VMEmonitor*, VMEnet, VMEnet II, and *VMEprobe* are trademarks and The I/O Experts, The I/O Systems Experts, The Soft Logic Experts, and The Total Solutions Provider are service marks of VMIC.

The I/O man figure, IOWorks, IOWorks man figure, UIOC, Visual IOWorks and the VMIC logo are registered trademarks of VMIC.

ActiveX, Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, Windows NT, and XENIX are registered trademarks of Microsoft Corporation.

MMX is trademarked, Celeron, Intel and Pentium are registered trademarks of Intel Corporation.

PICMG and CompactPCI are registered trademarks of PCI Industrial Computer Manufacturers' Group.

Other registered trademarks are the property of their respective owners.

#### **VMIC**

#### All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless granted express written permission from VMIC.

A GE Fanuc Company

# **Table of Contents**

| Dverview 1   Functional Description 1   Reference Material List 1   Safety Summary 1   Ground the System 1   Do Not Operate in an Explosive Atmosphere 1   Keep Away from Live Circuits 1   Do Not Service or Adjust Alone 1   Do Not Substitute Parts or Modify System 1 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Functional Description                                                                                                                                                                                                                                                    | 9  |

| Reference Material List                                                                                                                                                                                                                                                   | 11 |

| Safety Summary                                                                                                                                                                                                                                                            | 12 |

| Ground the System                                                                                                                                                                                                                                                         | 13 |

| Do Not Operate in an Explosive Atmosphere                                                                                                                                                                                                                                 | 14 |

| Keep Away from Live Circuits    1      Do Not Service or Adjust Alone    1                                                                                                                                                                                                | 14 |

| Do Not Service or Adjust Alone                                                                                                                                                                                                                                            | 14 |

| ·                                                                                                                                                                                                                                                                         | 14 |

| Do Not Substitute Parts or Modify System                                                                                                                                                                                                                                  | 14 |

|                                                                                                                                                                                                                                                                           | 14 |

| Dangerous Procedure Warnings                                                                                                                                                                                                                                              | 14 |

| Safety Symbols Used in This Manual1                                                                                                                                                                                                                                       | 15 |

| Chapter 1 - Theory of Operation                                                                                                                                                                                                                                           | 17 |

| Functional Operation                                                                                                                                                                                                                                                      | 17 |

| Address Decode Logic                                                                                                                                                                                                                                                      | 19 |

| VMEbus Foundation Logic                                                                                                                                                                                                                                                   | 20 |

| Output Data and Control Registers                                                                                                                                                                                                                                         | 21 |

| Digital-to-Synchro/Resolver Modules                                                                                                                                                                                                                                       | 22 |

| Built-in-Test Hardware Operation                                                                                                                                                                                                                                          | 23 |

| Output Relay Control                                                                                                                                                                                                                                                      | 28 |

| Power Connections                                                                                                                                                                                                                                                         | 29 |

| 5-Volt/Ampere Drive Option                                                                                                                                                                                                                                                | 30 |

| 2-Volt/Ampere Output Isolation Transformer Option                                                                                                                                                                                                                         | 31 |

| Chapter 2 - Configuration and Installation                 | <br>33   |

|------------------------------------------------------------|----------|

| Unpacking Procedures                                       | <br>. 34 |

| Connector and Jumper/Configuration                         | <br>. 35 |

| Built-in-Test Output Configuration                         | <br>. 41 |

| Hardware Connection to Synchro or Resolver                 | <br>. 42 |

| Built-in-Test Configuration with Synchro/Resolver Test Bus | <br>. 43 |

| Address Modifiers                                          | <br>. 44 |

| Address Selection Switches                                 | <br>. 45 |

| Calibration of High Drive Capability Boards                | <br>. 46 |

| Channel Zero                                               | <br>. 46 |

| Channel One                                                | <br>. 46 |

| Chapter 3 - Programming                                    | <br>49   |

| Built-in-Test Configuration with Synchro/Resolver Test Bus | <br>. 52 |

| Built-in-Test Output Configuration                         | <br>. 52 |

| Maintenance                                                | <br>. 53 |

| Maintenance                                                | <br>. 53 |

| Maintenance Prints                                         | 54       |

# List of Figures

| Figure 1    | Synchro/Resolver Test Subsystem (On-Line and Off-Line Testing)   | 12 |

|-------------|------------------------------------------------------------------|----|

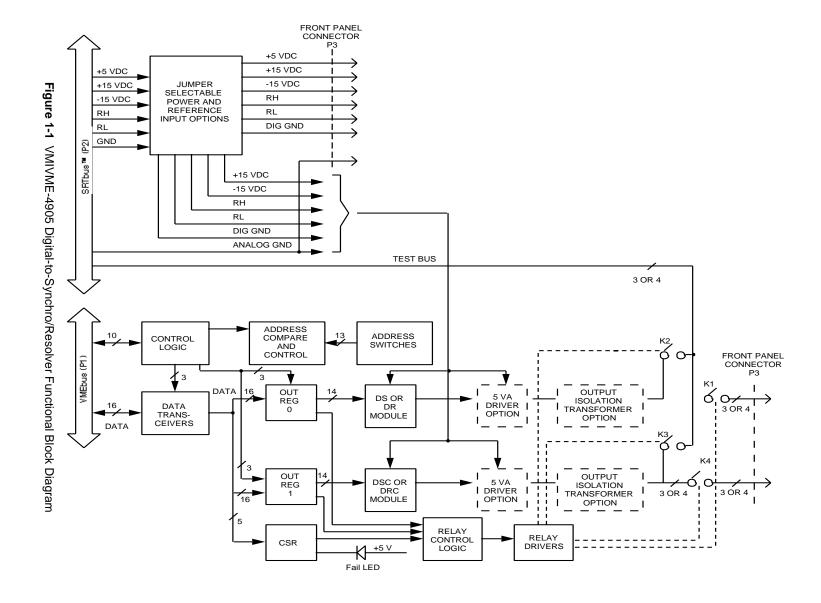

| Figure 1-1  | VMIVME-4905 Digital-to-Synchro/Resolver Functional Block Diagram | 18 |

| Figure 1-2  | Address Compare Functional Block Diagram                         | 19 |

| Figure 1-3  | VMEbus Foundation Logic Block Diagram                            | 20 |

| Figure 1-4  | Output Data and Control Registers Block Diagram                  | 21 |

| Figure 1-5  | Digital-to-Synchro/Resolver Block Diagram                        | 22 |

| Figure 1-6  | Built-in-Test Subsystem Configuration                            | 24 |

| Figure 1-7  | Expanded Synchro/Resolver Subsystem with Built-in-Test           | 25 |

| Figure 1-8  | Quad Channel DSC/DRC Board VMIVME-4911 Functional Block Diagram  | 26 |

| Figure 1-9  | VMIVME-4910 Functional Block Diagram                             | 27 |

| Figure 1-10 | Synchro/Resolver Output Functional Block Diagram                 | 28 |

| Figure 1-11 | Power Connection Block Diagram                                   | 29 |

| Figure 2-1  | Switch and Jumper Locations                                      | 39 |

| Figure 2-2  | Base Address Switches                                            | 45 |

# List of Tables

| Table 2-1 | P2, P3 Pinout                           | 36 |

|-----------|-----------------------------------------|----|

| Table 2-2 | Jumper Factory Configuration            | 37 |

| Table 2-3 | Jumper Configuration                    | 38 |

| Table 2-4 | Installation Table of Reference Voltage | 40 |

| Table 2-5 | Relay Functions**                       | 41 |

| Table 3-1 | Data Input Word: Bit Weights            | 50 |

| Table 3-2 | Address Map and Register Bit Formats    | 51 |

| Table 3-3 | Relay Functions                         | 52 |

# **Overview**

#### Introduction

The VMIVME-4905 board is a VMEbus compatible Digital-to-Synchro/Resolver Converter (DSC/DRC) Board that utilizes either one or two digital-to-synchro/resolver converters, depending upon the option chosen. The primary features are:

- Synchro or resolver outputs

- .024 or 5.0 VA options

- 2.0 VA with output transformer option

- One or two DSC/DRCs

- 14-bit converter with an accuracy as high as  $\pm 1$  ARC minute ( $\pm 4$  ARC minute is standard)

- 8- or 16-bit VMEbus data transfers

- Front panel Fail LED

- 115 Vrms or 26 Vrms reference excitation voltage\*

- Built-in-test features

- Supports off-line and on-line fault detection and isolation

- Compatible with Intelligent I/O Controllers (IIOCs)

**NOTE**: \*Consult the factory for other options

# **Functional Description**

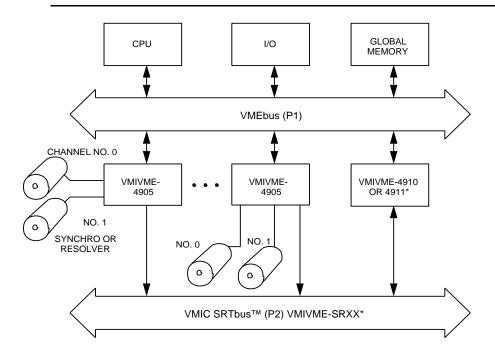

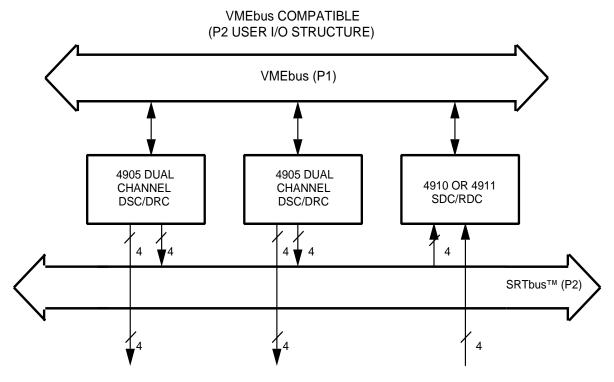

The DSC/DRC board is based on the NATEL HSDR 2514 converter module. The board supports a wide variety of options which are supported by configuring jumpers on the basic printed circuit board and by the installation of optional components. The options are listed in the Product Specification. The 4905 Board, with supporting Built-in-Test hardware, features both off-line and on-line fault detection and isolation. The Built-in-Test features require a VMIC Quad-Channel Synchro-to-Digital Converter (SDC) Board (VMIVME-4911) or a single-channel SDC Board (VMIVME-4910) and a standard synchro test backplane (SRTbus™) installed in the P2 position of a standard VMEbus chassis, as shown in Figure 1 below. The board accepts a 14-bit digital input word (shaft angle) and a reference excitation voltage, and produces a synchro or resolver output.

The DSC/DRC board is provided with several options and is capable of interfacing with most standard synchro or resolver devices. The board is ideally suited for computer-based systems in which digital information is processed, such as simulators, robotics, and other control-oriented systems. This product requires forced air cooling for the 5 volt amp (VA) option, and the 2.0 VA option with output isolation transformers.

**NOTE:** If this board is used with VMIC's intelligent I/O controller (IIOC) (VMIVME-9016), a quad-channel SDC board (VMIVME-4911) and a SRTbus<sup>TM</sup> is required for built-in-test. the IIOC firmware is not compatible with the VMIVME-4910.

\*VMIVME-4911 and SRTbus™ are required for use with the VMIVME-9016.

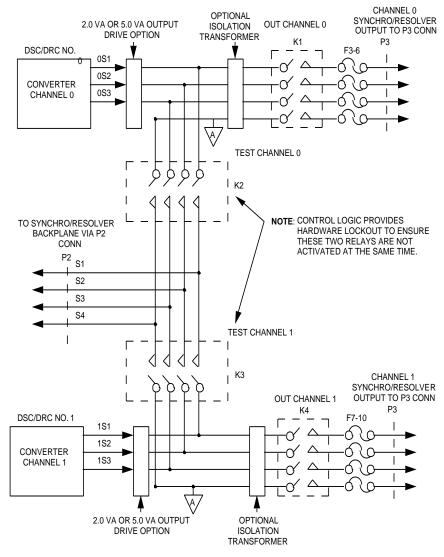

Figure 1 Synchro/Resolver Test Subsystem (On-Line and Off-Line Testing)

### **Reference Material List**

For a detailed description of the VMEbus, refer to *The VMEbus Specification and Handbook* available from:

VMEbus International Trade Association (VITA) 7825 Gelding Dr. Suite No. 104 Scottsdale, AZ 85620-3415 (602) 951-8866

Fax: (602) 951-0720 e-mail: info@vita.com Internet: www.vita.com

For detailed technical information concerning synchro/resolver theory, refer to the following source.

Synchro Conversion Handbook ILC Data Device Corporation 105 Wilbur Place Bohemia, New York 11716

The following application and configuration guides are available from VMIC to assist the user in the selection, specification, and implementation of systems based on VMIC's products.

| <u>Title</u>                                                                     | Document No.   |

|----------------------------------------------------------------------------------|----------------|

| Digital-to-Synchro/Resolver Converter Board Instruction Manual                   | 500-004905-000 |

| Synchro/Resolver-to-Digital Input Board with Built-in-Test<br>Instruction Manual | 500-004911-000 |

| Digital-to-Synchro/Resolver Converter Output Board Instruction<br>Manual         | 500-004900-000 |

| Synchro/Resolver (Built-in-Test) Subsystem Configuration Guide                   | 825-000000-004 |

| Digital Input Board Application Guide                                            | 825-000000-000 |

|                                                                                  |                |

| <u>Title</u>                                                                     | Document No.   |

| Change-of-State Application Guide                                                | 825-000000-002 |

| Digital I/O (with Built-in-Test) Product Line Description                        | 825-000000-003 |

| Analog I/O Products (with Built-in-Test) Configuration Guide                     | 825-000000-005 |

| Synchro/Resolver (Built-in-Test) Subsystem Configuration Guide                   | 825-000000-004 |

Physical Description and Specifications, refer to *Product Specification*, 800-004905-000 available from:

VMIC 12090 South Memorial Pkwy. Huntsville, AL 35803-3308, USA (256) 880-0444 (800) 322-3616 FAX: (256) 882-0859 www.vmic.com

Connector and I/O Cable Application Guide

825-000000-006

# **Safety Summary**

The following general safety precautions must be observed during all phases of the operation, service, and repair of this product. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of this product.

VMIC assumes no liability for the customer's failure to comply with these requirements.

#### **Ground the System**

To minimize shock hazard, the chassis and system cabinet must be connected to an electrical ground. A three-conductor AC power cable should be used. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet.

#### Do Not Operate in an Explosive Atmosphere

Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.

#### **Keep Away from Live Circuits**

Operating personnel must not remove product covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### Do Not Service or Adjust Alone

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### Do Not Substitute Parts or Modify System

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to VMIC for service and repair to ensure that safety features are maintained.

### **Dangerous Procedure Warnings**

Warnings, such as the example below, precede only potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

**STOP:** Dangerous voltages, capable of causing death, are present in this system. Use extreme caution when handling, testing, and adjusting.

# Safety Symbols Used in This Manual

**STOP:** This symbol informs the operator the that a practice or procedure should not be performed. Actions could result in injury or death to personnel, or could result in damage to or destruction of part or all of the system.

**WARNING:** This sign denotes a hazard. It calls attention to a procedure, a practice, a condition, which, if not correctly performed or adhered to, could result in injury or death to personnel.

**CAUTION:** This sign denotes a hazard. It calls attention to an operating procedure, a practice, or a condition, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the system.

**NOTE:** Calls attention to a procedure, a practice, a condition or the like, which is essential to highlight.

# Theory of Operation

#### **Contents**

| Address Decode Logic                              |

|---------------------------------------------------|

| VMEbus Foundation Logic                           |

| Output Data and Control Registers                 |

| Digital-to-Synchro/Resolver Modules               |

| Built-in-Test Hardware Operation                  |

| Output Relay Control                              |

| Power Connections                                 |

| 5-Volt/Ampere Drive Option                        |

| 2-Volt/Ampere Output Isolation Transformer Option |

#### Introduction

This section of the manual presents detailed information about the VMIVME-4905 Digital-to-Synchro/Resolver Converter (DSC/DRC) Board hardware operation. Information concerning programming is provided in Chapter 3.

#### **Functional Operation**

The VMIVME-4905 board design may be functionally divided into seven primary sections, as shown in the functional block diagram in Figure 1-1 on page 18. These primary functional sections are as follows:

- Address compare and control logic

- · VMEbus data transceivers

- · Output data and control registers

- Digital-to-synchro/resolver modules

- · Built-in-test bus

- Relay control

- Power connections

### **Address Decode Logic**

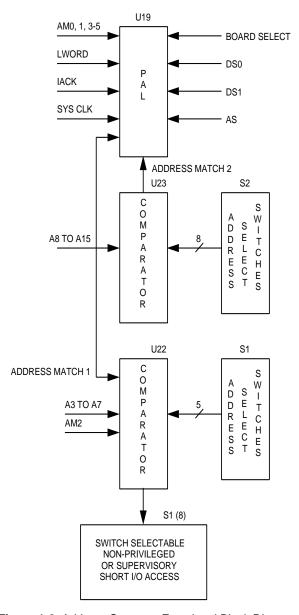

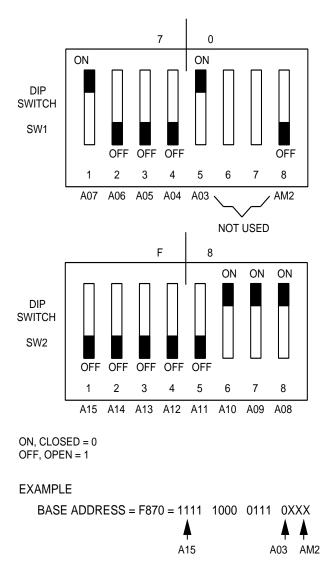

A functional block diagram of the address decode logic is shown in Figure 1-2 below. Two eight-position "DIP" switches are provided to enable the user to select from a wide range of short I/O memory addresses for the board address. The user may also select nonprivileged or supervisory short I/O transfers. The board is configured at the factory to respond to short supervisory I/O transfers.

Figure 1-2 Address Compare Functional Block Diagram

# **VMEbus Foundation Logic**

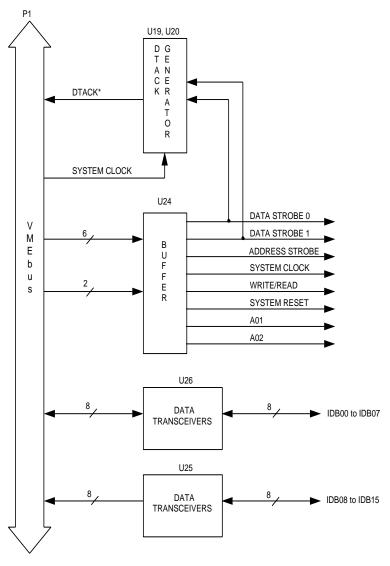

The DSC/DRC Board VMEbus foundation logic, shown in Figure 1-3 below, consists primarily of a DTACK generator, control signal buffers, and data transceivers. These transceivers buffer data to be transmitted to the output registers and to the Control and Status Register (CSR), which controls the front panel Fail LED and output isolation switches. The control logic is designed to support 8- and 16-bit transfers. Address bits A01 and A02 are decoded to select one of two output data registers and the CSR.

Figure 1-3 VMEbus Foundation Logic Block Diagram

# **Output Data and Control Registers**

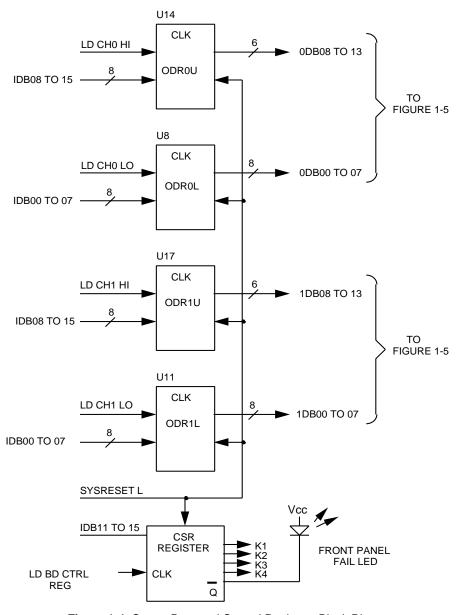

The DSC/DRC Board is designed with four 8-bit output data registers and a 5-bit CSR that controls the front panel Fail LED and relays for Built-in-Test, as shown in Figure 1-4 below. All registers are cleared at power-up by the VMEbus SYSRESET signal; therefore, all synchro/resolver outputs are disconnected from their loads, and the front panel Fail LED is illuminated at power-up.

Figure 1-4 Output Data and Control Registers Block Diagram

# 1

# **Digital-to-Synchro/Resolver Modules**

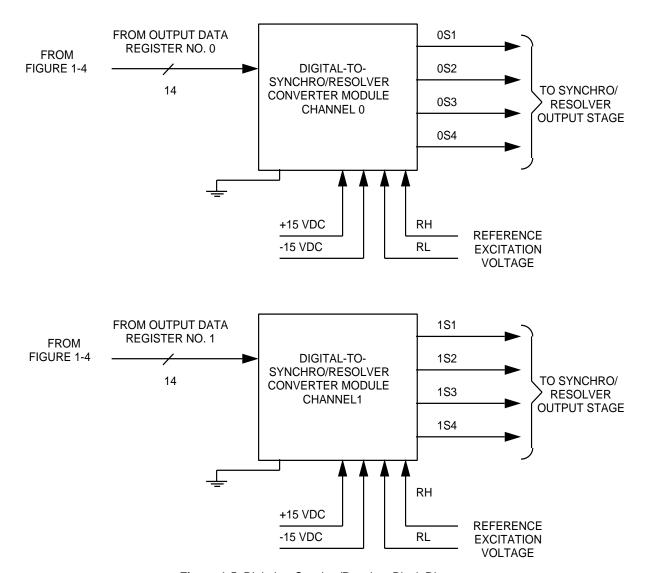

A functional block diagram of the synchro/resolver module is shown in Figure 1-5 below. The digital data provided as inputs to each module is stored in holding registers, as described in *Output Data and Control Registers* on page 21. VMIC selects from several vendors specific synchro/resolver modules that meet manufacturing options. The user should refer the Product Specification for a detailed explanation of available options.

Figure 1-5 Digital-to-Synchro/Resolver Block Diagram

#### **Built-in-Test Hardware Operation**

The DSC/DRC Board supports fault detection and isolation when used with the VMIC SRTbus<sup>TM</sup> and VMIC's models VMIVME-4910 or VMIVME-4911. The SRTbus<sup>TM</sup> is a synchro/resolver test bus that utilizes the user I/O pins on the P2 VMEbus connector. Programming the proper control bits in the CSR of the VMIVME-4905 Board allows field disconnect and/or real-time loopback testing via the SRTbus<sup>TM</sup> and the VMIVME-4910 or VMIVME-4911 Boards.

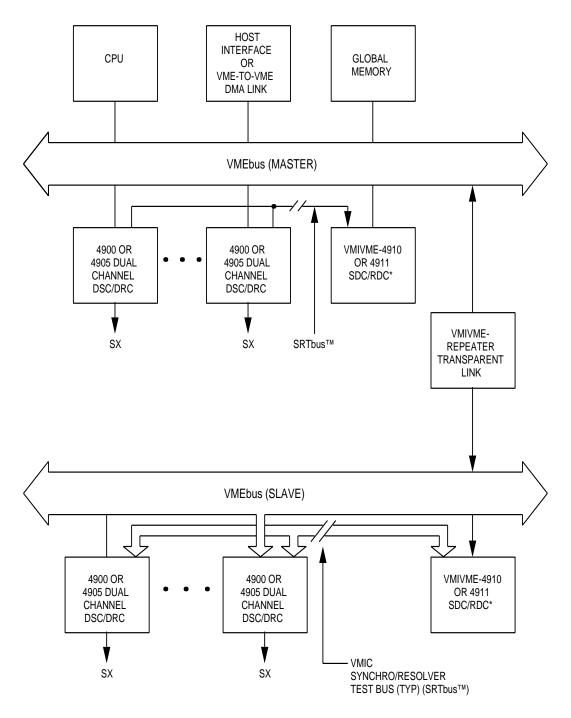

A typical VMIC DSC/DRC subsystem may be configured such that a VMIC P2 Synchro Backplane (SRTbus<sup>TM</sup>) is utilized for isolating failures to the board level. The DSC/DRC Built-in-Test subsystem is based on an individually switched DSC/DRC output to a shared DSC/DRC Board, as shown in Figure 1-6 on page 24. This subsystem may be economically expanded by utilizing the VME repeater link, as shown in Figure 1-7 on page 25.

Each DSC/DRC Board is designed to support both off-line and on-line fault detection and isolation by program control of two Built-in-Test output control switches. During off-line testing, synchro/resolver outputs are physically disconnected from the loads. Connection to the test backplane is electrically interlocked, such that no two synchro outputs can be connected to the backplane simultaneously.

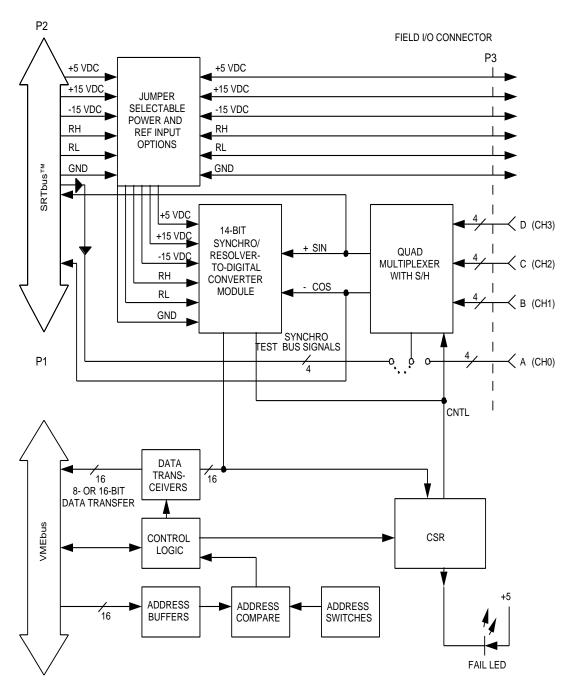

The VMIVME-4911 Quad SDC/RDC Board (Figure 1-8 on page 26) is utilized for fault detection and isolation of DSC/DRC Boards, and is based on an industry standard quad multiplexing Resolver/Synchro-to-Digital Converter (RDC/SDC) module. This high performance, fast settling, 14-bit SDC/RDC is required to support the real-time fault detection and isolation capabilities of the IIOC and the real-time synchro/resolver input data processing required in the simulation and training industry.

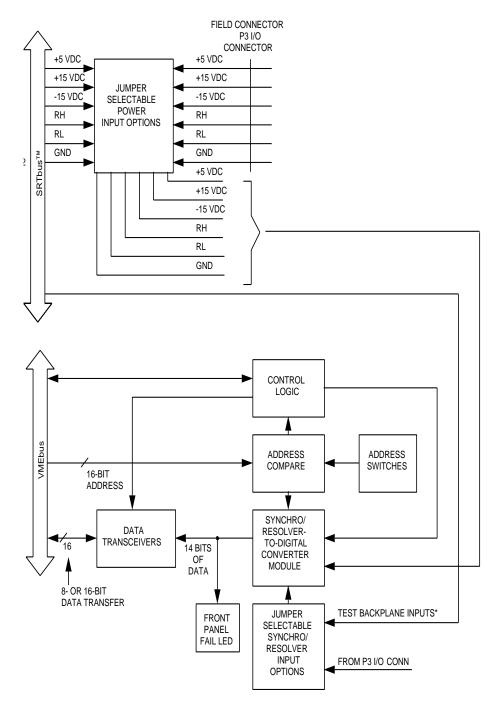

VMIC also produces a model VMIVME-4910 tracking DSC/DRC Board (Figure 1-9 on page 27) that supports fault detection and isolation. The VMIVME-4910 is a single-channel synchro/resolver input board that is designed with input data switching relays to support either inputs from field sources via the front panel connector or the P2 VMEbus connector. It is also designed to support loopback testing of VMIC's 49XX series DSC/DRC products. The worst-case settling time of the VMIVME-4910 may exceed 250 ms; therefore, it is not recommended for real-time data processing where update rates are in excess of the worst-case settling time. VMIC recommends the VMIVME-4911 Quad DSC/DRC Board for real-time simulation and training applications. This high-speed converter features simultaneous sampling and random access with a resolution of 14 bits and a 150 µs conversion time per channel.

\*If the 4905 is used with VMIC's VMIVME-9016, Intelligent I/O Controller (IIOC), the VMIVME-4911 and SRTbus™ must also be used. The IIOC firmware is not compatible with the VMIVME-4910.

Figure 1-6 Built-in-Test Subsystem Configuration

\*The 4911 is required with systems configured with VMIC's IIOC (VMIVME-9016).

Figure 1-7 Expanded Synchro/Resolver Subsystem with Built-in-Test

Figure 1-8 Quad Channel DSC/DRC Board VMIVME-4911 Functional Block Diagram

\*Used for fault isolation of VMIVME-49XX Series DSC/DRC Boards.

Figure 1-9 VMIVME-4910 Functional Block Diagram

### **Output Relay Control**

Four relays are provided to allow programmed field disconnect and to support real-time and off-line fault detection and isolation, as shown in Figure 1-10 below. The relays are controlled by the CSR, as described in *Output Data and Control Registers* on page 21. Relays K1 and K4 provide the field disconnect functions, whereas relays K2 and K3 provide the loopback testing hardware, as described in *Built-in-Test Hardware Operation* on page 23. Relay control logic for relays K2 and K3 is designed with a hardware interlock to preclude simultaneous energization. Each synchro/resolver output is fused at the immediate outputs of the synchro/resolver module for overcurrent protection.

Figure 1-10 Synchro/Resolver Output Functional Block Diagram

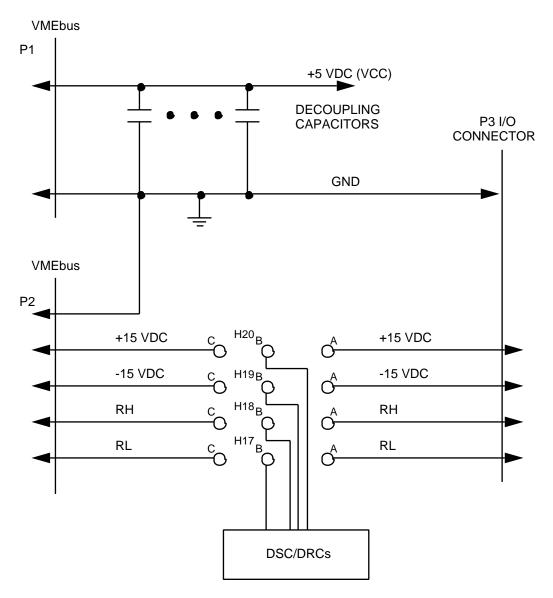

# **Power Connections**

The dual-channel DSC/DRC Board is designed to use three DC power supplies and one reference signal as shown in Figure 1-11 below. External ±15 VDC power supplies are required. The user should refer to Product Specification for power requirements as a function of options ordered. Jumpers are provided, as shown in Figure 1-11, to provide the user an option to select front panel or rear panel 15 VDC and reference inputs.

Figure 1-11 Power Connection Block Diagram

# 5-Volt/Ampere Drive Option

This option provides the capability of driving up to 5-volt/amperes of torque receiver(s) load. It is recommended that the processor know the approximate position of the torque receiver(s) before initiating an output to the board. Should the processor transfer an output word that results in overdriving the torque receiver(s), undesirable mechanical transients may result. The VMIVME-4905 5-volt/ampere option limits current transients to one ampere peak.

# 2-Volt/Ampere Output Isolation Transformer Option

This option provides the capability for driving up to 2-volt/amperes of torque receiver load. The VMIVME-4905 2-volt/ampere option limits current transients to 0.5 ampere peak.

# Configuration and Installation

#### **Contents**

| Unpacking Procedures 3                                       | 34 |

|--------------------------------------------------------------|----|

| Connector and Jumper/Configuration 3                         | 35 |

| Built-in-Test Output Configuration                           | 11 |

| Hardware Connection to Synchro or Resolver                   | 12 |

| Built-in-Test Configuration with Synchro/Resolver Test Bus 4 | 13 |

| Address Modifiers                                            | 14 |

| Address Selection Switches                                   | 15 |

| Calibration of High Drive Capability Boards 4                | 16 |

#### Introduction

This chapter describes the installation and configuration of the board. Cable configuration, jumper/switch configuration and board layout are illustrated in this chapter.

# **Unpacking Procedures**

**CAUTION:** Some of the components assembled on VMIC's products may be sensitive to electrostatic discharge and damage may occur on boards that are subjected to a high-energy electrostatic field. When the board is placed on a bench for configuring, etc., it is suggested that conductive material should be inserted under the board to provide a conductive shunt. Unused boards should be stored in the same protective boxes in which they were shipped.

Upon receipt, any precautions found in the shipping container should be observed. All items should be carefully unpacked and thoroughly inspected for damage that might have occurred during shipment. The board(s) should be checked for broken components, damaged printed circuit board(s), heat damage, and other visible contamination. All claims arising from shipping damage should be filed with the carrier and a complete report sent to VMIC together with a request for advice concerning the disposition of the damaged item(s).

# **Connector and Jumper/Configuration**

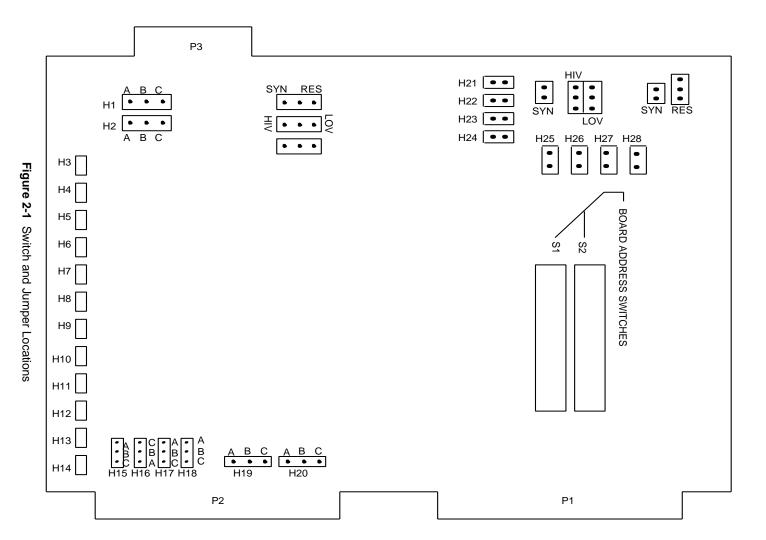

Pin functions for the P2 and P3 connectors are listed in Table 2-1 on page 36. Jumper configurations for the  $\pm 15$  VDC power and reference connection are shown in Table 2-2 on page 37. Factory configuration is shown in Table 2-3 on page 38, jumper locations are shown in Figure 2-1 on page 39.

**NOTE:** All other jumpers are option specific and should not be changed by user.

The jumper and resistor installations for the reference input voltage specified upon the customer's request (placement of order) are listed in Table 5.3-4.

Table 2-1 P2, P3 Pinout

| SIGNAL   | P2 CONNECTOR      | P3 CONNECTOR |

|----------|-------------------|--------------|

| DIG. GND | B12, B22, B31, C1 |              |

| AND. GND | A3, A4,           | 2, 24, 25    |

| +15VDC   | C5, C6            | 13           |

| -15VDC   | C7, C8            | 11           |

| RH       | C29               | 14           |

| RL       | C27               | 16           |

| 0S1      |                   | 1            |

| 0S2      |                   | 3            |

| 0\$3     |                   | 5            |

| 0S4      |                   | 7            |

| 1S1      |                   | 18           |

| 1S2      |                   | 20           |

| 1S3      |                   | 22           |

| 1S4      |                   | 9            |

| S1*      |                   |              |

| S2*      | C18               |              |

| S3*      | C20<br>C22        |              |

| S4*      | C24               |              |

|          |                   |              |

<sup>\*</sup>Relay selects channel 0 (0S1, 0S2, 0S3, 0S4) or channel 1 (1S1, 1S2, 1S3,1S4).

Table 2-2 Jumper Factory Configuration

| JUMPER     | HIGH DRIVE<br>CAPABILITY<br>(POWER) OPTION | HIGH DRIVE CAPABILITY<br>(POWER) OPTION WITH<br>TRANSFORMER OPTION | LOW DRIVE<br>CAPABILITY<br>(POWER) OPTION |  |  |  |

|------------|--------------------------------------------|--------------------------------------------------------------------|-------------------------------------------|--|--|--|

|            | (4905-XXXX-5)                              | (4905-XXXST-2)                                                     | (4905-XXXX-02)                            |  |  |  |

| H1         | B → C                                      | B → C                                                              | B → C                                     |  |  |  |

| H2         | B <b>→</b> C                               | В → С                                                              | в → С                                     |  |  |  |

| H3         | NOT INSTALLED                              | NOT INSTALLED                                                      | INSTALLED                                 |  |  |  |

| ▼          |                                            |                                                                    |                                           |  |  |  |

| H5         | NOT INSTALLED                              | NOT INSTALLED                                                      | INSTALLED                                 |  |  |  |

| H6         | INSTALLED                                  | NOT INSTALLED                                                      | INSTALLED                                 |  |  |  |

| ♦          |                                            |                                                                    |                                           |  |  |  |

| H8         | INSTALLED                                  | NOT INSTALLED                                                      | INSTALLED                                 |  |  |  |

| H9         | NOT INSTALLED                              | NOT INSTALLED                                                      | INSTALLED                                 |  |  |  |

| ♦          |                                            |                                                                    |                                           |  |  |  |

| H11        | NOT INSTALLED                              | NOT INSTALLED                                                      | INSTALLED                                 |  |  |  |

| H12        | INSTALLED                                  | NOT INSTALLED                                                      | INSTALLED                                 |  |  |  |

| ♦          |                                            |                                                                    |                                           |  |  |  |

| H14        | INSTALLED                                  | NOT INSTALLED                                                      | INSTALLED                                 |  |  |  |

| H15        | A <b>→</b> B                               | A <b>→</b> B                                                       | A <b>→</b> B                              |  |  |  |

| H16        | B <b>→</b> C                               | B <b>→</b> C                                                       | B <b>→</b> C                              |  |  |  |

| H17        | B <b>→</b> C                               | В — С                                                              | B <b>→</b> C                              |  |  |  |

| H18        | B → C                                      | B — C                                                              | B — C                                     |  |  |  |

| H19<br>H20 | B → C                                      | B → C<br>B → C                                                     | B → C                                     |  |  |  |

|            |                                            |                                                                    |                                           |  |  |  |

| SYN        | FACTORY CONFIGURE                          |                                                                    |                                           |  |  |  |

| LES        | RES FACTORY CONFIGURED TO BOARD OPTION     |                                                                    |                                           |  |  |  |

Table 2-3 Jumper Configuration

| JUMPER           | CONFIGURATION                            | FUNCTION                                                                                              |

|------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------|

| H1               | A → B<br>C → B                           | CONNECTS CH1 RH TO P3 1RH CONNECTS CH1 RH TO CH0 RH                                                   |

| H2               | A → B<br>C → B                           | CONNECTS CH1 RL TO P3 1RL CONNECTS CH1 RL TO CH0 RL                                                   |

| H3<br>H4<br>H5   | FACTORY<br>CONFIGURED<br>TO BOARD OPTION | SEE SCHEMATIC SHEET 8<br>(USED TO BYPASS OP AMP<br>CIRCUITRY)                                         |

| H6               | INSTALLED                                | CONNECTS CH0 S3 TO OUTPUT RELAYS                                                                      |

| H7               | INSTALLED                                | CONNECTS CH0 S2 TO OUTPUT RELAYS                                                                      |

| H8               | INSTALLED                                | CONNECTS CH0 S1 TO OUTPUT RELAYS                                                                      |

| H9<br>H10<br>H11 | FACTORY<br>CONFIGURED<br>TO BOARD OPTION | SEE SCHEMATIC SHEET 8<br>(USED TO BYPASS OP AMP CIRCUITRY)                                            |

| H12              | INSTALLED                                | CONNECTS CH1 S3 TO OUTPUT RELAYS                                                                      |

| H13              | INSTALLED                                | CONNECTS CH1 S2 TO OUTPUT RELAYS                                                                      |

| H14              | INSTALLED                                | CONNECTS CH1 S1 TO OUTPUT RELAYS                                                                      |

| H15              | A → B<br>C → B                           | CONNECTS RL TO CH0 RL OF CONVERTER MODULE CONNECTS RH TO CH0 RL OF CONVERTER MODULE (RH, RL REVERSAL) |

| H16              | C → B<br>A → B                           | CONNECTS RH TO CH0 RH OF CONVERTER MODULE CONNECTS RL TO CH0 RH OF CONVERTER MODULE (RH, RL REVERSAL) |

| H17              | A → B<br>C → B                           | CONNECTS P3 RL TO BOARD CONNECTS P2 RL TO BOARD                                                       |

| H18              | A → B<br>C → B                           | CONNECTS P3 RH TO BOARD CONNECTS P2 RH TO BOARD                                                       |

| H19              | A → B<br>C → B                           | CONNECTS P3 -15 V TO BOARD<br>CONNECTS P2 -15 V TO BOARD                                              |

| H20              | A → B<br>C → B                           | CONNECTS P3 +15 V TO BOARD<br>CONNECTS P2 +15 V TO BOARD                                              |

| SYN              | FACTORY CONFIGURED<br>TO BOARD OPTION    | CONFIGURES CONVERTER MODULES FOR SYNCHRO OPERATION                                                    |

| RES              | FACTORY CONFIGURED<br>TO BOARD OPTION    | CONFIGURES CONVERTER MODULES FOR RESOLVER OPERATION                                                   |

| LOV              | FACTORY CONFIGURED<br>TO BOARD OPTION    | CONFIGURES CONVERTER MODULES FOR LOW VOLTAGE OPERATION                                                |

| HIV              | FACTORY CONFIGURED<br>TO BOARD OPTION    | CONFIGURES CONVERTER MODULES FOR HIGH VOLTAGE OPERATION                                               |

Table 2-4

Installation Table of Reference Voltage

| JUMPER/  | 1.3 Vrms | 26 Vrms  | 115 Vrms | 2-25 Vrms | 27-114 Vrms | 116-200 Vrms |

|----------|----------|----------|----------|-----------|-------------|--------------|

| RESISTOR | (NOTE 3) | (NOTE 2) | (NOTE 3) | (NOTE 1)  | (NOTE 1)    | (NOTE 1)     |

|          |          |          |          |           |             |              |

NOTES 1. For non-standard reference input voltages contact factory for installation of R1 to R8 (requires new option number when ordering).

- 2. Factory configuration.

- 3. Factory configured upon request (new option number required when ordering).

# **Built-in-Test Output Configuration**

Relays are provided on the VMIVME-4905 to support off-line and real-time fault detection and isolation. The four relay functions are shown in Table 2-5 below.

Table 2-5 Relay Functions\*\*

| CSR BIT | MNEMONIC RELAY CONTROL BIT | FUNCTION PERFORMED                                        |

|---------|----------------------------|-----------------------------------------------------------|

| 14      | OUT CH0                    | CONNECTS D/S OR D/R CHAN 0 TO P3 FRONT PANEL CONNECTOR    |

| 13      | TEST CH0                   | CONNECTS D/S OR D/R CHAN 0 TO P2 CONNECTOR/SRTbus™*       |

| 12      | OUT CH1                    | CONNECTS D/S OR D/R CHAN 1 TO<br>P3 FRONT PANEL CONNECTOR |

| 11      | TEST CH1                   | CONNECTS D/S OR D/R CHAN 1 TO P2 CONNECTOR/SRTbus™*       |

On power-up or on system reset, all relays are inactive.

<sup>\*</sup>SRTbus™ is a synchro/resolver test bus, VMIVME-SRXX.

<sup>\*\*</sup>Control hardware prevents test relays from being asserted at the same time. The asserted relay must be de-energized prior to asserting the other relay. The first one set has priority.

# **Hardware Connection to Synchro or Resolver**

Depending on whether the board has Digital-to-Resolver Converter (DRC) or Digital-to-Synchro Converter (DSC) on-board, the pinouts in *Connector and Jumper/Configuration* on page 35. Table 2-1 on page 36, are directly applicable to the terminals labeled on the synchro or resolver load.

When driving a synchro load with the board, the S4 pins for channel No. 0 and channel No. 1 are not connected.

The RH and RL signed pinouts connect directly to the rotor terminals labeled R1 and R2, respectively. RH and RL are common to both DRC and DSC channels.

### **Built-in-Test Configuration with Synchro/Resolver Test Bus**

VMIC's VMIVME-4911 Quad SDC/RDC Board interface is utilized for fault detection and isolation of DSC/DRC boards and is based on an industry standard quad-multiplexing SDC/RDC module. This high performance, fast settling, 14-bit SDC/RDC is required to support the real-time fault detection and isolation capabilities of the IIOC and the real-time synchro/resolver input data processing required in the simulation and training industry.

VMIC also produces a model VMIVME-4910 tracking SDC/RDC Board that supports fault detection and isolation. The VMIVME-4910 is a single-channel synchro/resolver input board that is designed with input data switching relays to support either inputs from field sources via the front panel connector or the P2 VMEbus connector. It is also designed to support loopback testing of VMIC's 49XX series DSC/DRC products. The worst-case settling time of the VMIVME-4910 may exceed 250 ms; therefore, it is not recommended for real-time data processing where update rates are in excess of the worst-case settling time. VMIC recommends the VMIVME-4911 Quad SDC/RDC Board for real-time simulation and training applications. This high-speed converter features simultaneous sampling and random access with a resolution of 14 bits and a 150  $\mu s$  conversion time per channel.

The relay operation described in *Built-in-Test Output Configuration* on page 41 provides the user with the information necessary to implement built-in-test functions.

**WARNING:** This product must be used in a card cage with cooling fans in operation.

**CAUTION:** When using multiple VMIVME-4905 Boards in conjunction with the SRTbus  $^{\text{TM}}$ , the programmer must not switch more than one Synchro/Resolver output onto the SRTbus  $^{\text{TM}}$  at any one time. Doing so may result in damage to the DSC/DRC boards, or the SRTbus  $^{\text{TM}}$  backplane or to both. A one millisecond minimum delay must be provided to allow a relay to become de-energized.

### **Address Modifiers**

The VMIVME-4905 is configured at the factory to respond to short supervisory I/O access. The user may select the short non-privileged I/O access mode by changing the address modifier switch, as shown in Figure 2-2 on page 45. The location of switch S1 is shown in Figure 2-1 on page 39.

### **Address Selection Switches**

The VMIVME-4905 occupies 8 bytes of the VMEbus short I/O address space. The upper 13 address bits are switch selectable, as shown in Figure 2-2 below. The location of these switches are shown in Figure 2-1 on page 39.

SHORT SUPERVISORY ADDRESS MODIFIER SELECTED WHEN SW1 POSITION EIGHT IS IN THE OFF POSITION. SHORT NON-PRIVILEGED ADDRESS MODIFIER IS SELECTED WHEN SW1 POSITION EIGHT IS IN THE ON POSITION.

Figure 2-2 Base Address Switches

### **Calibration of High Drive Capability Boards**

All boards with the high drive capability option are calibrated at the factory to perform at the highest possible optimum level. It is not recommended that the user alter the set position of the calibration trim pots, doing so might cause out-of-calibration readings. If calibration becomes necessary to the user, then the following procedure may be followed:

**NOTE:** The calibration trim pots (R17, R22, R31, R36) and the associated operational amplifiers (OP AMPs) (U2, U3, U4, U5, U6, U7) may be viewed in their existing locations on sheet 2 of 9 from the assembly drawing, Number 132-004905-000, available from VMIC..

**NOTE:** The following procedure should be followed only after the board has been configured (±15 V, RH, RL, etc.,) for normal operation.

### **Channel Zero**

**Step 1:** Locate the OP AMP U2 and place a precision DC voltage meter on the output (case) of U2, thus providing a precision DC voltage reading between the output and ground. This will be referred to as the DC offset.

**Step 2:**With the DC offset from U2 recorded, locate the OP AMP U3 and place a precision DC voltage meter between the output (case) of U3 and ground.

**Step 3:**Locate the calibration trim pot R17 and alter the resistance value by trimming the pot to provide U3 with the same exact DC offset as was recorded for U2.

**Step 4**:Locate the OP AMP U4 and place a precision DC voltage meter between the output (case) of U4 and ground.

**Step 5:**Locate the calibration trim pot R22 and alter the resistance value by trimming the pot to provide U4 with the same exact DC offset as was recorded for U2.

#### **Channel One**

**Step 6:** Locate the OP AMP U5 and place a precision DC voltage meter on the output (case) of U5, thus providing a precision DC voltage reading between the output and ground. This will be referred to as the DC offset.

**Step 7:** With the DC offset from U5 recorded, locate the OP AMP U6 and place a precision DC voltage meter between the output (case) of U6 and ground.

**Step 8:** Locate the calibration trim pot R31 and alter the resistance value by trimming the pot to provide U6 with the same exact DC offset as was recorded for U5.

**Step 9:** Locate the OP AMP U7 and place a precision DC voltage meter between the output (case) of U7 and ground.

**Step 10:** Locate the calibration trim pot R36 and alter the resistance value by trimming the pot to provide U7 with the same exact DC offset as was recorded for U5.

# **Programming**

### **Contents**

Built-in-Test Configuration with Synchro/Resolver Test Bus...... 52

### Introduction

An output operation is initiated by executing an output transfer instruction that loads one of two output registers. The execution of this instruction sends the VMEbus an address that causes selection of the Digital-to-Synchro/Resolver Converter (DSC/DRC) Board if the board address switches match the address transmitted. The bit pattern of the data output word determines the position of the user's torque receiver(s). The bit-to-angle conversion (position) information is shown in Table 3-1 on page 50.

The Central Processor Unit (CPU) should not initiate large shaft position changes that may result in overdriving the torque receiver(s). High current electrical transients and mechanical transients may damage the torque receiver and or the DSC/DRC Board. VMIC suggests that the user design synchro smoothing into a software driver. Smoothing is accomplished by incrementing to the desired angle.

The DSC/DRC Board is initialized at power-up with the field (user torque receivers) disconnected and the front panel Fail LED illuminated. The format and register addresses to control the relays, front panel Fail LED, and output torque receivers are shown in Table 3-2 on page 51. All VMIVME-4905 data output registers are *write only* and can be written as bytes or words.

THE Control and Status Register (CSR) Bits 11 and 13 Control the connection of the synchro outputs VIA RELAYS K2 AND K3 to the synchro backplane (see Figure 1-10 on page 28); therefore, only one of these relays can be energized at one time. The programmer must provide a one millisecond (minimum) delay for relays to drop out before another relay can be energized. Relays on other boards must also be de-energized before they are tested. Simultaneous connection of more than one synchro signal to the test backplane can result in stuck relays and/or blown fuses.

Table 3-1 Data Input Word: Bit Weights

| BIT<br>NO. | (14-N)  | LSB AS % OF<br>FULL SCALE | RADIANS<br>BIT | DEGREES<br>BIT | MINUTES<br>BIT | SECONDS<br>BIT | MILS<br>BIT |

|------------|---------|---------------------------|----------------|----------------|----------------|----------------|-------------|

|            | 10.001  | 00040050                  | 00000050       | 0040707        | 4.04.000       | 70.4040        | 0.000005    |

| 0          | 16,384. | .00610352                 | .00038350      | .0219727       | 1.31836        | 79.1016        | 0.390625    |

| 1          | 8,192.  | .01220703                 | .00076699      | .0439453       | 2.63672        | 158.2031       | 0.78125     |

| 2          | 4,096.  | .02441406                 | .00153398      | .0878906       | 5.27344        | 316.4063       | 1.5625      |

| 3          | 2,048.  | .04882813                 | .00306796      | .1757813       | 10.54688       | 632.8125       | 3.125       |

| 4          | 1,024.  | .09765625                 | .00613592      | .3515625       | 21.09375       | 1,265.6250     | 6.25        |

| 5          | 512.    | .1953125                  | .01227185      | .703125        | 42.1875        | 2,531.25       | 12.5        |

| 6          | 256.    | .390625                   | .02454369      | 1.40625        | 84.375         | 5,062.5        | 25.         |

| 7          | 128.    | .78125                    | .04908739      | 2.8125         | 168.75         | 10,125.        | 50.         |

| 8          | 64.     | 1.5625                    | .09817477      | 5.625          | 337.5          | 20,250.        | 100.        |

| 9          | 32.     | 3.125                     | .19634954      | 11.25          | 675.           | 40,500.        | 200.        |

| 10         | 16.     | 6.25                      | .39269908      | 22.5           | 1,350.         | 81,000.        | 400.        |

| 11         | 8.      | 12.5                      | .78539816      | 45.            | 2,700.         | 162,000.       | 800.        |

| 12         | 4.      | 25.                       | 1.57079633     | 90.            | 5,400.         | 324,000.       | 1,600.      |

| 13         | 2.      | 50.                       | 3.14159265     | 180.           | 10,800.        | 648,000.       | 3,200.      |

Table 3-2 Address Map and Register Bit Formats

| HEX<br>ADDRESS | ļ  | BINA<br>ADDRE |    |             |               |                     |                      |                     |                      |            |                        |       |

|----------------|----|---------------|----|-------------|---------------|---------------------|----------------------|---------------------|----------------------|------------|------------------------|-------|

| A15 - A4       | А3 | A2            | A1 | A0          |               |                     |                      |                     |                      |            |                        |       |

|                |    |               |    |             |               | D/S OR D/R          | NO. 0 OUTP           | UT REGIST           | ER UPPER E           | BYTE (WRIT | E ONLY)                |       |

| ххх            | Х  | 0             | 0  | 0           | BIT 15        | BIT 14              | BIT 13               | BIT 12              | BIT 11               | BIT 10     | BIT 9                  | BIT 8 |

|                |    |               |    |             | NOT<br>USED   | NOT<br>USED         | 0DB13                | 0DB12               | 0DB11                | 0DB10      | 0DB9                   | 0DB8  |

|                |    |               |    |             | I             | D/S OR D/R I        | NO. 0 OUTP           | UT REGISTE          | ER LOWER I           | BYTE (WRIT | E ONLY)                |       |

| x x x          | Х  | 0             | 0  | 1           | BIT 7         | BIT 6               | BIT 5                | BIT 4               | BIT 3                | BIT 2      | BIT 1                  | BIT 0 |

|                |    |               |    |             | 0DB7          | 0DB6                | 0DB5                 | 0DB4                | 0DB3                 | 0DB2       | 0DB1                   | 0DB0  |

|                |    |               |    |             |               | D/S OR D/R          | NO. 1 OUTF           | ·<br>PUT REGIST     | ER UPPER I           | BYTE (WRIT | E ONLY)                | •     |

| x x x          | Х  | 0             | 1  | 0           | BIT 15        | BIT 14              | BIT 13               | BIT 12              | BIT 11               | BIT 10     | BIT 9                  | BIT 8 |

|                |    |               |    | NOT<br>USED | NOT<br>USED   | 1DB13               | 1DB12                | 1DB11               | 1DB10                | 1DB9       | 1DB8                   |       |

|                |    |               |    |             |               | D/S OR D/R          | NO. 1 OUTP           | UT REGIST           | ER LOWER             | BYTE (WRIT | E ONLY)                | •     |

| x x x          | Х  | 0             | 1  | 1           | BIT 7         | BIT 6               | BIT 5                | BIT 4               | BIT 3                | BIT 2      | BIT 1                  | BIT 0 |

|                |    |               |    |             | 1DB7          | 1DB6                | 1DB5                 | 1DB4                | 1DB3                 | 1DB2       | 1DB1                   | 1DB0  |

|                |    |               |    |             |               | С                   | ONTROL ST            | ATUS REGI           | STER UPPE            | R BYTE     | •                      |       |

| x x x          | Х  | 1             | 0  | 0           | BIT 15        | BIT 14              | BIT 13               | BIT 12              | BIT 11               | BIT 10     | BIT 9                  | BIT 8 |

|                |    |               |    |             | FL=1<br>(R/W) | OUT<br>CH0<br>(R/W) | TEST<br>CH0<br>(R/W) | OUT<br>CH1<br>(R/W) | TEST<br>CH1<br>(R/W) |            | NOT USED<br>(FLOATING) |       |

|                |    |               |    |             |               |                     | CONTROL S            | STATUS REG          | GISTER LOV           | VER BYTE   |                        |       |

| x x x          | Х  | 1             | 0  | 1           | BIT 7         | BIT 6               | BIT 5                | BIT 4               | BIT 3                | BIT 2      | BIT 1                  | BIT 0 |

|                |    |               |    |             |               |                     |                      | - NOT USE           |                      |            |                        |       |

A15 A3

Base address switch selectable

FL=Front panel Fail LED

0=On

1=Off

Fail LED is turned ON at power-up or system reset.

All register bits are cleared at power-up or system reset, which also de-energizes the relays.

# **Built-in-Test Configuration with Synchro/Resolver Test Bus**

VMIC's VMIVME-4911 Quad SDC/RDC interface is utilized for fault detection and isolation of DSC/DRC Boards and is based on an industry standard quad-multiplexing SDC/RDC module. This high performance, fast settling, 14-bit SDC/RDC Board is required to support the real-time fault detection and isolation capabilities of the IIOC and the real-time synchro/resolver input data processing required in the simulation and training industry.

The relay operation described in the following section provides the user with the information necessary to implement built-in-test functions.

### **Built-in-Test Output Configuration**

Relays are provided on the VMIVME-4905 to support off-line and real-time fault detection and isolation. The four relay functions are shown in Table 3-3 below.

| Table | 3-3 | Relay | Function | ons |

|-------|-----|-------|----------|-----|

|-------|-----|-------|----------|-----|

|         |                            | •                                                         |

|---------|----------------------------|-----------------------------------------------------------|

| CSR BIT | MNEMONIC RELAY CONTROL BIT | FUNCTION PERFORMED                                        |

| 14      | OUT CH0                    | CONNECTS D/S OR D/R CHAN 0 TO<br>P3 FRONT PANEL CONNECTOR |

| 13      | TEST CH0                   | CONNECTS D/S OR D/R CHAN 0 TO P2 CONNECTOR/SRTbus*        |

| 12      | OUT CH1                    | CONNECTS D/S OR D/R CHAN 1 TO<br>P3 FRONT PANEL CONNECTOR |

| 11      | TEST CH1                   | CONNECTS D/S OR D/R CHAN 1 TO P2 CONNECTOR/SRTbus™        |

On power-up or on system reset, all relays are inactive.

<sup>\*</sup>SRTbus<sup>TM</sup> is a synchro/resolver test bus, VMIVME-SRXX.

# Maintenance

### **Maintenance**

This section provides information relative to the care and maintenance of VMIC's products. If the product malfunctions, verify the following:

- System power

- Software

- System configuration

- Electrical connections

- Jumper or configuration options

- Boards are fully inserted into their proper connector location

- Connector pins are clean and free from contamination

- No components of adjacent boards are disturbed when inserting or removing the board from the chassis

- Quality of cables and I/O connections

If products must be returned, contact VMIC for a Return Material Authorization (RMA) Number. This RMA Number must be obtained prior to any return.

Contact VMIC Customer Service at 1-800-240-7782, or E-mail: customer.service@vmic.com

# **Maintenance Prints**