# VMIVME-6000

# 1553 COMMUNICATIONS INTERFACE BOARD

**PRODUCT MANUAL**

DOCUMENT NO. 500-006000-000 E

Revised September 30, 1999

VMIC 12090 SOUTH MEMORIAL PARKWAY HUNTSVILLE, ALABAMA 35803-3308 (256) 880-0444 Fax: (256) 882-0859 1-800-322-3616

# **COPYRIGHT AND TRADEMARKS**

© Copyright September 1993. The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

AMXbus, BITMODULE, COSMODULE, DMAbus, Instant OPC wizard logo, IOMax, IOWorks Access, IOWorks Foundation, IOWorks man figure, IOWorks Manager, IOWorks Server, MAGICWARE, MEGAMODULE, PLC ACCELERATOR (ACCELERATION), Quick Link, RTnet, Soft Logic Link, SRTbus, TESTCAL, "The Next Generation PLC", The PLC Connection, TURBOMODULE, UCLIO, UIOD, UPLC, Visual Soft Logic Control(Ier), *VMEaccess, VMEmanager, VMEmonitor*, VMEnet, VMEnet II, and *VMEprobe* are trademarks and The I/O Experts, The I/O Systems Experts, The Soft Logic Experts, and The Total Solutions Provider are service marks of VMIC.

(I/O man figure)

TV.

(IOWorks man figure)

The I/O man figure, IOWorks, UIOC, Visual IOWorks, the VMIC logo, and *WinUIOC* are registered trademarks of VMIC.

ActiveX, Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, Windows NT, and XENIX are registered trademarks of Microsoft Corporation.

Celeron and MMX are trademarks and Intel and Pentium are registered trademarks of Intel Corporation.

PICMG and CompactPCI are registered trademarks of PCI Industrial Computer Manufacturers' Group.

Other registered trademarks are the property of their respective owners.

VMIC All Rights Reserved This document shall not be duplicated, nor its contents used for any purpose, unless granted express written permission from VMIC.

| RECORD OF REVISIONS                            |                                   |                                              |                                                                  |              |                |

|------------------------------------------------|-----------------------------------|----------------------------------------------|------------------------------------------------------------------|--------------|----------------|

| REVISION<br>LETTER                             | DATE                              | P                                            | AGES INVOLVED                                                    | CHANGE       | NUMBER         |

| A                                              | 09/09/93                          | Release                                      |                                                                  | 93-071       | 2              |

| В                                              | 10/26/93                          | Changed pag                                  | es ii, and 3-2 per ECO                                           | 94-007       | 0              |

| С                                              | 11/20/97                          | Changed pag<br>pages 4-124,<br>4-166, and 4- | es ii, viii, and Section 4<br>4-137, 4-153, 4-160, 4-161,<br>173 | 97-077       | 8              |

| D                                              | 02/05/99                          | Change page                                  | s ii and 4-165                                                   | 99-011       | 6              |

| Е                                              | 09/30/99                          | Cover, pages                                 | ii and 4-186                                                     | 99-078       | 6              |

|                                                |                                   |                                              |                                                                  |              |                |

| VMIC<br>12090 South Memo<br>Huntsville, AL 358 | orial Parkway<br>803-3308 • (256) | 880-0444                                     | DOC. NO. 500-006000-000                                          | REV LTR<br>E | PAGE NO.<br>ii |

# VMIC SAFETY SUMMARY

THE FOLLOWING GENERAL SAFETY PRECAUTIONS MUST BE OBSERVED DURING ALL PHASES OF THE OPERATION, SERVICE, AND REPAIR OF THIS PRODUCT. FAILURE TO COMPLY WITH THESE PRECAUTIONS OR WITH SPECIFIC WARNINGS ELSEWHERE IN THIS MANUAL VIOLATES SAFETY STANDARDS OF DESIGN, MANUFACTURE, AND INTENDED USE OF THIS PRODUCT. VMIC ASSUMES NO LIABILITY FOR THE CUSTOMER'S FAILURE TO COMPLY WITH THESE REQUIREMENTS.

### GROUND THE SYSTEM

To minimize shock hazard, the chassis and system cabinet must be connected to an electrical ground. A three-conductor AC power cable should be used. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet.

### DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE

Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.

### KEEP AWAY FROM LIVE CIRCUITS

Operating personnel must not remove product covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

### DO NOT SERVICE OR ADJUST ALONE

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

### DO NOT SUBSTITUTE PARTS OR MODIFY SYSTEM

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to VMIC for service and repair to ensure that safety features are maintained.

### DANGEROUS PROCEDURE WARNINGS

Warnings, such as the example below, precede only potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

WARNING

DANGEROUS VOLTAGES, CAPABLE OF CAUSING DEATH, ARE PRESENT IN THIS SYSTEM. USE EXTREME CAUTION WHEN HANDLING, TESTING, AND ADJUSTING.

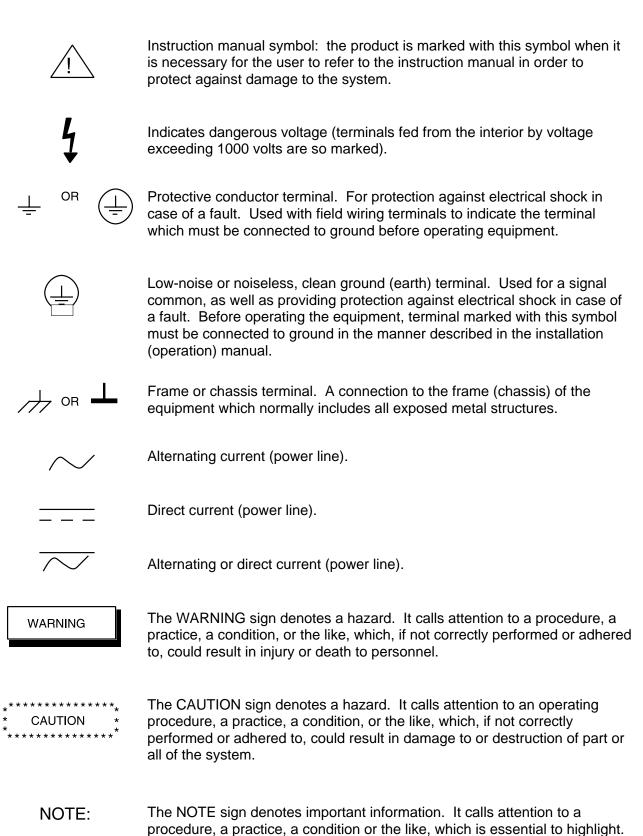

# SAFETY SYMBOLS

# GENERAL DEFINITIONS OF SAFETY SYMBOLS USED IN THIS MANUAL

# VMIVME-6000 1553 COMMUNICATIONS INTERFACE BOARD

# TABLE OF CONTENTS

### SECTION 1 INTRODUCTION

1.1GENERAL DESCRIPTION1-11.2FUNCTIONAL DESCRIPTION1-11.3REFERENCE MATERIAL LIST1-3

# SECTION 2 PHYSICAL DESCRIPTION AND SPECIFICATIONS

# SECTION 3 THEORY OF OPERATION

| 3.1 | INTRODUCTION         | 3-1 |

|-----|----------------------|-----|

| 3.2 | VMEbus INTERFACE     |     |

| 3.3 | REGISTERS AND MEMORY |     |

| 3.4 | 1553 CONTROL         | 3-2 |

### SECTION 4 PROGRAMMING

| PROGRAMMING THE VMIVME-6000                 | 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REGISTERS                                   | 4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Configuration Registers                     | 4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XIO Registers                               | 4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Hardware Registers                          | 4-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Special Function Registers                  | 4-32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Internal ALU Registers                      | 4-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Active XIO                                  | 4-96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| OPERATIONAL MODES                           | 4-96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Self-Test                                   | 4-97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Power-Up Self-Test                          | 4-97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Diagmode Control block                      | 4-97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Multiple Remote Terminal (MRT)/Monitor Mode | 4-131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Multiple Remote Terminal (MRT)              | 4-131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Monitor (MON)                               | 4-131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MRT/Monitor Setup                           | 4-132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Initialization                              | 4-132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MRT/MON Header                              | 4-134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                             | PROGRAMMING THE VMIVME-6000<br>REGISTERS.<br>Configuration Registers.<br>XIO Registers.<br>Hardware Registers.<br>Special Function Registers.<br>Internal ALU Registers.<br>Active XIO.<br>OPERATIONAL MODES.<br>Self-Test<br>Power-Up Self-Test.<br>Diagmode.<br>Diagmode.<br>Diagmode Control block.<br>Bus Controller/Simulator Mode.<br>Multiple Remote Terminal (MRT)/Monitor Mode<br>Multiple Remote Terminal (MRT).<br>Monitor (MON).<br>MRT/Monitor Setup.<br>Initialization.<br>Quick Start MRT/MON.<br>MRT/MON Control Blocks.<br>MRT/MON Header |

# VMIVME-6000 1553 COMMUNICATIONS INTERFACE BOARD

# TABLE OF CONTENTS (CONTINUED)

|           |                                       | <u>Page</u> |

|-----------|---------------------------------------|-------------|

| 4.3.3.6.2 | RT Control Blocks                     | 4-149       |

| 4.3.3.6.3 | Subaddress Control Blocks             | 4-162       |

| 4.3.3.6.4 | Data Buffer Format                    |             |

| 4.3.3.7   | MRT/MON Broadcast Operation           | 4-167       |

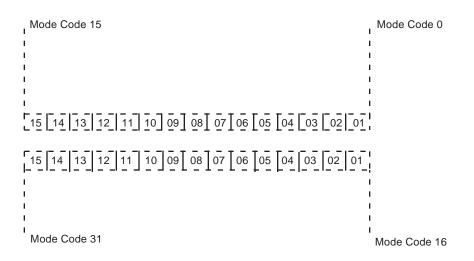

| 4.3.3.8   | NRT Mode Code Operation               | 4-167       |

| 4.3.3.8.1 | Enabling Mode Codes                   | 4-167       |

| 4.3.3.8.2 | Mode Code Interrupts                  | 4-167       |

|           | Mode Codes                            | 4-168       |

| 4.4       | EXTERNAL MRT/MON RAM                  |             |

| 4.5       | INTERRUPTS                            |             |

| 4.5.1     | Interrupt Enable/Disable              | 4-184       |

| 4.5.2     | Interrupt Status Register/Masks (ISR) | 4-185       |

| 4.5.2.1   | Transmission Error                    |             |

| 4.5.2.2   | DMA Error                             |             |

| 4.5.2.3   | B Interrupt Not Serviced              |             |

| 4.5.2.4   | End of Message Interrupt              |             |

| 4.5.2.5   | Programming Error                     |             |

| 4.5.2.6   | Status Word Mask Compare              |             |

| 4.5.2.7   | Ring Buffer Page Full                 |             |

| 4.5.2.8   | Ring Buffer Full                      |             |

| 4.5.2.9   | "STOP" Detected                       |             |

| 4.5.2.10  | Context Lock Lost                     |             |

| 4.5.2.11  | Illegal Command Word Received         |             |

| 4.5.2.12  | Command Word Trigger                  |             |

| 4.5.2.13  | Mode Code Received                    |             |

| 4.5.2.14  | Auto Retry Successful                 |             |

| 4.5.2.15  | Auto Retry Failed                     |             |

| 4.5.2.16  | Bus Switchover Performed              |             |

| 4.5.2.17  | Bit Failed                            |             |

| 4.5.2.18  | Bit Data Compare (Loop Fail)          |             |

| 4.5.2.19  | Message on B (Secondary) Bus          |             |

| 4.5.3     | Interrupt Vectors                     |             |

| 4.6       |                                       |             |

| 4.6.1     | Error Generation Selects              |             |

| 4.6.1.1   | Manchester Error                      |             |

| 4.6.1.2   | Parity Error                          |             |

| 4.6.1.3   | SYNC Error                            |             |

| 4.6.1.4   | Bit Count Error                       |             |

| 4.6.1.5   | Word Count Error                      | 4-194       |

# VMIVME-6000 1553 COMMUNICATIONS INTERFACE BOARD

# TABLE OF CONTENTS (CONTINUED)

|         |                                       | <u>Page</u> |

|---------|---------------------------------------|-------------|

| 4.6.1.6 | Wrong Bus Response Error              | 4-194       |

| 4.6.1.7 | Data Word Gap Error                   | 4-194       |

| 4.6.1.8 | Error in Status Word and Command Word | 4-194       |

| 4.6.2   | Error Generation Words                | 4-195       |

# SECTION 5 CONFIGURATION AND INSTALLATION

| 5.1<br>5.2 | UNPACKING PROCEDURES<br>PHYSICAL INSTALLATION |     |

|------------|-----------------------------------------------|-----|

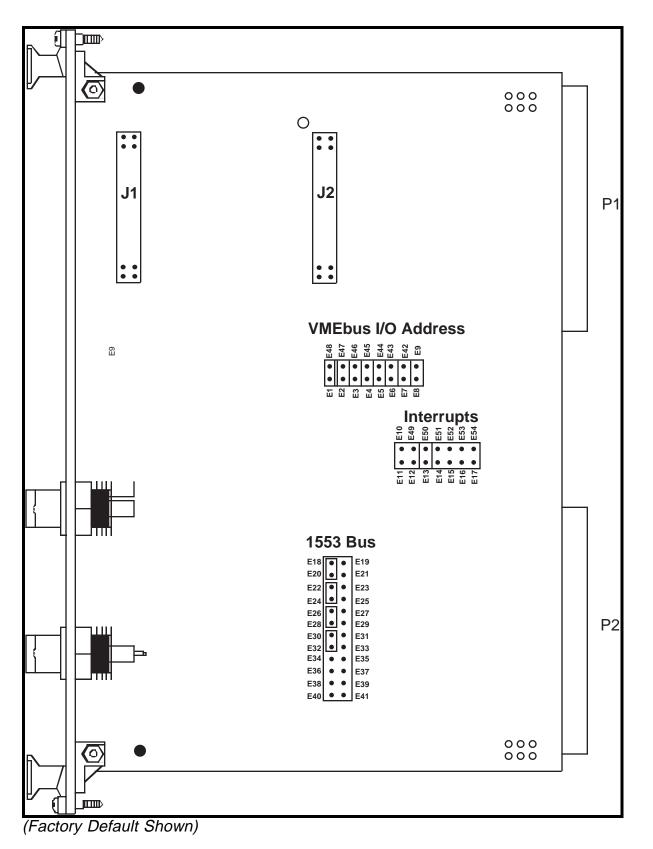

| 5.3        | JUMPER INSTALLATIONS                          |     |

| 5.3.1      | VMIVME-6000 Short I/O Base Address Header     | 5-3 |

| 5.3.2      | Interrupt Request Header                      | 5-3 |

| 5.3.3      | 1553 Bus Header                               | 5-4 |

| 5.3.4      | Transformer Center Tap Jumpers                | 5-6 |

| 5.4        | MIL-STD-1553 CABLES                           |     |

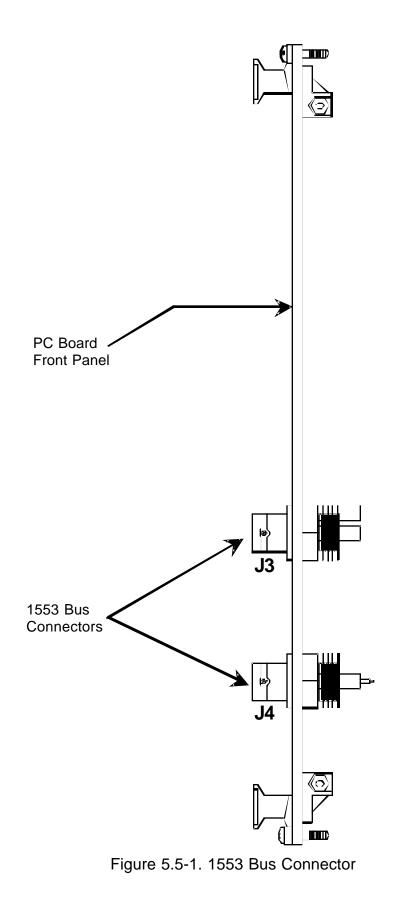

| 5.5        | CABLE CONNECTOR                               | 5-6 |

# SECTION 6 MAINTENANCE

| 6.1 | MAINTENANCE           |

|-----|-----------------------|

| 6.2 | MAINTENANCE PRINTS6-1 |

# LIST OF FIGURES

| <u>Figure</u> |                                         | <u>Page</u> |

|---------------|-----------------------------------------|-------------|

| 1.2.1         | VMIVME-6000 Block Diagram               | 1-2         |

| 4.1-1         | VMIVME-6000 Programming Block Diagram   | 4-2         |

| 4.2-1         | VMIVME-6000 Configuration Registers     | 4-4         |

| 4.3.3.8.1-1   | Mode Code Enables                       | 4-168       |

| 4.6.2-1       | Error Generation Words                  | 4-195       |

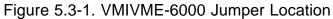

| 5.3-1         | VMIVME-6000 Jumper Location             | 5-2         |

| 5.3.1-1       | VMIVME-6000 Address Header              | 5-3         |

| 5.3.2-1       | Interrupt Request Header                | 5-3         |

| 5.3.3-1       | VMIVME-6000 1553 Bus Header             |             |

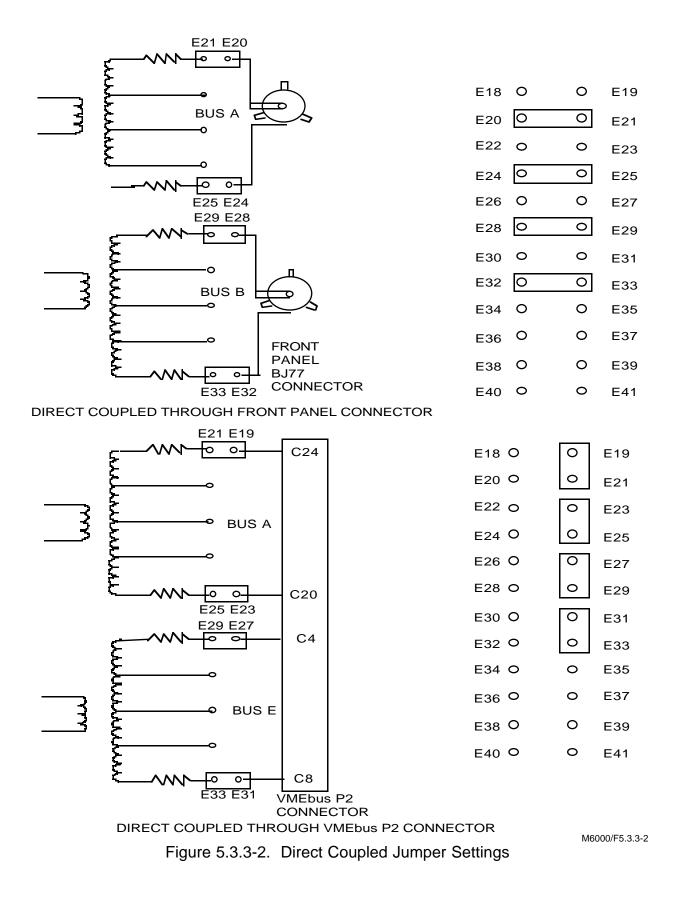

| 5.3.3-2       | Direct Coupled Jumper Settings          | 5-5         |

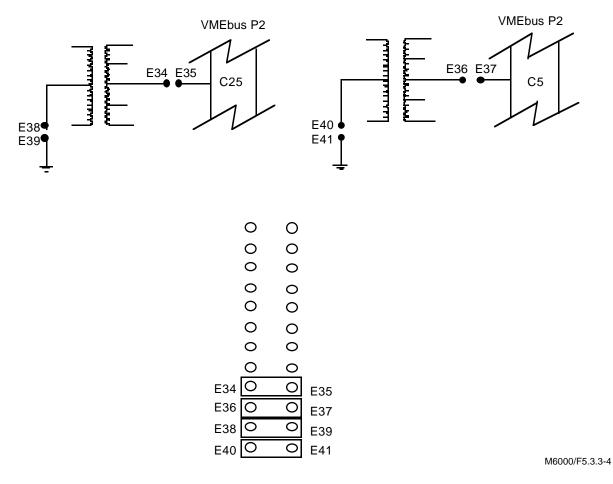

| 5.3.4-1       | Coupling Transformer Center Tap Jumpers |             |

| 5.5-1         | 1553 Bus Connector                      |             |

# LIST OF TABLES

| <u>Table</u> |                                                 | <u>Page</u> |

|--------------|-------------------------------------------------|-------------|

| 4.2.2-1      | XIO Register Group                              | 4-9         |

| 4.2.2-2      | XIO Register Map                                | 4-11        |

| 4.3-1        | VMIVME-6000 Mode Assignments                    |             |

| 4.3.1.3-1    | Diagmode Control Block                          | 4-98        |

| 4.3.2-1      | Bus Controller/Simulator Data Buffer            | 4-104       |

| 4.3.2-2      | Bus Controller Control Block                    | 4-105       |

| 4.3.3.6-1    | MRT/MON Control Block Structure                 | 4-133       |

| 4.3.3.6.1-1  | MRT/MON Header Control Block                    | 4-134       |

| 4.3.3.6.2-1  | MRT/MON RT Control Block                        | 4-149       |

| 4.3.3.6.3-1  | Subaddress Control Block                        | 4-162       |

| 4.3.3.6.4-1  | MRT/MON Data Buffers                            | 4-166       |

| 4.3.3.8.3-1  | Bit Word                                        | 4-169       |

| 4.4-1        | MRT/MON External RAM                            | 4-170       |

| 4.5.2.5-1    | Programming Error Register                      | 4-188       |

| 4.6.1-1      | Error Generation Selects                        | 4-192       |

| 4.6.1.1-1    | Manchester Type Register                        | 4-193       |

| 5.3.2-1      | VMIVME-6000 Interrupt Level Header              | 5-4         |

| 5.5-1        | Pin Assignments for the J1 Test Point Connector |             |

| 5.5-2        | Pin Assignments for the J2 Test Point Connector | 5-8         |

| 5.5-3        | 1553 Bus "B" J3 Connector                       | 5-9         |

| 5.5-4        | 1553 Bus "A" J4 Connector                       |             |

### APPENDIX A

# ASSEMBLY DRAWING, PARTS LIST, AND SCHEMATIC

# APPENDIX B

PROGRAMMING EXAMPLES

# APPENDIX C

GLOSSARY OF TERMS

# **SECTION 1**

# INTRODUCTION

### 1.1 GENERAL DESCRIPTION

The VMIVME-6000 is a microprogrammed MIL-STD-1553 interface specifically for VMEbus computers. The VMIVME-6000 is a single 6U VMEbus printed circuit board that requires only one backplane slot for operation. The 1553 bus may be customer selected (by jumpers) to be accessible through the VMEbus P2 connector or through the front panel of the board.

### 1.2 FUNCTIONAL DESCRIPTION

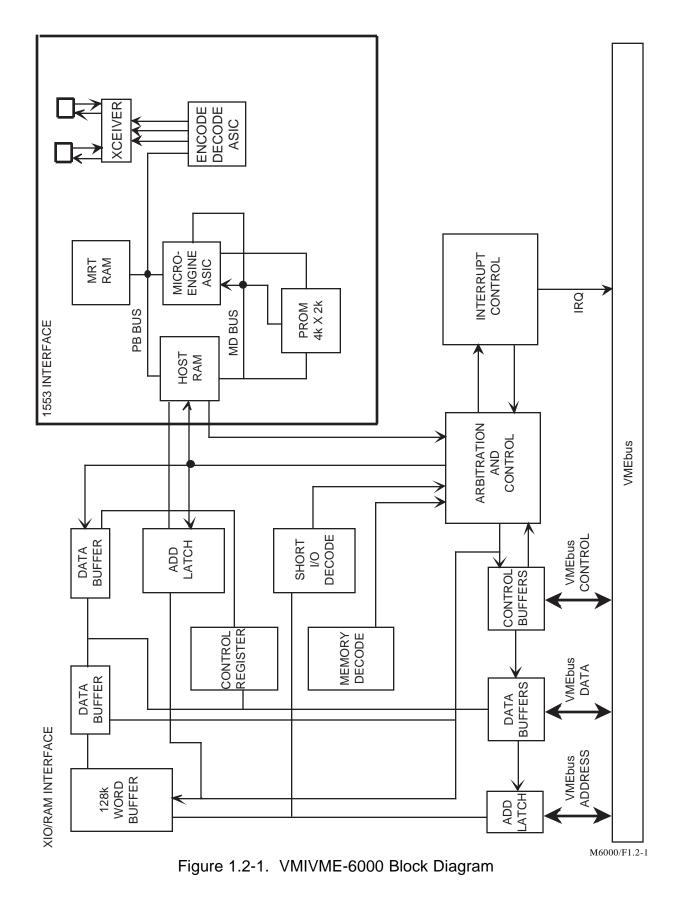

The VMIVME-6000 can function as a Bus Controller/Simulator, Multiple The VMIVME-6000 Remote Terminal and/or Monitor. is based on а microprogram-driven CMOS ASIC chip set that provides the versatility needed by tester and simulator environments, while meeting the needs of todays system power, space, and reliability requirements. The board provides 128 k x 16-bits of on-board RAM for constructing control blocks and storing transmitted and received 1553 data. Once initialized by the host, the VMIVME-6000 on-board processor can retrieve and store all control block data and commands needed for 1553 operation. The board also provides two levels of maskable interrupts to allow flexible data and exception processing. The VMIVME-6000 is compatible with the protocol of 1553B, 1553A, as well as F16, and F18 derivatives of these specifications. A block diagram of the VMIVME-6000 is shown in Figure 1.2-1.

The VMIVME-6000 VMEbus slave interface supports standard byte and word transfers. All byte accesses to the I/O registers must be done as Even/Odd since the registers are word (16-bits) length. Longword accesses to the on-board registers or memory will cause a Bus Error.

During Interrupt Acknowledge cycles, the VMIVME-6000 supports Release-on-Acknowledge (ROAK). The board will provide a 16-bit interrupt vector (programmable by the host) during the cycle.

# **1.3 REFERENCE MATERIAL LIST**

The reader should refer to The VMEbus Specification for a detailed explanation fo the VMEbus. The VMEbus Specification is available from the following source:

VITA VFEA International Trade Association 10229 N. Scottsdale Road Scottsdale, AZ 85253 (602) 951-8866

For general information regarding the Aircraft Internal Time Division Command/Response Multiplex Databus, refer to the following documents:

> MIL-STD-1553B MIL-HDBK-1553B

# SECTION 2

# PHYSICAL DESCRIPTION AND SPECIFICATIONS

REFER TO 800-006000-000 SPECIFICATION

# **SECTION 3**

# THEORY OF OPERATION

### 3.1 INTRODUCTION

The VMIVME-6000 is a single-slot, 6U Eurocard form factor MIL-STD-1553 simulator board for the VMEbus. The host interacts with the VMIVME-6000 through Configuration registers located in short I/O space to execute External Input/Output (XIO) commands, and by constructing Control Blocks (CBs) in the 128 k x 16 bit on-board memory located in standard addressing space. There is an extra 8 k x 16 bit MRT/MON mode memory (accessible through the XIO commands) which is used by the microprogram-driven CMOS ASIC chip set to access the host and ASIC supplied 1553 MRT/MON mode.

### 3.2 VMEbus INTERFACE

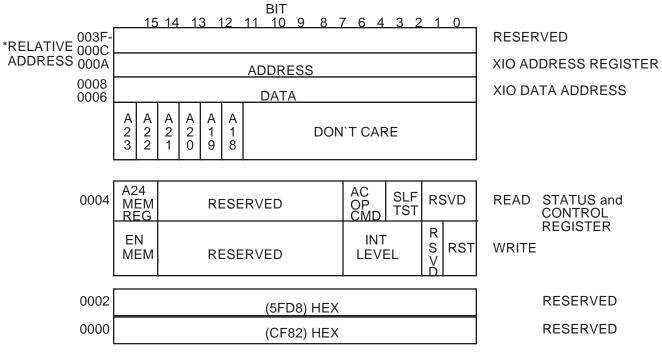

The VMIVME-6000 VMEbus slave interface has six word-length I/O Configuration register locations that are accessible by the host. These registers may be mapped on the VMEbus starting at address C000H of the short I/O space, in 64-byte increments. The VMEbus base address of these I/O registers is programmable on the header marked as E1 through E9. The Address Offset register in this short I/O space is used to offset the base address of the 128 k x 16-bit memory. This allows configuration of the memory space through software. The details of the I/O configuration registers are shown in Section 4.2. The 128 k x 16-bit memory supports standard (A24), (D16) addressing and will respond to address modifiers 3DH, 39H, 2DH, 29H.

# 3.3 REGISTERS AND MEMORY

The VMIVME-6000 Configuration registers take one VMEbus cycle in order to complete the access because they are accessed directly. The XIO registers, which are located in the ASICs, are accessed indirectly using a polling method involving the XIO Address and XIO Data registers. Basically, a read cycle consists of writing to the XIO Address register and polling a status bit until the ASIC micro-engine has a chance to write the data to the XIO Data registers at which time the host can read the valid data. An XIO write cycle consists of writing the XIO Address and Data registers and polling to verify completion.

The 8 k x 16 MRT/MON RAM is accessed indirectly from the MRT/MON RAM Address and Data XIO Registers, a type of double indirect method. The MRT/MON RAM contains information about the 32 possible RTs. The 128 k x 16-bit SRAM memory is located in standard addressing space and contains the Control Block information used by the 1553 micro-engine to control the board.

This memory is where all data that is transmitted and received will be located. Data pointers are used to locate the data buffers and an easy-to-use buffer linking method allows the user to extend the buffering to double, triple, etc. buffering.

### 3.4 1553 CONTROL

The VMIVME-6000 uses a custom 8 MIPs microengine interfaced to a 1553 encoder/decoder and the on-board memory to perform the intended 1553 processing. The simulator mode uses Control Blocks in memory that are strung together using either linked lists or table look-up methods. The VMIVME-6000 can simulate responses of RTs that are not present, inject and detect errors, and posts all pertinent information in memory.

MRT/MON mode simulates or monitors up to 32 remote terminals while supporting different aircraft protocol in different simulated RTs, error injection and detection, and buffering all information associated with each message.

# **SECTION 4**

# PROGRAMMING

#### 4.1 **PROGRAMMING THE VMIVME-6000**

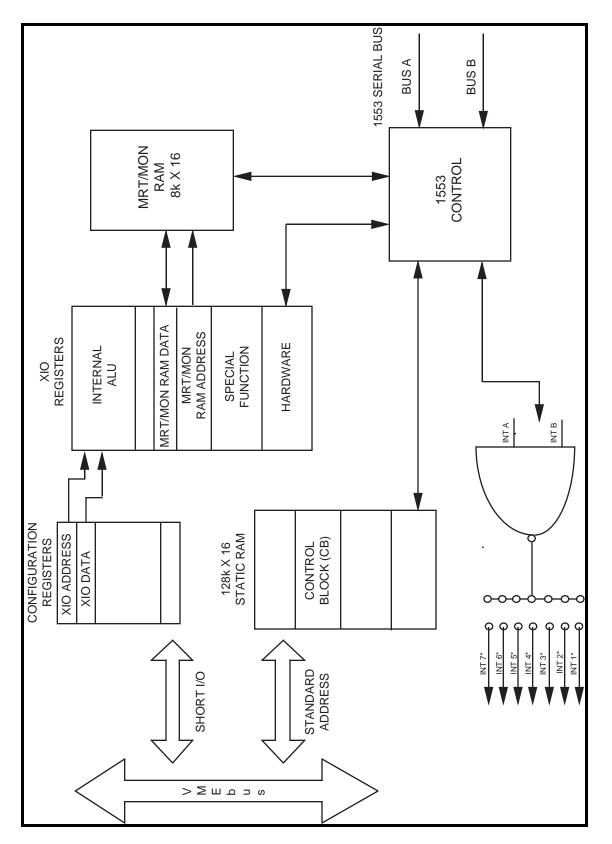

The VMIVME-6000 is programmed by accessing configuration registers to execute External Input/Output (XIO) commands, and by constructing Control Blocks (CB's) in static RAM. Once the board is programmed and started, it operates out of the on-board memory without host intervention. The VMIVME-6000 consists of several groups of registers and memory that are used to configure and control the board. These groups and their relationships are shown in Figure 4.1-1. The Configuration registers are located in short I/O space. Two XIO registers, the XIO Address register and XIO Data register, are used to access the XIO registers themselves. Two XIO registers, the MRT/MON RAM Address and Data registers, are used to access the XIO registers, the 128 k x 16 static RAM. This block of memory is located in VMEbus standard addressing space. The A and B interrupts are controlled by various registers and memory locations in the previously mentioned groups.

The following five sections will describe the registers, memory, and programming features:

4.2 REGISTERS4.3 OPERTIONAL MODES4.4 EXTERNAL MRT/MON RAM4.5 INTERRUPTS4.6 ERROR INJECTION

Various aspects are covered in multiple sections due to the fact that the sections are so interrelated.

Figure 4.1-1. VMIVME-6000 Programming Block Diagram

# 4.2 **REGISTERS**

The registers section will describe the configuration registers and the External Input/Output (XIO) registers and all their bit level definitions. The XIO address and XIO Data Configuration registers are used to access the XIO registers themselves. Figure 4.1-1 shows that a pair of XIO registers, the MRT/MON RAM address and data registers are used to access the MRT/MON RAM, but the MRT/MON RAM will be described in Section 4.4, EXTERNAL MRT/MON RAM. The Control Block structures for the on-board RAM will be discussed in Section 4.3, OPERATIONAL MODES. The VMIVME-6000 is programmed by accessing the VMIVME-6000 slave configuration registers located in short I/O space to execute External Input/Output (XIO) commands, and by constructing Control Blocks (CBs) in the 128 k x 16-bit on-board memory located in standard addressing space. Once the Board is programmed and started, it operates out of the on-board memory without host intervention. This section will deal with the Configuration registers and XIO commands.

The registers section is comprised of the following sections:

- 4.2 REGISTERS

- 4.2.1 Configuration Registers

- 4.2.2 XIO Registers

- 4.2.2.1 Hardware Registers

- 4.2.2.2 Special Function Registers

- 4.2.2.3 Internal ALU Registers

The registers section will contain a description of the particular register group and will be followed by a page for each register describing it in detail.

# 4.2.1 <u>Configuration Registers</u>

The VMIVME-6000 has 6-word length registers mapped in the short I/O space of the VMEbus, as shown in Figure 4.2-1. These registers are used by the host to program and obtain control and status information to/from the board during operation.

M6000/F4.2-1

\* ADDRESS RELATIVE TO SHORT I/O JUMPER SETTINGS.

Figure 4.2-1. VMIVME-6000 Configuration Registers

4-4

Name: Address: Address Space: Type: Status and Control Register Base Address + 0004 (Hex) VMEbus short I/O Read (Status) / Write (Control)

**Description**: A READ of this register will provide the host status of the VMIVME-6000 as defined below:

- BIT 15 A logic "one" indicates the A24 memory registers can be accessed.

- BITS14-4 Reserved.

- **BIT 3** This bit (logic "one") indicates that the board is ready to accept its full set of operational commands.

- **BIT 2** A logic "one" in this bit indicates the Board passed its self-test.

- BITS1-0 Reserved, set to zero

**Description:** Host WRITES to this register cause specific actions to be executed.

- **BIT 15** A logic "one" written to this bit will enable reads and writes to the on-board memory by the host. A logic "zero" disables memory.

- BITS14-5 Reserved, set to zero

- BITS4-2 Are written by the host to match the selected interrupt level of headers E10 E17. The 3 bits (2 through 4) form a BCD indication of the level, and are compared to A03, A02, and A01.

- BIT 1 Reserved, set to zero

- **BIT 0** Writing a logic "one" to this bit will reset all on-board logic.

Name: Address: Address Space: Type: Offset Register Base Address + 0006 (Hex) VMEbus short I/O Read / Write

**Description:** The Offset Register is programmed by the host to select the A24 VMEbus address of the on-board memory. Bit 15 of the register corresponds to address line A23, while bit 10 corresponds to address line A18. As an example, if the host wants the 256 kbytes of memory to start at \$100000, the Offset Register would be programmed to 10XX where the Xs are "don't cares".

BIT 15 A23 BIT 14 A22 BIT 13 A21 BIT 12 A20 BIT 11 A19 **BIT 10 A18** BIT 9 Don't Care, set to logic "zero" BIT 8 Don't Care, set to logic "zero" BIT 7 Don't Care, set to logic "zero" BIT 6 Don't Care, set to logic "zero" BIT 5 Don't Care, set to logic "zero" BIT 4 Don't Care, set to logic "zero" BIT 3 Don't Care, set to logic "zero" BIT 2 Don't Care, set to logic "zero" Don't Care, set to logic "zero" BIT 1 BIT 0 Don't Care, set to logic "zero" Name: Address: Address Space: Type: XIO Data Register Base Address + 0008 (Hex) VMEbus short I/O Read/Write

**Description:** All data accesses to the XIO Registers (READ and WRITE) must be through this register. Before accessing this register, the address of the XIO to be executed must be written to the XIO Address Register.

BIT 15 Data Bit 15 BIT 14 Data Bit 14 BIT 13 Data Bit 13 BIT 12 Data Bit 12 BIT 11 Data Bit 11 BIT 10 Data Bit 10 BIT 9 Data Bit 9 BIT 8 Data Bit 8 BIT 7 Data Bit 7 BIT 6 Data Bit 6 BIT 5 Data Bit 5 BIT 4 Data Bit 4 BIT 3 Data Bit 3 BIT 2 Data Bit 2 BIT 1 Data Bit 1 BIT 0 Data Bit 0

#### Name: XIO Address Register Address: Address Space: Type:

#### Base Address + 000A (Hex) VMEbus short I/O Write

**Description:** The host writes the XIO address to be executed to this register prior to accessing the XIO Data register. The addresses of the XIO commands are shown in Section 4.2.2. This register is WRITE ONLY. Note that once the XIO address is written into this register, it will remain until the host loads another XIO address, or a reset is generated. This allows the host to poll an XIO register by loading the XIO Address register once, then reading the XIO Data register until the desired results are obtained.

BIT 15 Address Bit 15 BIT 14 Address Bit 14 BIT 13 Address Bit 13 BIT 12 Address Bit 12 BIT 11 Address Bit 11 BIT 10 Address Bit 10 BIT 9 Address Bit 9 BIT 8 Address Bit 8 BIT 7 Address Bit 7 Address Bit 6 BIT 6 BIT 5 Address Bit 5 BIT 4 Address Bit 4 BIT 3 Address Bit 3 BIT 2 Address Bit 2 BIT 1 Address Bit 1 BIT 0 Address Bit 0

### 4.2.2 XIO Registers

Relative addresses 0 through 1FE(Hex) bytes are written to the XIO Address register (000AH) of the VMIVME-6000 to specify XIO registers. These registers are programmed by the host to provide configuration and operational information for the VMIVME-6000. All data written/read to/from the XIO registers is done so through the XIO Data register (0008). Table 4.2.2-1 shows the three particular types of XIO and their relative address spaces that may be executed. Table 4.2.2-2 shows a map of all the XIO registers and the page where their description is located.

| Address (Hex) | Description                |

|---------------|----------------------------|

| 0000 - 007E   | Hardware Registers         |

| 0080 - 00FE   | Special Function Registers |

| 0100 - 01FE   | Internal ALU Registers     |

|               |                            |

To access an XIO register, the host must first load the XIO Address register with the address of the desired XIO. The host may then Read or Write data to the XIO Data register, depending on the type of access. Note that once the XIO address is loaded into the XIO Address register, it will not change until the register is loaded again, or a reset is generated. This allows the host to poll an XIO register by writing the XIO Address once, then reading the XIO Data register until the desired results are obtained. The XIO Hardware registers are programmed by the host to enable specific functions such as interrupts, or to read exception pointers provided by the board. Accesses to these registers require no on-board processor (firmware) interaction to complete the cycle. Therefore, data is read or written from/to the register in one VMEbus cycle.

When the host executes a Write Special Function XIO or writes to an XIO ALU register, the actual execution of the command is done by the on-board processor **after** the VMEbus cycle for the XIO Data register access is completed. The data (if required) is latched into an internal XIO register, and a flag is set to the internal firmware requesting service of the XIO. When the VMEbus cycle is completed, the on-board processor will interpret the Special Function or ALU register, and use the data accordingly. When the function is completed, the board will set bit 11 of the Active Status register. The host can read the Active Status Register (ASR) until bit 11 is detected, or program the board to provide a B Interrupt when the XIO is complete. After the bit is detected or the B Interrupt on XIO complete is asserted, the host must read the ASR again to clear bit 11 of the ASR.

#### NOTE

NO OTHER SPECIAL FUNCTION OR ALU REGISTER XIO COMMANDS SHOULD BE PERFORMED UNTIL BIT 11 OF THE ASR IS SET (DETECTED BY THE HOST) INDICATING THE PREVIOUS SPECIAL FUNCTION XIO IS COMPLETE, AND THE ASR IS READ A SECOND TIME TO CLEAR BIT 11. Similarly, a Read Special Function or a read of an ALU register XIO involves the on-board firmware. When a READ Special Function/ALU register is performed, the board uses the address provided in the XIO Address register to identify the particular READ data. The board will complete the VMEbus read cycle, but the data in the XIO Data register will be invalid. After completion of the cycle, the on-board processor will move the requested data into the XIO Data register, and set bit 11 of the ASR. The host can read the ASR until bit 11 is detected, or program the board to provide a B Interrupt on XIO Complete. When bit 11 of the ASR is set or the B Interrupt is asserted, the host must read the ASR again to clear bit 11. The host may then execute the same Read Special Function XIO, and will receive the valid data. The same procedure, polling the ASR for bit 11 and then again reading the ASR to clear bit 11, must be followed on the second Special Function Read XIO. Special attention must be given to execution of XIO Commands while the VMIVME-6000 is "Actively" executing 1553 bus traffic. Section 4.2.4 describes the procedure for processing "Active XIO Commands".

| Hardware Register             | Write Address  | Read Address   | Page |

|-------------------------------|----------------|----------------|------|

| Control Register              | 0000           |                | 4-14 |

| Status Word "Set" Mask        | 0002           |                | 4-15 |

| Status Word "Clear" Mask      | 0004           |                | 4-15 |

| Option Register               | 0006           |                | 4-16 |

| Reserved                      | 0008 thru 0012 |                |      |

| A Interrupt Pointer           |                | 0000           | 4-17 |

| A Interrupt Map               |                | 0002           | 4-18 |

| B Interrupt Pointer           |                | 0004           | 4-19 |

| B Interrupt Map               |                | 0006           | 4-20 |

| Current Control Block Pointer |                | 0008           | 4-21 |

| Current Control Block Map     |                | 000A           | 4-22 |

| Last Posted ISR Pointer       |                | 000C           | 4-23 |

| Last Posted ISR Map           |                | 000E           | 4-24 |

| Monitor Ring Buffer Pointer   |                | 0010           | 4-25 |

| Monitor Ring Buffer Map       |                | 0012           | 4-26 |

| Last Status Word              |                | 0014           | 4-27 |

| Last Command Word             |                | 0016           | 4-28 |

| Active Status Register (ASR)  |                | 0018           | 4-29 |

| A Interrupt Vector            |                | 001A           | 4-30 |

| B Interrupt Vector            |                | 001C           | 4-31 |

| Reserved                      | 001E thru 007E | 001E thru 007E |      |

| Special Function Register     | Write Address  | Read Address   | Page |

| Start Command                 | 0080           |                | 4-33 |

| Reserved                      | 0082 thru 0084 | 0082 thru 0084 |      |

| Reset Board Command           | 0086           |                | 4-34 |

| Clear Board Command           | 0088           |                | 4-35 |

| Orderly Shutdown              | 008A           |                | 4-36 |

| Time Tag Increments           | 008C           |                | 4-37 |

| Time Tag MSW                  | 008E           | 008E           | 4-38 |

| Time Tag LSW                  | 0090           | 0090           | 4-39 |

| Time Tag Reset                | 0092           |                | 4-40 |

| Time Tag Start                | 0094           |                | 4-41 |

| Time Tag Halt                 | 0096           |                | 4-42 |

| Active Status Register (ASR)  | 0098           |                | 4-43 |

| Reserved                      | 009A thru 009E | 009A thru 009E |      |

| Manchester Error Type (MET)   | 00A0           |                | 4-44 |

| Error Bit Time                | 00A2           |                | 4-45 |

| Frame Length Register         | 00A4           |                | 4-46 |

| Reserved                      | 00A6 thru 00a8 | 00A6 thru 00A8 |      |

| MRT/MON RAM Address           | 00AA           |                | 4-47 |

| MRT/MON RAM Data              | 00AC           | 00AC           | 4-48 |

| Mil (1/MOI 1 0 (M Data        |                |                |      |

# Table 4.2.2-2. XIO Register Map

| ALU Registers                   | Write Address  | Read Address   | Page |

|---------------------------------|----------------|----------------|------|

| Control Block Address (W)       | 0100           | 0100           | 4-50 |

| Control Block Map (W)           | 0102           | 0102           | 4-51 |

| Current Buffer Pointer (R/W)    | 0104           | 0104           | 4-52 |

| DMA Disable (W)                 | 0106           | 0106           | 4-53 |

| ISR (R)                         | 0108           | 0108           | 4-54 |

| TSR (R)                         | 010A           | 010A           | 4-55 |

| A Interrupt Mask (W)            | 010C           | 010C           | 4-56 |

| B Interrupt Mask (W)            | 010E           | 010E           | 4-57 |

| Auto Retry B int Mask (W)       | 0110           | 0110           | 4-58 |

| Command Word Trigger (W)        | 0112           | 0112           | 4-59 |

| Command Word Mask (W)           | 0114           | 0114           | 4-60 |

| Reserved                        | 0116 thru 0118 | 0116 thru 0118 |      |

| Auto Retry TSR Mask             | 011A           | 011A           | 4-61 |

| Auto Retry ISR Mask             | 011C           | 011C           | 4-62 |

| ISR Mask (W)                    | 011E           | 011e           | 4-63 |

| TSR Mask (W)                    | 0120           | 0120           | 4-64 |

| Error Mask (W)                  | 0122           | 0122           | 4-65 |

| BC Pointer Table Origin (W)     | 0124           | 0124           | 4-66 |

| BC Pointer Table Length (W)     | 0126           | 0126           | 4-67 |

| Lower Error Select Word (W)     | 0128           | 0128           | 4-68 |

| Error Generation (Diagmode) (W) | 012A           | 012A           | 4-70 |

| Upper Error Select Word (W)     | 012C           | 012C           | 4-69 |

| Built In Test Word (R)          | 012E           | 012E           | 4-71 |

| DMA Timeout (W)                 | 0130           | 0130           | 4-72 |

| Reserved                        | 0132           | 0132           |      |

| Response Time (W)               | 0134           | 0134           | 4-73 |

| BC Intermessage Gap (W)         | 0136           | 0136           | 4-74 |

| Ring Buffer Address (W)         | 0138           | 0138           | 4-75 |

| Ring Buffer Map (W)             | 013A           | 013A           | 4-76 |

| Status Word 1 Mask (W)          | 013C           | 013C           | 4-77 |

| Status Word 2 Mask (W)          | 013E           | 013E           | 4-78 |

| Reserved                        | 0140 thru 0142 | 0140 thru 0142 |      |

| Word Count Error Plus (W)       | 0144           | 0144           | 4-79 |

| Word Count Error Minus (W)      | 0146           | 0146           | 4-80 |

| Major Frame Time LSW (W)        | 0148           | 0148           | 4-81 |

| Major Frame Time MSW (W)        | 014A           | 014A           | 4-82 |

| Minor Frame Time LSW (W)        | 014C           | 014C           | 4-83 |

| Minor Frame Time MSW (W)        | 014E           | 014E           | 4-84 |

| Programming Error (R)           | 0150           | 0150           | 4-85 |

| Data Word Gap (W)               | 0152           | 0152           | 4-86 |

| Dynamic BC RT Map (W)           | 0154           | 0154           | 4-87 |

| Dynamic BC RT Address (W)       | 0156           | 0156           | 4-88 |

| Dynamic BC Map (W)              | 0158           | 0158           | 4-89 |

| Dynamic BC Address (W)          | 015A           | 015A           | 4-90 |

| Dynamic DMA Disable (W)         | 015C           | 015C           | 4-91 |

# 4.2.2-2. XIO Register Map (Continued)

# 4.2.2-2. XIO Register Map (Concluded)

| ALU Registers                | Write Address  | Read Address   | Page |

|------------------------------|----------------|----------------|------|

| Dynamic Status Word Mask (W) | 015E           | 015E           | 4-92 |

| Reserved                     | 0160 thru 017E | 0160 thru 017E |      |

| Microcode Revision (R)       | 0180           | 0180           | 4-93 |

| Reserved                     | 0182 thru 0196 | 0182 thru 0196 |      |

| Lost B Interrupt Count (R)   | 0198           | 0198           | 4-94 |

| Lost B Interrupt Pointer (R) | 019A           | 019A           | 4-95 |

| Reserved                     | 019C thur 01FE | 019C thur 01FE |      |

#### <u>NOTE</u>

THE REGISTERS ARE READ/WRITE, THE (W) AND (R) ARE INCLUDED WITH THE REGISTER NAME TO INDICATE THE USAGE OF THE REGISTER.

### 4.2.2.1 <u>Hardware Registers</u>

The first 80 (Hex) bytes of the XIO map are the Hardware registers located in the Host Interface ASIC. These registers are programmed by the host to enable specific functions such as interrupts, or to read exception pointers provided by the board. Accesses to these registers require no micro-code (firmware) interaction to complete the cycle, and therefore data is read or written from/to the register in one VMEbus cycle. The following pages will show the functions and addresses of the hardware registers.

Choose Hardware Registers in the following manner:

- a. Write address of chosen hardware register into the XIO Address register located at offset 000A (Hex) in VMEbus short I/O space.

- b. <u>Register Write:</u> Write desired data to the XIO Data register, located at offset 0008 (Hex) in VMEbus short I/O space.

<u>Register Read:</u> Read data from the XIO Data register, located at offset 0008 (Hex) in VMEbus short I/O space.

# XIO REGISTERS HARDWARE

Name: Address: Address Space: Type: Control Register 0000 (Hex) XIO Write

**Description:** The Control Register allows easy host access to hardware functions of the VMIVME-6000. The Control Register is write only.

- **BIT 15 Halt Immediately-** Setting this bit to a logic "one" stops the VMIVME-6000 immediately regardless of its operation. The board will perform its "self-test" and return to OFF mode.

- **BIT 14 Enable A Interrupts**

- BIT 13 Enable B Interrupts

- BIT 12 Generate B Interrupt on Active XIO complete

- **BIT 11 Clear A Interrupt Pointer-** A Logic "one" set in any of bits 7-11 will "clear" the particular Pointer register.

- **BIT 10 Clear B Interrupt Pointer**

- BIT 9 Clear Last Data Buffer/Control Block Pointer

- BIT 8 Clear Pointer to Last Posted ISR

- BIT 7 Clear Ring Buffer Pointer

- BIT 6 Not Used

- **BIT 5 Clear ASR-** Setting this bit to a logic "1" will clear the Active Status register (ASR).

- **BIT 4 Enable Vectored Interrupts**

- BIT 3 Reserved, set to logic "zero"

- BIT 2 Reserved, set to logic "zero"

- BIT 1 Reserved, set to logic "zero"

- BIT 0 Reserved, set to logic "zero"

#### XIO REGISTERS HARDWARE

Name: Address: Address Space: Type: Status Word Set Mask/Clear Mask Set Mask: 0002 (Hex), Clear Mask: 0004 (Hex) XIO Write

**Description:** The VMIVME-6000 Status Word Set Mask and its companion register the Clear Mask provide the host a global means to "set" and/or "clear" MIL-STD-1553 Status Word (SW) bits (excluding the Terminal Address) "on the fly" when the board is operating in MRT mode. **After** each MIL-STD-1553 status word transmission, the VMIVME-6000 will set and/or clear bits in the SW skeleton based on the Status Word Set and Status Word Clear registers. If these registers are left "zero", there will be no "real-time" changing of the Status Word. These two registers work with the individual RT Status Word Set and Clear Mask registers located in the MRT RAM space (Section 4.4), to provide the actual set/clear function.

A logic "one" set in a particular bit of the status word "set" mask will cause the corresponding bit to be set in the SW skeleton. Likewise, a logic "one" set in the status word "clear" mask will cause the corresponding bit to be cleared from the status word skeleton. If both bits are set, the "clear" will have priority.

\* The status word skeletion bits are the actual bits the firmware will use to transmit on the MIL-STD-1553 bus.

| BIT 15 | Reserved, set to logic "zero" | BIT | 7 | Status Word Bit 7 |

|--------|-------------------------------|-----|---|-------------------|

| BIT 14 | Reserved, set to logic "zero" | BIT | 6 | Status Word Bit 6 |

| BIT 13 | Reserved, set to logic "zero" | BIT | 5 | Status Word Bit 5 |

| BIT 12 | Reserved, set to logic "zero" | BIT | 4 | Status Word Bit 4 |

| BIT 11 | Reserved, set to logic "zero" | BIT | 3 | Status Word Bit 3 |

| BIT 10 | Status Word Bit 10            | BIT | 2 | Status Word Bit 2 |

| BIT 9  | Status Word Bit 9             | BIT | 1 | Status Word Bit 1 |

| BIT 8  | Status Word Bit 8             | BIT | 0 | Status Word Bit 0 |

#### NOTE:

The Status Word Skeleton is updated after each MIL-STD-1553 transmission. When the user sets or clears a bit, there will be a message transmission lag until the skeleton is updated.

### XIO REGISTERS HARDWARE

Name: Address: Address Space: Type: Option Register 0006 (Hex) XIO Write

**Description:** This register contains additional host selected options.

- BIT 15 Reserved, set to logic "zero"

- **BIT 14** Enable BC Pointer Table Bus Controller will get Links from a table (as opposed to the Control Block). The Bus Control Table Pointer and Bus Control Table Length ALU register should be programmed to use this option.

- BIT 13 A Interrupt on B Interrupt Not Serviced

- **BIT 12 Post Zero ISR\*** A logic "one" in this bit will cause the board to post all ISRs\* including those with no bits set.

- BIT 11 Transmit On Already Active 1553 Bus If this bit is set, the VMIVME-6000 will not check the 1553 bus to ensure "no activity" before it transmits.

- **BIT 10 Post Zero TSR\*\*** A logic "one" in this bit will cause the board to post all TSRs including those with no bits set.

- **BIT 9** Set Terminal Flag on Loop Error Set terminal flag in MIL-STD-1553 Status Word if loop-around error occurs. (MRT mode)

- BIT 8 Initialize All 32 RTs Using One Set of RT Control/Subaddress Blocks -

BIOCKS -

If set, during MRT initialization, board will initialize all RT parameters except the terminal address using the information from one host- supplied set of Header Block, RT Control Block, and Subaddress Blocks. Useful for quick set-up of board to monitor or simulate all bus traffic.

- BIT 7 Continue on DMA Error

- **BIT 6** Inhibit Transmitter Timeout Disable transmitter timeout circuitry (all modes).

- **BIT 5 Instrumentation BIT -** The board uses the instrumentation bit to validate command and status responses.

- BIT 4 B Interrupt after MRT/MON Initialization Complete

- BIT 3 Subsystem Flag Set on DMA Error (MRT mode only)

- BIT 2 Reserved, set to logic "zero"

- BIT 1 Reserved, set to logic "zero"

- BIT 0 Reserved, set to logic "zero"

\*ISR: Interrupt Status Register

\*\***TSR**: Transmission Status Register

Name: Address: Address Space: Type: "A" Interrupt Pointer 0000 (Hex) XIO Read

**Description:** The VMIVME-6000 provides a 16-bit pointer of the on-board memory that contains the address of the last data buffer (MRT/MON mode) or Control Block (Simulator BC) that caused an A level interrupt.

BIT 15 Address Bit 15 BIT 14 Address Bit 14 BIT 13 Address Bit 13 BIT 12 Address Bit 12 BIT 11 Address Bit 11 BIT 10 Address Bit 10 BIT 9 Address Bit 9 BIT 8 Address Bit 8 BIT 7 Address Bit 7 BIT 6 Address Bit 6 BIT 5 Address Bit 5 BIT 4 Address Bit 4 BIT 3 Address Bit 3 BIT 2 Address Bit 2 BIT 1 Address Bit 1 BIT 0 Address Bit 0

#### NOTE

Name: Address: Address Space: Type: "A" Interrupt Map 0002 (Hex) XIO Read

**Description:** The VMIVME-6000 provides a 4-bit map of the on-board memory that contains the address of the last data buffer (MRT/MON mode) or Control Block (Simulator BC) that caused an A level interrupt.

BIT 15 Reserved, set to logic "zero" BIT 14 Reserved, set to logic "zero" BIT 13 Reserved, set to logic "zero" BIT 12 Reserved, set to logic "zero" BIT 11 Reserved, set to logic "zero" BIT 10 Reserved, set to logic "zero" BIT 9 Reserved, set to logic "zero" BIT 8 Reserved, set to logic "zero" BIT 7 Reserved, set to logic "zero" BIT 6 Reserved, set to logic "zero" BIT 5 Reserved, set to logic "zero" BIT 4 Reserved, set to logic "zero" BIT 3 Address Bit 19 BIT 2 Address Bit 18 BIT 1 Address Bit 17 BIT 0 Address Bit 16

<u>NOTE</u>

Name: Address: Address Space: Type: "B" Interrupt Pointer 0004 (Hex) XIO Read

**Description:** The VMIVME-6000 provides a 16-bit pointer of the on-board memory that contains the address of the last data buffer (MRT/MON mode) or Control Block (Simulator, BC) that caused a B level interrupt.

BIT 15 Address Bit 15 BIT 14 Address Bit 14 BIT 13 Address Bit 13 BIT 12 Address Bit 12 BIT 11 Address Bit 11 BIT 10 Address Bit 10 BIT 9 Address Bit 9 BIT 8 Address Bit 8 BIT 7 Address Bit 7 BIT 6 Address Bit 6 BIT 5 Address Bit 5 BIT 4 Address Bit 4 BIT 3 Address Bit 3 BIT 2 Address Bit 2 BIT 1 Address Bit 1 BIT 0 Address Bit 0

#### NOTE

Name: Address: Address Space: Type: "B" Interrupt map 0006 (Hex) XIO Read

**Description:** The VMIVME-6000 provides a 4-bit map of the on-board memory that contains the address of the last data buffer (MRT/MON mode) or Control Block (Simulator, BC) that caused a B level interrupt.

BIT 15 Reserved, set to logic "zero" BIT 14 Reserved, set to logic "zero" BIT 13 Reserved, set to logic "zero" BIT 12 Reserved, set to logic "zero" BIT 11 Reserved, set to logic "zero" BIT 10 Reserved, set to logic "zero" BIT 9 Reserved, set to logic "zero" BIT 8 Reserved, set to logic "zero" BIT 7 Reserved, set to logic "zero" BIT 6 Reserved, set to logic "zero" BIT 5 Reserved, set to logic "zero" BIT 4 Reserved, set to logic "zero" BIT 3 Address Bit 19 BIT 2 Address Bit 18 BIT 1 Address Bit 17 BIT 0 Address Bit 16

#### NOTE

Name: Address: Address Space: Type: Current Control Block Pointer 0008 (Hex) XIO Read

**Description:** In **Bus Controller Mode (Simulator mode)**, the VMIVME-6000 provides a 16-bit pointer that contains the on-board memory address of the current control block being executed. In **MRT Mode**, it is the last data buffer to be updated.

BIT 15 Address Bit 15 BIT 14 Address Bit 14 BIT 13 Address Bit 13 BIT 12 Address Bit 12 BIT 11 Address Bit 11 BIT 10 Address Bit 10 BIT 9 Address Bit 9 BIT 8 Address Bit 8 BIT 7 Address Bit 7 BIT 6 Address Bit 6 BIT 5 Address Bit 5 BIT 4 Address Bit 4 BIT 3 Address Bit 3 BIT 2 Address Bit 2 BIT 1 Address Bit 1 BIT 0 Address Bit 0

#### <u>NOTE</u>

Name: Address: Address Space: Type: Current Control Block Map 000A (Hex) XIO Read

**Description:** In **Bus Control Mode (Simulator mode)**, the VMIVME-6000 provides a 4-bit map that contains the on-board memory address of the current control block being executed. In **MRT Mode**, it is the last data buffer to be updated.

| BIT |    | Reserved, set to logic "zero" |

|-----|----|-------------------------------|

| BIT | 14 | Reserved, set to logic "zero" |

| BIT | 13 | Reserved, set to logic "zero" |

| BIT | 12 | Reserved, set to logic "zero" |

| BIT | 11 | Reserved, set to logic "zero" |

| BIT | 10 | Reserved, set to logic "zero" |

| BIT | 9  | Reserved, set to logic "zero" |

| BIT | 8  | Reserved, set to logic "zero" |

| BIT | 7  | Reserved, set to logic "zero" |

| BIT | 6  | Reserved, set to logic "zero" |

| BIT | 5  | Reserved, set to logic "zero" |

| BIT | 4  | Reserved, set to logic "zero" |

| BIT | 3  | Address Bit 19                |

| BIT | 2  | Address Bit 18                |

| BIT | 1  | Address Bit 17                |

| BIT | 0  | Address Bit 16                |

#### NOTE

EACH OF THE POINTER AND MAP COMBINATIONS DISCUSSED ABOVE MAKE UP A 20-bit ADDRESS. THE UPPER 4-bits OF THE 24-bit ADDRESS (IF USED) MUST BE KEPT AS AN OFFSET BY THE HOST AND ADDED TO THE POINTER/MAP ADDRESS.

Name: Address: Address Space Type: Last Posted ISR\* Pointer 000C (Hex) XIO Read

**Description:** This register contains a 16-bit pointer to the on-board memory address of the last posted nonzero Interrupt Status Register as determined by the ISR mask **(all modes)**.

BIT 15 Address Bit 15 BIT 14 Address Bit 14 BIT 13 Address Bit 13 BIT 12 Address Bit 12 BIT 11 Address Bit 11 BIT 10 Address Bit 10 BIT 9 Address Bit 9 BIT 8 Address Bit 8 BIT 7 Address Bit 7 BIT 6 Address Bit 6 BIT 5 Address Bit 5 BIT 4 Address Bit 4 BIT 3 Address Bit 3 BIT 2 Address Bit 2 BIT 1 Address Bit 1 BIT 0 Address Bit 0

#### NOTE

EACH OF THE POINTER AND MAP COMBINATIONS DISCUSSED ABOVE MAKE UP A 20-bit ADDRESS. THE UPPER 4-bits OF THE 24-bit ADDRESS (IF USED) MUST BE KEPT AS AN OFFSET BY THE HOST AND ADDED TO THE POINTER/MAP ADDRESS.

**\*ISR**: INTERRUPT STATUS REGISTER

Name: Address: Address Space: Type: Last Posted ISR\* Map 000E (Hex) XIO Read

**Description:** This register contains a 4-bit map to the on-board memory address of the last posted non zero ISR as determined by the ISR mask **(all modes)**.

| BIT | 15 | Reserved, set to logic "zero" |

|-----|----|-------------------------------|

| BIT | 14 | Reserved, set to logic "zero" |

| BIT | 13 | Reserved, set to logic "zero" |

| BIT | 12 | Reserved, set to logic "zero" |

| віт | 11 | Reserved, set to logic "zero" |

| BIT |    | Reserved, set to logic "zero" |

| BIT | 9  | Reserved, set to logic "zero" |

| BIT | 8  | Reserved, set to logic "zero" |

| віт | 7  | Reserved, set to logic "zero" |

| BIT | 6  | Reserved, set to logic "zero" |

| BIT | 5  | Reserved, set to logic "zero" |

| BIT | 4  | Reserved, set to logic "zero" |

| віт | 3  | Address Bit 19                |

|     | 2  | Address Bit 18                |

| BIT | _  |                               |

|     | -  | Address Bit 17                |

| BIT | 0  | Address Bit 16                |

#### <u>NOTE</u>

EACH OF THE POINTER AND MAP COMBINATIONS DISCUSSED ABOVE MAKE UP A 20-bit ADDRESS. THE UPPER 4-bits OF THE 24-bit ADDRESS (IF USED) MUST BE KEPT AS AN OFFSET BY THE HOST AND ADDED TO THE POINTER/MAP ADDRESS.

\*ISR: INTERRUPT STATUS REGISTER

Name: Address: Address Space: Type: Monitor Ring Buffer Pointer 0010 (Hex) XIO Read

**Description:** If the board is operating in **Monitor Mode**, this register will contain the lower 16-bit on-board memory address of the last entry in the monitor ring buffer.

BIT 15 Address Bit 15 BIT 14 Address Bit 14 BIT 13 Address Bit 13 BIT 12 Address Bit 12 BIT 11 Address Bit 11 BIT 10 Address Bit 10 BIT 9 Address Bit 9 BIT 8 Address Bit 8 BIT 7 Address Bit 7 BIT 6 Address Bit 6 BIT 5 Address Bit 5 BIT 4 Address Bit 4 BIT 3 Address Bit 3 BIT 2 Address Bit 2 BIT 1 Address Bit 1 BIT 0 Address Bit 0

#### <u>NOTE</u>

EACH OF THE POINTER AND MAP COMBINATIONS DISCUSSED ABOVE MAKE UP A 20-bit ADDRESS. THE UPPER 4-bits OF THE 24-bit ADDRESS (IF USED) MUST BE KEPT AS AN OFFSET BY THE HOST AND ADDED TO THE POINTER/MAP ADDRESS.

Name: Address: Address Space: Type: Monitor Ring Buffer Map 0012 (Hex) XIO Read

**Description:** If the board is operating in **Monitor Mode**, this register will contain the upper 4-bit on-board memory address of the last entry in the monitor ring buffer.

BIT 15 Reserved, set to logic "zero" BIT 14 Reserved, set to logic "zero" BIT 13 Reserved, set to logic "zero" BIT 12 Reserved, set to logic "zero" BIT 11 Reserved, set to logic "zero" BIT 10 Reserved, set to logic "zero" BIT 9 Reserved, set to logic "zero" BIT 8 Reserved, set to logic "zero" BIT 7 Reserved, set to logic "zero" BIT 6 Reserved, set to logic "zero" BIT 5 Reserved, set to logic "zero" BIT 4 Reserved, set to logic "zero" BIT 3 Address Bit 19 BIT 2 Address Bit 18 BIT 1 Address Bit 17 BIT 0 Address Bit 16

#### <u>NOTE</u>

EACH OF THE POINTER AND MAP COMBINATIONS DISCUSSED ABOVE MAKE UP A 20-bit ADDRESS. THE UPPER 4-bits OF THE 24-bit ADDRESS (IF USED) MUST BE KEPT AS AN OFFSET BY THE HOST AND ADDED TO THE POINTER/MAP ADDRESS.

Name: Address: Address Space: Type: Last Status Word 0014 (Hex) XIO Read

**Description:** This register will contain the Last Status Word updated by the board as a remote terminal.

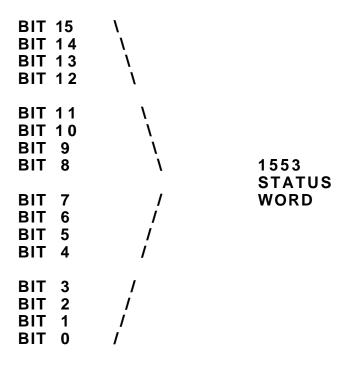

| BIT<br>BIT<br>BIT<br>BIT | 1 4<br>1 3         | \<br>\<br>\<br>\ |                |

|--------------------------|--------------------|------------------|----------------|

| BIT<br>BIT<br>BIT<br>BIT | 11<br>10<br>9<br>8 |                  | 1553<br>Status |

| BIT<br>BIT<br>BIT<br>BIT | 7<br>6<br>5<br>4   | <br> <br> <br>   | WORD           |

| BIT<br>BIT<br>BIT<br>BIT | 3<br>2<br>1<br>0   | /<br>/<br>/      |                |

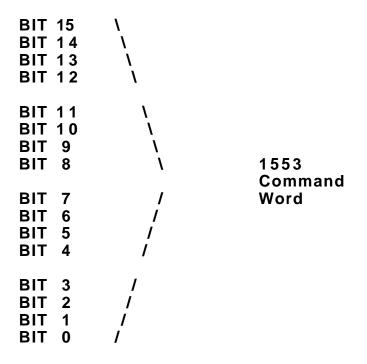

Name: Address: Address Space: Type: Last Command Word 0016 (Hex) XIO Read

**Description:** This register will contain the Last Command Word received by the board as a remote terminal.

Name:Active Status Register (ASR)Address:0018 (Hex)Address Space:XIOType:Read (Write performed at Special Function XIO 0098)

**Description:** The ASR provides the VMIVME-6000's current status. This register is Read/Write and may be read from this address and written to as a Special Function XIO 0098 (Hex) (see Special Function XIO, Section 4.2.2.2). The ASR is cleared upon Power-Up Reset and may be cleared by the host via a CLEAR Command (0088 Hex) or by setting bit 5 of the Control register (000 Hex). See Control Register, Hardware registers this section and Clear Command, Special Function registers Section 4.2.2.2.

- **BIT 15 Board Active -** The board is busy executing control blocks, self test, or lengthy XIO commands such as a "clear".

- **BIT 14** A Interrupt Requested A match of the A Interrupt Mask and a ISR has occurred for a previous message.

- **BIT 13 B** Interrupt Requested A match of the B Interrupt Mask and a ISR hasoccurred for a previous message.

- **BIT 12 B** Interrupt Requested on Active XIO Complete The board has generated a B interrupt to signal completion of a XIO.

- BIT 11 Active XIO Finished The VMIVME-6000 has completed servicing an XIO command.

- **BIT 10 ALU Self-Test Failed -** The VMIVME-6000 has determined that there is a problem with the internal ALU, Sequencer, or RAM.

- **BIT 9** Host Self-Test Failed The VMIVME-6000 has failed BIT in communication with the host interface ASIC.

- **BIT 8** XMIT/RCV Self-Test Failed "Loopback " of transmitted data did not match, or there was a transmission error.

- **BIT 7 Orderly Shutdown -** A logic "one" in this bit signals that the host has requested the board to "shutdown" and return to OFF mode.

- BITS 6, 5, 4 Current Mode

- 0 OFF

- 1 Bus Controller/Simulator

- 2 Diagmode

- 4 MRŤ/MON

- **BIT 3 B Interrupt Not Serviced -** The current B Interrupt was asserted before the previous B Interrupt was serviced.

- BIT 2 Self-Test Complete

- BIT 1 Bit Failed An internal VMIVME-6000 BIT failed.

- **BIT 0 Error -** The VMIVME-6000 has detected what it considers an error. (Maskable via the Error Mask except during Power-up)

Name: Address: Address Space: Type: "A" Interrupt Vector Register 001A (Hex) XIO Read/Write

**Description:** The VMIVME-6000 provides vector interrupt capability during VMEbus interrupt acknowledge cycles. The host selected vectors for the A level interrupts should be written to this location during initialization of the board. A detailed discussion of interrupts is included in Section 4.5.

BIT 15 Vector Bit 15 BIT 14 Vector Bit 14 BIT 13 Vector Bit 13 BIT 12 Vector Bit 12 BIT 11 Vector Bit 11 BIT 10 Vector Bit 10 BIT 9 Vector Bit 9 BIT 8 Vector Bit 8 BIT 7 Vector Bit 7 Vector Bit 6 BIT 6 BIT 5 Vector Bit 5 BIT 4 Vector Bit 4 BIT 3 Vector Bit 3 Vector Bit 2 BIT 2 BIT 1 Vector Bit 1 BIT 0 Vector Bit 0

Name: Address: Address Space: Type: "B" Interrupt Vector Register 001C (Hex) XIO Read/Write

**Description:** The VMIVME-6000 provides vector interrupt capability during VMEbus interrupt acknowledge cycles. The host selected vectors for the B level interrupts should be written to these locations during initialization of the board. A detailed discussion of interrupts is included in Section 4.5.

BIT 15 Vector Bit 15 BIT 14 Vector Bit 14 BIT 13 Vector Bit 13 BIT 12 Vector Bit 12 BIT 11 Vector Bit 11 BIT 10 Vector Bit 10 BIT 9 Vector Bit 9 BIT 8 Vector Bit 8 BIT 7 Vector Bit 7 BIT 6 Vector Bit 6 BIT 5 Vector Bit 5 BIT 4 Vector Bit 4 BIT 3 Vector Bit 3 2 Vector Bit 2 BIT BIT 1 Vector Bit 1 BIT 0 Vector Bit 0

# 4.2.2.2 Special Function Registers

The next 80 (Hex) bytes of the VMIVME-6000 make up the Special Function Registers. These registers are accessed by the host to instruct the board to perform a special function such as a START, SHUTDOWN, or CLEAR. Accesses to these registers require interaction with the on-board firmware. For this reason, the Special Functions must be executed in a specific manner.

When the host executes a Write Special Function, the actual execution of the command is done by the microcode AFTER the VMEbus cycle is completed for the write to the XIO Data Register. The data (if required) is latched into an internal XIO Register, and a flag is set to the internal firmware requesting service of the XIO. When the VMEbus cycle is completed, the on-board processor will interpret the Special Function and use the data accordingly. When the function is completed, the board will set bit 11 of the ASR. The host can poll the ASR until bit 11 is detected. After the bit is detected, the host must read the ASR again to clear bit 11. No other XIO commands should be performed until bit 11 of the ASR is set (detected by the host) indicating the previous Special Function XIO is complete, and the ASR is read a second time to clear bit 11.

Similarly, a Read Special Function XIO involves the on-board firmware. When a Read Special Function is performed, the board uses the address provided in the XIO Address register to identify the particular Read data. The board will complete the VMEbus read cycle, but the data will be invalid. After completion of the cycle. The on-board processor will move the requested data into the XIO register, and set bit 11 of the ASR. The host must read the ASR until bit 11 is detected. When bit 11 of the ASR is set, the host must read the ASR again to clear bit 11. The host may then execute the same READ Special Function XIO, and will receive the valid data. The same procedure, polling the ASR for bit 11 and then again reading the ASR to clear bit 11, must be followed on the second Special Function READ XIO. Special Function XIO register addresses and descriptions are shown in the following pages.

## Name: Address: Address Space: Type:

Start Command 0080 (Hex) XIO Write

**Description:** The START Command places the board in "active mode", executing Control Blocks. The desired mode should be included as data when the XIO START Command is written to the board. The valid choices for the Start Command are 1- Simulator 2- Diagmode, 3- MRT/MON with initialization, 4- MRT/MON without initialization. Both MRT/MON modes will display a "4" in the Active Status Register (ASR). For more information on operational modes, see Section 4.3.

BIT 15 Reserved, set to zero BIT 14 Reserved, set to zero BIT 13 Reserved, set to zero BIT 12 Reserved, set to zero BIT 11 Reserved, set to zero BIT 10 Reserved, set to zero BIT 9 Reserved, set to zero BIT 8 Reserved, set to zero BIT 7 Reserved, set to zero BIT 6 Reserved, set to zero BIT 5 Reserved, set to zero BIT 4 Reserved, set to zero BIT 3 Reserved, set to zero BIT 2 Bits 2,1,0 Desired Mode BIT 1 1 - Simulator/Bus Controller BIT 0 2 - Diagmode 4 - MRT/MON: w/initialization 3 - MRT/MON: w/o initialization (quick start) Example (for less confusion) Dita 2 1 0 desired meda

|       | <u>Bits 2, 1, 0</u> | desired mode       |

|-------|---------------------|--------------------|

| Bit 2 | 001 (1)             | Simulator/B        |

| Bit 1 | 010 (2)             | Diagmode           |

| Bit 0 | 011 (3)             | MRT/MON : W/INIT   |

|       | 100 (́4)́           | MRT/MON : W/O INIT |

Name: Address: Address Space: Type: Reset board Command 0086 (Hex) XIO Write

**Description:** The Reset board Command clears all VMIVME-6000 ASIC logic. A reset command may be executed after completion of the VMIVME-6000 self-test at power-up.