## **VMIVME-6016**

## 16-CHANNEL INTELLIGENT ASYNCHRONOUS SERIAL CONTROLLER (IASC)

**PRODUCT MANUAL**

DOCUMENT NO. 500-006016-000 D

Revised May 7, 1997

VME MICROSYSTEMS INTERNATIONAL CORPORATION 12090 SOUTH MEMORIAL PARKWAY HUNTSVILLE, AL 35803-3308 (205) 880-0444 FAX: (205) 882-0859 (800) 322-3616

## **COPYRIGHT AND TRADEMARKS**

© Copyright January 1996. The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

AMXbus', BITMODULE', COSMODULE', DMAbus', IOWorks', IOWorks Access', IOWorks Foundation', IOWorks man figure<sup>™</sup>, IOWorks Manager<sup>™</sup>, IOWorks Server<sup>™</sup>, MAGICWARE', MEGAMODULE', PLC ACCELERATOR (ACCELERATION)', Quick Link', RTnet<sup>™</sup>, Soft Logic Link', SRTbus', TESTCAL', "The Next Generation PLC"', The PLC Connection', TURBOMODULE', UCLIO', UIOD', UPLC', Visual IOWorks', Visual Soft Logic Control(ler)<sup>™</sup>, VMEaccess', VMEmanager', VMEmonitor', VMEnet', VMEnet II', and VMEprobe' are trademarks of VMIC.

**UIOC**®

Winl IIOC

(I/O man figure)

(IOWorks man figure)

The I/O man figure, UIOC<sup>®</sup>, and *WinUIOC*<sup>®</sup> are registered trademarks of VMIC.

Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, and XENIX are registered trademarks and Windows NT is a trademark of Microsoft Corporation.

MMX is a trademark and Pentium is a registered trademark of Intel Corporation.

Other registered trademarks are the property of their respective owners.

#### VMIC

All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless granted express written permission from VMIC.

|                                               | R                                | REC                   | CORD OF REVISIONS           |    |              |                |

|-----------------------------------------------|----------------------------------|-----------------------|-----------------------------|----|--------------|----------------|

| REVISION<br>LETTER                            | DATE                             |                       | PAGES INVOLVED              |    | CHANGE       | NUMBER         |

| А                                             | 02/07/96                         | Release               |                             |    | 96-0         | 125            |

| В                                             | 02/19/97                         | Cover, pag<br>and 5-5 | ges ii, 1-1, 1-2, 3-2, 3-3, |    | 97-02        | 205            |

| С                                             | 05/12/97                         | Cover, Pag            | ges ii and 5-4              |    | 97-0         | 405            |

|                                               |                                  |                       |                             |    |              |                |

|                                               |                                  |                       |                             |    |              |                |

|                                               |                                  |                       |                             |    |              |                |

|                                               |                                  |                       |                             |    |              |                |

|                                               |                                  |                       |                             |    |              |                |

|                                               |                                  |                       |                             |    |              |                |

|                                               |                                  |                       |                             |    |              |                |

|                                               |                                  |                       |                             |    |              |                |

|                                               |                                  |                       |                             |    |              |                |

|                                               |                                  |                       |                             |    |              |                |

| VMIC<br>12090 South Mem<br>Huntsville, AL 358 | orial Parkway<br>03-3308 • (205) | 880-0444              | DOC. NO. 500-003419-00      | 00 | REV LTR<br>C | PAGE NO.<br>ii |

## SAFETY SUMMARY

THE FOLLOWING GENERAL SAFETY PRECAUTIONS MUST BE OBSERVED DURING ALL PHASES OF THE OPERATION, SERVICE, AND REPAIR OF THIS PRODUCT. FAILURE TO COMPLY WITH THESE PRECAUTIONS OR WITH SPECIFIC WARNINGS ELSEWHERE IN THIS MANUAL VIOLATES SAFETY STANDARDS OF DESIGN, MANUFACTURE, AND INTENDED USE OF THIS PRODUCT. VME MICROSYSTEMS INTERNATIONAL CORPORATION ASSUMES NO LIABILITY FOR THE CUSTOMER'S FAILURE TO COMPLY WITH THESE REQUIREMENTS.

#### **GROUND THE SYSTEM**

To minimize shock hazard, the chassis and system cabinet must be connected to an electrical ground. A three-conductor AC power cable should be used. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet.

#### DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE

Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.

#### KEEP AWAY FROM LIVE CIRCUITS

Operating personnel must not remove product covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### DO NOT SERVICE OR ADJUST ALONE

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### DO NOT SUBSTITUTE PARTS OR MODIFY SYSTEM

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to VME Microsystems International Corporation for service and repair to ensure that safety features are maintained.

#### DANGEROUS PROCEDURE WARNINGS

Warnings, such as the example below, precede only potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

WARNING

DANGEROUS VOLTAGES, CAPABLE OF CAUSING DEATH, ARE PRESENT IN THIS SYSTEM. USE EXTREME CAUTION WHEN HANDLING, TESTING, AND ADJUSTING.

## SAFETY SYMBOLS

## GENERAL DEFINITIONS OF SAFETY SYMBOLS USED IN THIS MANUAL

Instruction manual symbol: the product is marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect against damage to the system.

Indicates dangerous voltage (terminals fed from the interior by voltage exceeding 1000 volts are so marked).

Protective conductor terminal. For protection against electrical shock in case of a fault. Used with field wiring terminals to indicate the terminal which must be connected to ground before operating equipment.

OR

Low-noise or noiseless, clean ground (earth) terminal. Used for a signal common, as well as providing protection against electrical shock in case of a fault. Before operating the equipment, terminal marked with this symbol must be connected to ground in the manner described in the installation (operation) manual.

Frame or chassis terminal. A connection to the frame (chassis) of the equipment which normally includes all exposed metal structures.

Alternating current (power line).

Direct current (power line).

Alternating or direct current (power line).

WARNING

The WARNING sign denotes a hazard. It calls attention to a procedure, a practice, a condition, or the like, which, if not correctly performed or adhered to, could result in injury or death to personnel.

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, a practice, a condition, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the system.

**NOTE:** The NOTE sign denotes important information. It calls attention to a procedure, a practice, a condition or the like, which is essential to highlight.

## **VMIVME-6016 16-CHANNEL INTELLIGENT ASYNCHRONOUS SERIAL CONTROLLER (IASC)**

## **TABLE OF CONTENTS**

<u>Page</u>

#### SECTION 1. INTRODUCTION

| 1.1 | INTRODUCTION            | 1-1 |

|-----|-------------------------|-----|

| 1.2 | FEATURES                | 1-1 |

| 1.3 | REFERENCE MATERIAL LIST | 1-2 |

#### SECTION 2. PHYSICAL DESCRIPTION AND SPECIFICATIONS

#### SECTION 3. THEORY OF OPERATION

| 3.1   | OPERATIONAL OVERVIEW         | 3-1 |

|-------|------------------------------|-----|

| 3.2   | RS-232 CONNECTIONS           | 3-1 |

| 3.3   | CONTROL BLOCKS AND REGISTERS | 3-2 |

| 3.4   | VMEbus INTERFACE             | 3-2 |

| 3.5   | LOCAL BUS                    | 3-3 |

| 3.5.1 | CPU                          | 3-4 |

| 3.5.2 | ROM                          | 3-4 |

| 3.5.3 | RAM                          | 3-4 |

| 3.5.4 | UARTs                        | 3-5 |

| 3.5.5 | Jumpers                      | 3-5 |

| 3.5.6 | Glue Logic                   | 3-6 |

| 3.6   | VMEbus TIMER                 | 3-6 |

#### SECTION 4. PROGRAMMING

| 4.1   | OVERVIEW                                    |  |

|-------|---------------------------------------------|--|

| 4.2   | GLOBAL REGISTER MAP                         |  |

| 4.2.1 | Board ID Register (BRD_ID)                  |  |

| 4.2.2 | POR Self-Test Status Flag Register (STFLAG) |  |

| 4.2.3 | ROM Version Register (ROM_VER)              |  |

| 4.2.4 | Command Register 0 (CR0)                    |  |

| 4.2.5 | Command Register 1 (CR1)                    |  |

|       | V                                           |  |

| 4.2.6  | GO Bits Register (GO)                             |     |

|--------|---------------------------------------------------|-----|

| 4.2.7  | Transmit Request Bits Register (TX)               | 4-8 |

| 4.2.8  | Receive Accept Bits Register (RX)                 |     |

| 4.2.9  | Send Break Bits Register (BREAK)                  |     |

| 4.2.10 | Control Register 2 (CR2)                          |     |

| 4.2.11 | Master Size and Address Modifier Register (SZ_AM) |     |

|        | TABLE OF CONTENTS (Continued)                     |     |

# SECTION 4. PROGRAMMING (Concluded)

## <u>Page</u>

| 4.2.12 | Self-Test Procedure Register (ST_PROC)           |      |

|--------|--------------------------------------------------|------|

| 4.2.13 | Error Interrupt Control Register (ER_MSK)        |      |

| 4.2.14 | Error Interrupt Vector Register (ER_VEC)         | 4-13 |

| 4.2.15 | Buffer Base Register (BUFBASE)                   |      |

| 4.2.16 | Global Status Register (GST)                     | 4-14 |

| 4.2.17 | Master Granularity (MAS_GRN)                     |      |

| 4.3    | CHANNEL CONTROL BLOCKS                           | 4-17 |

| 4.3.1  | Channel Status Register (CST)                    | 4-18 |

| 4.3.2  | Channel Interrupt Mask Register (CH_MSK)         |      |

| 4.3.3  | Channel Interrupt Vector Register (CH_VEC)       |      |

| 4.3.4  | End-of-Block Code Register (EOB)                 | 4-21 |

| 4.3.5  | Flow Control XOFF Code Register (XOFF)           |      |

| 4.3.6  | Flow Control XON Code Register (XON)             |      |

| 4.3.7  | BREAK Duration Register (BRK_DUR)                |      |

| 4.3.8  | Internal Ring Size Register (SZ_RING)            | 4-23 |

| 4.3.9  | Internal Ring Low Water Mark Register (LO_RING)  |      |

| 4.3.10 | Internal Ring High Water Mark Register (HI_RING) |      |

| 4.3.11 | Channel Control Byte 1 Register (CH_CON1)        |      |

| 4.3.12 | Channel Control Byte 2 Register (CH_CON2)        |      |

| 4.3.13 | User Buffer Size Register (SZ_UBUF)              | 4-28 |

| 4.4    | GENERAL PROGRAMMING DETAILS                      |      |

| 4.4.1  | Introduction                                     |      |

| 4.4.2  | Channel Shutdown                                 |      |

| 4.4.3  | Global Setup for Board Operation                 |      |

| 4.4.4  | Channel Setup                                    |      |

| 4.4.5  | Channel Startup                                  | 4-31 |

| 4.4.6  | Channel Operation                                | 4-31 |

| 4.4.7  | Restarting After an Error Interrupt              |      |

|        |                                                  |      |

| 4.4.8 | Performance Considerations                       |  |

|-------|--------------------------------------------------|--|

| 4.4.9 | Usage Notes on VMIVME-6016 Registers             |  |

| 4.5   | GENERAL PROGRAMMING EXAMPLES                     |  |

| 4.6   | RUNNING SELF-TESTS FROM THE HOST                 |  |

| 4.7   | SAMPLE HEADER FILE                               |  |

| 4.7.1 | Sample Header File for Indivisible RMWs          |  |

| 4.7.2 | Assembler Source File for 680x0 RMW Instructions |  |

## SECTION 5. CONFIGURATION AND INSTALLATION

| 5.1 | UNPACKING PROCEDURES          |

|-----|-------------------------------|

| 5.2 | PHYSICAL INSTALLATION         |

|     | TABLE OF CONTENTS (Continued) |

## SECTION 5. CONFIGURATION AND INSTALLATION (Concluded)

#### <u>Page</u>

| 5.3   | JUMPER CONFIGURATIONS           | 5-2 |

|-------|---------------------------------|-----|

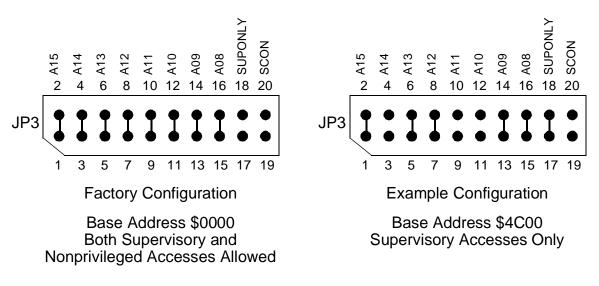

| 5.3.1 | VMEbus Address Configuration    | 5-2 |

| 5.3.2 | System Controller Configuration | 5-3 |

| 5.3.3 | Hardware Reset                  | 5-3 |

| 5.3.4 | Fixed Jumpers                   | 5-3 |

## SECTION 6. MAINTENANCE

| 6.1 | MAINTENANCE        | 6-1 |

|-----|--------------------|-----|

| 6.2 | MAINTENANCE PRINTS | 6-1 |

## LIST OF FIGURES

#### <u>FigurePage</u>

| 3.2-1    | RJ12 Socket                            |     |

|----------|----------------------------------------|-----|

| 3.5.3-1  | Ring and Linear Buffer Diagrams        |     |

| 4.3.13-1 | Buffers                                |     |

| 5.3.1-1  | Base Address and Access Mode Selection |     |

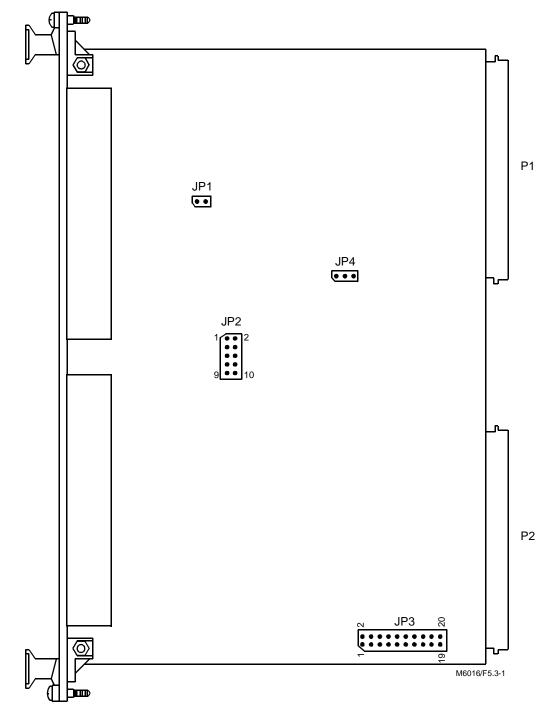

| 5.3-1    | VMIVME-6016 Jumper Field Locations     | 5-4 |

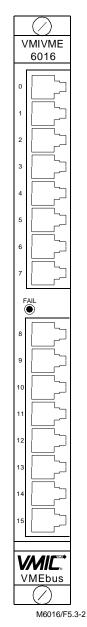

| 5.3-2    | VMIVME-6016 Front Panel                | 5-5 |

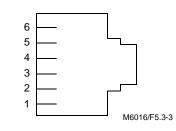

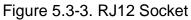

| 5.3-3    | RJ12 Socket                            | 5-5 |

|          |                                        |     |

## LIST OF TABLES

## TablePage

| 3.2-1   | RJ12 Socket Pinout                         |     |

|---------|--------------------------------------------|-----|

| 3.5-1   | Local Bus Map                              |     |

| 3.5.3-1 | RAM Map                                    |     |

| 4.1-1   | VMIVME-6016 Register Map                   | 4-1 |

| 4.2-1   | VMIVME-6016 Global Register Map            |     |

| 4.2.1-1 | Board ID Register Bit Map                  |     |

| 4.2.2-1 | POR Self-Test Status Flag Register Bit Map |     |

| 4.2.3-1 | ROM Version Register Bit Map               | 4-3 |

| 4.2.4-1 | Command Register 0 Bit Map                 |     |

| 4.2.5-1 | Command Register 1 Bit Map                 |     |

| 4.2.6-1 | GO Bits Register Bit Map                   | 4-7 |

| 4.2.7-1 | Transmit Request Bits Register Bit Map     |     |

| 4.2.8-1 | Receive Accept Bits Register Bit Map       |     |

|         |                                            |     |

## TABLE OF CONTENTS (Concluded)

## LIST OF TABLES (Concluded)

## <u>TablePage</u>

| 4.2.9-1  | Send Break Bits Register Bit Map                  |  |

|----------|---------------------------------------------------|--|

| 4.2.10-1 | Control Register 2 Bit Map                        |  |

| 4.2.11-1 | Master Size and Address Modifier Register Bit Map |  |

| 4.2.12-1 | Self-Test Procedure Register Bit Map              |  |

| 4.2.13-1 | Error Interrupt Control Register Bit Map          |  |

| 4.2.14-1 | Error Interrupt Vector Register Bit Map           |  |

| 4.2.16-1 | Global Status Register Bit Map                    |  |

| 4.2.17-1 | Master Granularity Register Bit Map               |  |

| 4.3-1    | VMIVME-6016 Channel Control Block Map             |  |

| 4.3.1-1  | Channel Status Register Bit Map                   |  |

| 4.3.2-1  | Channel Interrupt Mask Register Bit Map           |  |

| 4.3.3-1  | Channel Interrupt Vector Register Bit Map         |  |

| 4.3.4-1  | End-of-Block Code Register Bit Map                |  |

| 4.3.5-1  | Flow Control XOFF Code Register                   |  |

| 4.3.6-1  | Flow Control XON Code Register Bit Map            |  |

| 4.3.7-1  | BREAK Duration Register Bit Map                   |  |

| 4.3.8-1  | Internal Ring Size Register Bit Map              |     |

|----------|--------------------------------------------------|-----|

| 4.3.9-1  | Internal Ring Low Water Mark Register Bit Map    |     |

| 4.3.10-1 | Internal Ring High Water Mark Register Bit Map . |     |

| 4.3.11-1 | Channel Control Byte 1 Register Bit Map          |     |

| 4.3.12-1 | Channel Control Byte 2 Register Bit Map          |     |

| 4.3.13-1 | User Buffer Size Register Bit Map                |     |

| 4.4.1-1  | VMIVME-6016 Register and Field Symbols           |     |

| 4.6-1    | CST[0] Register Self-Test Failure Codes          |     |

| 4.6-2    | Test Bits in STPROC Register                     |     |

| 5.3-1    | RJ12 Socket Pinout                               | 5-5 |

## **APPENDIX**

| A | Assembly Drawing, | Parts List, | and Schematic |

|---|-------------------|-------------|---------------|

|---|-------------------|-------------|---------------|

## **SECTION 1**

## INTRODUCTION

#### 1.1 INTRODUCTION

The VMIVME-6016 is a single-slot serial port controller with 16 or 32 channels, on-board ring buffers for each channel in both directions, and an on-board 25 MHz no-wait-state 68020 processor. The processor handles all character I/O and buffering, with Channel Control Blocks (CCBs) in on-board memory. User buffers, either linear or ring, reside either on-board or in VMEbus global memory. The VMEbus interface is controlled by a VIC068 or optional VIC64 VMEbus Interface Controller.

#### 1.2 FEATURES

- a. 8 or 16 channels available in one VMEbus slot

- b. Line parameters independently controlled for each channel by control block in memory:

- baud rate

- internal ring buffer size

- user buffer size and address

- user buffer type (linear or ring)

- flow control: XON/XOFF, Any/XOFF, User characters, RTS/CTS, None

- interrupt on EOB or user-defined character

- interrupt on receive time-out

- interrupt on flow control

- interrupt on transmit complete

- BREAK send/receive and duration

- interrupt vector and level

- c. RJ12 front panel connectors

- d. Signal levels RS-232 compatible

- e. Channel signals: TXD, RXD, RTS, CTS, DCD, GND

- f. Short I/O-accessed control blocks

- g. Standard/extended/DMA-accessed user buffers

- h. Programmable VMEbus address modifiers

- i. Size-programmable on-board ring buffers

- j. 128 Kbytes, 256 Kbytes, 512 Kbytes, or 1024 Kbytes total user buffer space

- k. 68020 processor, 25 MHz or 32 MHz, no-wait-states

- I. Baud rates: 50 through 38,400 bps, each channel independent

- m. Programmable interrupt vector and level

- n. VMEbus compatible

- o. MA32:MBLT32 as Master, optional MBLT64 with VIC64

- p. SADO32:SD32 as Slave, optional MBLT with VIC64

- q. Front panel status indicator

- r. Programmable slave address for extended/standard buffer locations

- s. Jumper-selectable slave address for short I/O

- t. Bus release: ROR, RWD, FAIR, RCLR

- u. Jumper-enabled system controller functions

#### 1.3 REFERENCE MATERIAL LIST

Refer to "The VMEbus Specification" for a detailed explanation of the priority interrupt bus. "The VMEbus Specification" is available from the following source:

#### VITA VFEA International Trade Association 10229 N. Scottsdale Road Scottsdale, AZ 85253 (602) 951-8866

The following application and configuration guides are available from VMIC to assist the user in the selection, specification, and implementation of systems based on VMIC's products:

#### <u>TITLE</u>

## DOCUMENT NO.

| Digital Input Board Application Guide                        | 825-000000-000 |

|--------------------------------------------------------------|----------------|

| Change-of-State Application Guide                            | 825-000000-002 |

| Digital I/O (with Built-in-Test) Production Line Description | 825-000000-003 |

| Connector and I/O Cable Application Guide                    | 825-000000-006 |

## **SECTION 2**

## PHYSICAL DESCRIPTION AND SPECIFICATIONS

REFER TO 800-006016-000 SPECIFICATION

## **SECTION 3**

## THEORY OF OPERATION

#### 3.1 OPERATIONAL OVERVIEW

The VMIVME-6016 is a single-slot serial port controller with 16 or 32 channels, on-board ring buffers for each channel in both directions, and an on-board 25 MHz no-wait-state 68020 processor. The processor handles all character I/O and buffering, with Channel Control Blocks (CCBs) in on-board memory. User buffers, either linear or ring, reside either on-board or in VMEbus global memory. The VMEbus interface is controlled by a VIC068 or VIC64 VMEbus Interface Controller.

The VMIVME-6016 is an SADO32:SD32 VMEbus Slave for setup purposes. The VMEbus processor must set a number of items within the VMIVME-6016, such as interrupt vectors and masks. Most importantly, the host processor must set up a CCB for each of the channels. These blocks specify line parameters, flow control method, interrupts, on-board transmit and receive ring buffer size, and off-board user buffer size and method. The CCB allows each of the 16 channels to be independently programmable. When the host processor sets the GO bit for a channel, the VMIVME-6016 autonomously operates according to parameters in the corresponding CCB.

The front panel has an RJ12 6-pin telecom jack for each channel. Each channel supports signal ground and five signals:

- Receive Data

- Transmit Data

- Request to Send

- Clear to Send

- Data Carrier Detect

#### 3.2 RS-232 CONNECTIONS

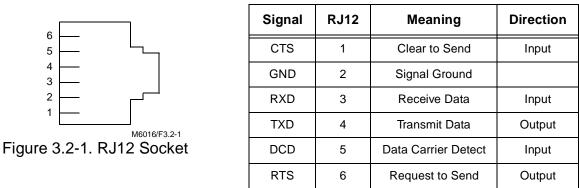

Each of the 16 channels is a 6-wire subset of the usual RS-232 signals. The RJ12 connectors are shown on schematic sheet 14. As viewed from the front panel, the RJ12 appears as in Figure 3.2-1. Each channel has the pinout shown in Table 3.2-1.

#### Table 3.2-1. RJ12 Socket Pinout

M6016/T3.2-1

The VMIVME-6016 does not need ±12 V from the VMEbus backplane. The RS-232 levels are converted to and from TTL by the MAX244 chips shown on sheets 11 and 13 of the schematics. Using internal charge pumps, these chips generate their own ±12 V from the VMEbus +5 V. The charge pumps require the attached 1  $\mu$ F capacitors. There are no jumpers or hardware configuration involved with the RS-232 interfaces.

#### 3.3 CONTROL BLOCKS AND REGISTERS

The VMIVME-6016 emulates the register space with the top 256 bytes of on-board RAM accessed from the VMEbus by SADO16:SD32 (short I/O). Most of this space is taken up by 16 identically formatted control blocks, one for each of the 16 RS-232 channels. There is also a global register set for overall control and status.

#### 3.4 VMEbus INTERFACE

The VMEbus interface is shown on schematic sheets 2, 5, 6, 7, and the top of 8. It uses a VIC as the core of the design. The CY7C964 slices save complexity of layout and logic design and support full master and slave VMEbus functionality including block-mode slave transfers. These transfers appear to the local bus as a chain of single cycles, so the CPU will not get locked out. See Section 3.5.1.

As a VMEbus slave, the VMIVME-6016 responds to A16 accesses to implement control and status registers with some of the on-board memory and to A24 and A32 accesses to implement on-board user buffers for each channel. The VMEbus slave specification is SADO32:SD32 (A32:A24:A16:ADO:D32:D16:D8(EO)). Supervisory only or both supervisory and nonprivileged accesses are allowed. Boards with the VIC64 option are additionally capable of MBLT64 VME64 accesses.

As a VMEbus master, the VMIVME-6016 can request the bus on any of the three BR levels, with AM code, BR level, and data width under control of programmable registers. The master specification is MA32:MBLT32 (A32:A24:A16:D32:D16:D8(EO):BLT)). The VIC64 option adds MBLT64.

As system controller (if installed in VMEbus slot 1), the VMIVME-6016 provides a full-function three-level arbiter, an IACK daisy-chain driver, a programmable BERR timer, a SYSCLK driver, and a SYSRESET\* driver.

See Sections 3.5.3, 3.5.5, 3.6, and Sections 4 and 5 for details.

#### 3.5 LOCAL BUS

A 32-bit data bus supports the ROM, RAM, 68020 CPU, UARTs, control and status registers for the VMEbus interface, and a buffer for reading the short I/O configuration jumpers. See Table 3.5-1 for the overall map for the local bus.

| Offset            | Description                     |

|-------------------|---------------------------------|

| \$000000 - 03FFFF | RAM                             |

| \$040000 - 1FFFFF | Expansion RAM                   |

| \$200000 - 27FFFF | VIC VMEbus Interface Controller |

| \$280000 - 2FFFFF | LED control, jumpers, etc.      |

| \$300000 - 37FFFF | UARTs                           |

| \$380000 - 3FFFFF | ROM                             |

|                   | M6016/T3.5-1                    |

Table 3.5-1. Local Bus Map

The on-board CPU can make VMEbus master accesses by setting a direction control bit (TOLOCAL in the \$280000 space) and then entering user mode, as opposed to supervisor mode. If the direction is TOLOCAL = 1, for example, a read accesses VMEbus space no matter what the address, and a write accesses local RAM. The TOLOCAL register is in the glue logic (see Section 3.5.6). The VMEbus cycles can be single cycle, bursts, or block transfers, depending on the programmable registers in the VIC chip.

#### 3.5.1 CPU

The CPU (see schematic sheet 3) is a 25 or 32 MHz 68020. The CPU controls all other devices on the local bus and is responsible for transferring all UART data and status. It runs extensive tests on most of the hardware at power up. Additional diagnostic routines support production test. At the highest UART bit rate (38,400 bits/second), there are some throughput restrictions. The CPU has to process a data byte from a channel about every 15 microseconds if all are active at once in one direction. Bidirectional 38,400 bits/second on all channels simultaneously is not possible.

#### 3.5.2 ROM

The VMIVME-6016 firmware resides in a 64 Kbyte ROM (27C512), on the lower half of schematic sheet 8. On power up or hard reset (by momentarily shorting J1), the firmware causes the CPU to run a test of the RAM. After this test, the whole content of the ROM is copied to the private section of RAM, the upper half. At least 64 Kbytes of private RAM are left for stacks and so forth. For the first eight byte-wide local bus cycles, the ROM is mapped to local bus zero (0). Afterwards, it is mapped at local \$380000 and up allowing the CPU to get its initial program counter and stack address correctly. Once the CPU completes the power-on tests, it sets up defaults in the register space and begins waiting for the host to set up control blocks.

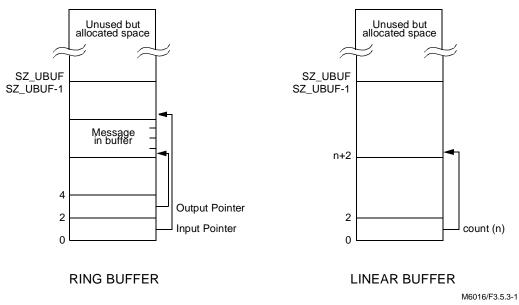

#### 3.5.3 RAM

A 256 Kbyte static RAM, U16 on sheet 9, provides all of the space needed for the A16 space registers, local work area and code, and on-board user buffers. It is a 35 ns static RAM module, organized 64 Kbytes x 32 bits. See Table 3.5.3-1 for a map of the RAM.

| Offset            | Description                    |

|-------------------|--------------------------------|

| \$000000 - 01FFFF | On-board user buffers, if used |

| \$020000 - 03FEFF | CPU private, and ring buffers  |

| \$03FF00 - 03FFFF | A16-space registers            |

|                   | M6016/T3.5.3-1                 |

Table 3.5.3-1. RAM Map

The RAM can be expanded to 512 Kbytes, 1 MB, or 2 MB, but it would only provide for larger on-board user and internal buffers. (See Section 4.2.15 for details.)

When the VMIVME-6016 is used in slave mode (on-board user buffers), the user buffers (linear or ring) appear in ascending order by channel, starting at the VMEbus address given in one of the global registers. This space is mapped into the lower half of the on-board RAM. The CPU's private memory (stacks, interrupt vectors, primary ring buffers, global variables, and code) begins halfway through the on-board RAM and ends just below the area taken by the A16 space registers.

#### 3.5.4 UARTs

Two Phillips 2698B octal UART chips provide a total of 16 channels (shown on schematic sheets 10 and 12). Receive Ready signals from each channel can interrupt the on-board CPU with sixteen unique vectors. There are eight more vectors for pairs of channels for lower-priority events, such as Transmit Ready, Break, Overrun, and Parity Error. The TTL level serial signals get converted to and from RS-232 levels by five Maxim MAX244 self-powered transceiver chips.

#### 3.5.5 Jumpers

The CPU can read the ten jumpers at JP3 on sheet 8 of the schematic by asserting the JMPRDN signal (see Section 3.5.6). There is no other connection to the jumpers except through the buffers to the Local Bus. The CPU uses the upper eight jumper locations to program the CY7C964 connected to VMEbus A[15..8] (sheet 7) to map VMEbus A16 slave space. The ninth jumper location is used by the CPU to

program the VIC chip slave decode control registers for either supervisor only or for both supervisor and nonprivileged. It is not possible to configure the VMIVME-6016 for nonprivileged only slave space. This jumper controls only the AM decode for A16 space; the A24 and A32 buffer space is programmable, but also for the same two choices (no nonprivileged only). The CPU uses the tenth jumper location to control the System Controller features of the VIC chip.

#### 3.5.6 Glue Logic

The glue logic that provides the local bus memory mapping and the local bus read/write/select signals is in an 80-macrocell PLD-like FPGA at U9 on sheet 4. This is an Intel FX780, chosen because of its uniform timing and global routability.

#### 3.6 VMEbus TIMER

The VMIVME-6016 has a hardware timer that counts 3.6864 MHz clock cycles while either DS0\* or DS1\* is asserted. Sheet 4, lower left, shows the timer. If about 50 microseconds elapse while the timer is counting, it asserts BERR\* (if BTOEN is low). The BERR\* negates about 300 ns after the DSx negate. Note that the DSx signals are isolated from the PLD by 220 ohm resistors which help reduce the DSx tracelengths and loading. See Section 4.2.5 for information on disabling the hardware timer.

The VIC chip supplies a programmable VMEbus time-out period (BERR\* generator) ONLY if the board is configured for, and is in, VMEbus slot 1.

## **SECTION 4**

## PROGRAMMING

#### 4.1 OVERVIEW

The VMIVME-6016 has 256 bytes of registers which appear in VMEbus A16 (short I/O) memory space. The Global Registers use the first 32 bytes of this space. The Channel Control Blocks immediately follow the Global Registers in short I/O space, channel 0 first (see Table 4.1-1). These registers should generally be accessed according to the size indicated, but the registers tolerate byte, word, longword, and unaligned access.

#### NOTE:

FOR A SHORT TIME AFTER POWER UP, THE VMIVME-6016 WILL NOT DECODE ACCESSES FROM THE VMEbus. THIS PERIOD IS ALWAYS LESS THAN TWENTY (20) MILLISECONDS. AFTER THIS TIME, ON-BOARD SELF-TESTS BEGIN TO RUN, DURING WHICH TIME THE VMIVME-6016 DECODES VMEbus A16 (SHORT I/O) ACCESSES AND SHOWS \$FF IN THE POR SELF-TEST STATUS FLAG REGISTER. WHILE THE POR SELF-TEST STATUS FLAG REGISTER IS NONZERO, NONE OF THE REGISTERS BEYOND OFFSET \$03 ARE VALID, AND VMEbus ACCESSES TO THE BOARD SHOULD BE KEPT TO A MINIMUM OR THE SELF-TEST WILL SLOW DOWN. THE SELF-TEST PERIOD IS LESS THAN TWENTY SECONDS (ABOUT FIVE SECONDS FOR THE NORMAL MEMORY CONFIGURATION, WHICH PROVIDES 128 KBYTES OF USER BUFFER MEMORY).

| Offset    | Description              |

|-----------|--------------------------|

| \$00 - 1F | Global Registers         |

| \$20 - 2D | Channel Control Block 0  |

| \$2E - 3B | Channel Control Block 1  |

| \$3C - 49 | Channel Control Block 2  |

| \$4A - 57 | Channel Control Block 3  |

| \$58 - 65 | Channel Control Block 4  |

| \$66 - 73 | Channel Control Block 5  |

| \$74 - 81 | Channel Control Block 6  |

| \$82 - 8F | Channel Control Block 7  |

| \$90 - 9D | Channel Control Block 8  |

| \$9E - AB | Channel Control Block 9  |

| \$AC - B9 | Channel Control Block 10 |

| \$BA - C7 | Channel Control Block 11 |

| \$C8 - D5 | Channel Control Block 12 |

| \$D6 - E3 | Channel Control Block 13 |

| \$E4 - F1 | Channel Control Block 14 |

| \$F2 - FF | Channel Control Block 15 |

Table 4.1-1. VMIVME-6016 Register Map

M6016

#### 4.2 GLOBAL REGISTER MAP

The Global Registers control those features of the VMIVME-6016, and reflect those status conditions, that are independent of specific channels. This includes, for example, the slave mode base address and address space of the VMIVME-6016. Table 4.2.1 shows their offsets from the Board ID Register, the short I/O address of which is determined by a jumper field (see Section 5.3.1).

#### NOTE:

ANY BIT OR FIELD SHOWN AS ZERO (0) AND/OR RESERVED MUST BE SET TO ZERO (0).

| Offset | Name    | Meaning                          | Read/Write |

|--------|---------|----------------------------------|------------|

| \$00   | BRD_ID  | Board ID                         | Read Only  |

| \$01   | STFLAG  | Self-Test flag in ID Register    | Read Only  |

| \$02   | ROM_VER | ROM Version Code                 | Read Only  |

| \$04   | CR0     | Command Register 0               | Read/Write |

| \$05   | CR1     | Command Register 1               | Read/Write |

| \$06   | GO      | "GO" bits, ch[150] = GO[150]     | Read/Write |

| \$08   | ТХ      | "TX" bits, ch[150] = TX[150]     | Read/Write |

| \$0A   | RX      | "RX" bits, ch[150] = RX[150]     | Read/Write |

| \$0C   | BREAK   | "BREAK", ch[150] = BREAK[150]    | Read/Write |

| \$0E   | CR2     | Command Register 2               | Read/Write |

| \$0F   |         | Reserved                         |            |

| \$10   | SZ_AM   | Master's Size and AM             | Read/Write |

| \$11   | ST_PROC | Self-Test Procedure Register     | Read/Write |

| \$12   | ER_MSK  | Error Interrupt Control          | Read/Write |

| \$13   | ER_VEC  | Error Interrupt Vector           | Read/Write |

| \$14   | BUFBASE | Base of Buffers (M) or Board (S) | Read/Write |

| \$18   | GST     | Global Status Register           | Read/Write |

| \$1A   | MAS_GRN | Master Granularity               | Read/Write |

Table 4.2-1. VMIVME-6016 Global Register Map

M6016/T4.2-1

#### 4.2.1 Board ID Register (BRD\_ID)

The Board ID register is a read-only byte register. It always contains the value \$3A, the VMIVME-6016 board identification code.

| Global Offset \$00 BRD_ID (Read Only)                                                                           |               |   |   |   |   |   |   |  |  |

|-----------------------------------------------------------------------------------------------------------------|---------------|---|---|---|---|---|---|--|--|

| Bit 07         Bit 06         Bit 05         Bit 04         Bit 03         Bit 02         Bit 01         Bit 00 |               |   |   |   |   |   |   |  |  |

| 0                                                                                                               | 0             | 1 | 1 | 1 | 0 | 1 | 0 |  |  |

|                                                                                                                 | M6016/T4.2.1- |   |   |   |   |   |   |  |  |

Table 4.2.1-1. Board ID Register Bit Map

## 4.2.2 POR Self-Test Status Flag Register (STFLAG)

The Power-On-Reset (POR) Self-Test Status Flag register is a read-only byte register. Upon power up or VMEbus system reset, the VMIVME-6016 processor runs a self-diagnostic and reports the results to the GST register. A value of \$FF indicates the board is still busy with its self-test, while a value of \$00 indicates the test is complete. If the self-test fails, the Self-Test Fail bit in the GST is set. While the value is \$FF, the board should be considered nonfunctional; the only register containing valid data besides this one is the Board ID register. Once the STFLAG register is clear, the board functions normally and all other registers are valid.

| Global Offset \$01 STFLAG (Read Only)                                                                           |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Bit 07         Bit 06         Bit 05         Bit 04         Bit 03         Bit 02         Bit 01         Bit 00 |  |  |  |  |  |  |  |  |

| SELF-TEST STATUS                                                                                                |  |  |  |  |  |  |  |  |

M6016/T4.2.2-1

## 4.2.3 ROM Version Register (ROM\_VER)

The ROM Version register is a read-only word register. The value in the lower byte of this register represents the revision number of the on-board firmware as two 4-bit BCD digits. The upper byte represents the hardware options installed.

| Global Offset \$02 ROM_VER (Read Only)                                                                          |   |             |          |              |          |         |  |  |

|-----------------------------------------------------------------------------------------------------------------|---|-------------|----------|--------------|----------|---------|--|--|

| Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 09         Bit 08 |   |             |          |              |          |         |  |  |

| INCONSIST_OPT                                                                                                   | 0 | OLD_VIC_OPT | MBLT_OPT | SLOW_CPU_OPT | CHAN_OPT | MEM_OPT |  |  |

| Bit 07         Bit 06         Bit 05         Bit 04         Bit 03         Bit 02         Bit 01         Bit 00 |   |             |          |              |          |         |  |  |

| FIRMWARE REVISION                                                                                               |   |             |          |              |          |         |  |  |

Table 4.2.3-1. ROM Version Register Bit Map

M6016/T4.2.3-1

- **Bit 15:** Inconsistent Options (INCONSIST\_OPT) When set to one (1), this bit indicates that the ROM firmware is inconsistent with the hardware options.

- **<u>Bit 14:</u>** Reserved This bit is always zero (0).

- **Bit 13:** Old VIC Option (OLD\_VIC\_OPT) When set to one (1), this bit indicates that the VMIC silicon ID is too old.

- **Bit 12:** MBLT Option (MBLT\_OPT) When set to one (1), this bit indicates that the VIC chip is VIC64 and MBLT is possible. A zero (0) indicates that the VIC chip is VIC68 and MBLT is **not** possible.

- **Bit 11:** Slow CPU Option (SLOW\_CPU\_OPT) When set to one (1), this bit indicates that the CPU is running at 25 MHz. A zero (0) indicates a 32 MHz CPU.

- **Bit 10:** Channel Option (CHAN\_OPT) When set to one (1), this bit indicates that only 8 channels are available for use. A zero (0) indicates that 16 channels are available.

- **<u>Bits 09-08</u>**: Memory Option (MEM\_OPT) These bits indicate the memory available on the VMIVME-6016 as follows:

| Bit 09 | Bit 08 | User Buffer<br>Area |

|--------|--------|---------------------|

| 0      | 0      | 128 Kbytes          |

| 0      | 1      | 256 Kbytes          |

| 1      | 0      | 512 Kbytes          |

| 1      | 1      | 1 Mbyte             |

## 4.2.4 Command Register 0 (CR0)

This register controls the major features of the VMIVME-6016. This register should be accessed according to Section 4.4.9.

| Global Offset \$04 CR0 (Read/Write)                                                                             |        |        |         |       |        |         |      |  |  |

|-----------------------------------------------------------------------------------------------------------------|--------|--------|---------|-------|--------|---------|------|--|--|

| Bit 07         Bit 06         Bit 05         Bit 04         Bit 03         Bit 02         Bit 01         Bit 00 |        |        |         |       |        |         |      |  |  |

| MASTER                                                                                                          | SLV_OK | SLV_32 | SUPONLY | TXBRK | SLFTST | RST_BRD | LEDN |  |  |

Table 4.2.4-1. Command Register 0 Bit Map

M6016/T4.2.4-1

- **Bit 07:** Master Mode (MASTER) When set to one (1), this bit causes the VMIVME-6016 to run in master mode, in which the user buffers are off-board. In master mode, SZ\_AM and BUFBASE point to a block of VMEbus memory that holds all the user buffers. When set to zero (0), the MASTER bit causes the VMIVME-6016 to run in slave mode, in which the user buffers are on-board. In this case, BUFBASE is the programmable VMEbus address of the on-board user buffers. In both cases, the user buffers are an array of possibly different-sized buffers. Each is allocated a fixed amount of memory whether or not it is all used: 1/64 of the total on-board RAM in the slave case and up to 32 Kbytes in the master case. They start with channel 0 input followed by channel 0 output, and finally ending with channel 15 output.

- **Bit 06:** Slave Decode OK (SLV\_OK) When set to one (1), this bit allows VMEbus access to the user buffer memory on the VMIVME-6016. This bit should ordinarily be set to one (1) if the VMIVME-6016 is in slave mode (on-board user buffers), and be set to zero (0) otherwise. When this bit transitions from zero (0) to one (1), the VMIVME-6016 uses the contents of the BUFBASE to set the base address of the VMEbus space in which the user buffer memory will appear. After the slave address is set, BUFBASE can be used for other purposes.

- **Bit 05:** Slave is A32 (SLV\_32) When set to one (1), this bit allows extended (A32) VMEbus access to the user buffer memory on the VMIVME-6016. When this bit is set to zero (0), the VMIVME-6016 responds to standard (A24) accesses, and the most significant eight bits of BUFBASE are ignored.

- **Bit 04:** Slave decodes only Supervisor Address Modifiers (SUPONLY) When set to one (1), this bit allows only supervisor accesses to the user buffer memory on the VMIVME-6016. When set to zero (0), it allows both supervisory and nonprivileged accesses. This bit has no effect on short I/O (A16) accesses to the VMIVME-6016. (There is a jumper for that function; see Section 5.3.1.)

- **Bit 03:** Transmit BREAK Signals (TXBRK) When this bit is set from zero (0) to one (1), a BREAK signal is sent on each active channel for which a bit is set in the BREAK register. Bits are automatically cleared in BREAK as the signals are sent, and when all the requested BREAKs have been sent, the TXBRK bit is automatically reset to zero (0).

- **Bit 02:** Run Self-Test (SLFTST) When this bit is set from zero (0) to one (1), the self-tests requested in the ST\_PROC register are run in order of most significant ST\_PROC bit to least significant ST\_PROC bit. When the tests have run, or a failure occurs, the testing stops and the SLFTST bit is automatically reset to zero (0). The STBUSY bit of the GST should be one (1) until the self-test is complete. The ANYERR and STFAIL bits of the GST should be zero (0) if the self-test passed.

- **Bit 01:** Reset Board (RST\_BRD) When this bit is set to a one (1), the VMIVME-6016 goes through nearly all the POR test sequence (excepting only the RAM shake) and presents itself as if power had just come on. Note that the board briefly "disappears" from short I/O space as it executes the POR tests. See Sections 4.1 and 4.2.2.

- **<u>Bit 00:</u>** LED Control (LEDN) When this bit is set to one (1), the LED on the front panel is off. Clear this bit to turn the LED on. The LED is off after the power-up (or reset) self-tests complete successfully. (The LED flashes on and off during these self-tests.)

#### 4.2.5 Command Register 1 (CR1)

This register controls the BERR\* timer and the arbitration mode. Bits not mentioned below must remain set to zero (0).

| Global Offset \$05 CR1 (Read/Write)                                                                             |   |   |   |        |         |  |                |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|---|---|---|--------|---------|--|----------------|--|--|--|

| Bit 07         Bit 06         Bit 05         Bit 04         Bit 03         Bit 02         Bit 01         Bit 00 |   |   |   |        |         |  |                |  |  |  |

| 0                                                                                                               | 0 | 0 | 0 | ARBMOD | BERR_TO |  |                |  |  |  |

|                                                                                                                 |   | • |   |        |         |  | M6016/T4 2 5-1 |  |  |  |

Table 4.2.5-1. Command Register 1 Bit Map

**Bit 03:** Arbiter Mode (ARBMOD) – This bit has no effect unless the VMIVME-6016 is in the VMEbus slot 1 as the system controller and the SCON jumper is installed (see Section 5.3.2 for details). If the VMIVME-6016 is the system controller, a zero in this bit causes the VMIVME-6016 VMEbus arbiter to use a round-robin arbitration scheme, while a one (1) causes it to use a prioritized arbitration scheme.

**Bits 02-00:** SCON Mode VMEbus Timeout (BERR\_TO) – When the VMIVME-6016 is system controller, this field sets the maximum allowed time before a BUS ERROR signal is issued in the absence of a DTACK for any VMEbus access. The maximum time codes mean:

| Bit 2 | Bit 1 | Bit 0 | Maximum Time     |  |  |

|-------|-------|-------|------------------|--|--|

| 0     | 0     | 0     | 4 microseconds   |  |  |

| 0     | 0     | 1     | 16 microseconds  |  |  |

| 0     | 1     | 0     | 32 microseconds  |  |  |

| 0     | 1     | 1     | 64 microseconds  |  |  |

| 1     | 0     | 0     | 128 microseconds |  |  |

| 1     | 0     | 1     | 256 microseconds |  |  |

| 1     | 1     | 0     | 512 microseconds |  |  |

| 1     | 1     | 1     | Infinite         |  |  |

When the VMIVME-6016 is **not** the system controller, any value in BERR\_TO other than binary 111 selects a nominal 50 microsecond timeout, and 111 disables the timer. In this case, the timer applies only to VMIVME-6016 accesses.

#### 4.2.6 GO Bits Register (GO)

The GO register has a GO bit for each of the 16 channels. After the Channel Control Blocks and the Global Registers have been set up, setting the GO bit for a given channel to one (1) lets the VMIVME-6016 activate that channel. Activity for a channel stops if the corresponding GO bit is set to zero (0). Bit 15 (the MSB) corresponds to channel 15, bit 14 is for channel 14, and similar mapping goes through bit 0 (the LSB), which is for channel 0. Setting GO for a channel automatically clears TX and RX for that channel. This register should be modified using an indivisible RMW instruction. See Section 4.4.9 for details.

|               | Global Offset \$06 GO (Read/Write) |               |               |               |               |               |               |  |  |  |  |

|---------------|------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|--|--|--|--|

| Bit 15        | Bit 14                             | Bit 13        | Bit 12        | Bit 11        | Bit 10        | Bit 09        | Bit 08        |  |  |  |  |

| Channel<br>15 | Channel<br>14                      | Channel<br>13 | Channel<br>12 | Channel<br>11 | Channel<br>10 | Channel<br>09 | Channel<br>08 |  |  |  |  |

| Bit 07        | Bit 06                             | Bit 05        | Bit 04        | Bit 03        | Bit 02        | Bit 01        | Bit 00        |  |  |  |  |

| Channel<br>07 | Channel<br>06                      | Channel<br>05 | Channel<br>04 | Channel<br>03 | Channel<br>02 | Channel<br>01 | Channel<br>00 |  |  |  |  |

Table 4.2.6-1. GO Bits Register Bit Map

M6016/T4.2.6-1

## 4.2.7 Transmit Request Bits Register (TX)

The TX register has a transmit request bit for each of the 16 channels. Provided the GO bit for a channel is set, setting the corresponding TX bit will request the VMIVME-6016 to accept data from the transmit user buffer and transfer it through the internal ring buffer to the transmitter. Bit 15 (the MSB) corresponds to channel 15, bit 14 is for channel 14, and similar mapping goes through bit 0 (the LSB), which is for channel 0. These bits can be understood as notifying the VMIVME-6016 that the user buffer contains new data to be transmitted. This register should be modified using an indivisible RMW operation. See Section 4.4.9 for details.

|               | Global Offset \$08 TX (Read/Write) |               |               |               |               |               |               |  |  |  |  |

|---------------|------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|--|--|--|--|

| Bit 15        | Bit 14                             | Bit 13        | Bit 12        | Bit 11        | Bit 10        | Bit 09        | Bit 08        |  |  |  |  |

| Channel<br>15 | Channel<br>14                      | Channel<br>13 | Channel<br>12 | Channel<br>11 | Channel<br>10 | Channel<br>09 | Channel<br>08 |  |  |  |  |

| Bit 07        | Bit 06                             | Bit 05        | Bit 04        | Bit 03        | Bit 02        | Bit 01        | Bit 00        |  |  |  |  |

| Channel<br>07 | Channel<br>06                      | Channel<br>05 | Channel<br>04 | Channel<br>03 | Channel<br>02 | Channel<br>01 | Channel<br>00 |  |  |  |  |

| Table 4.2.7-1. Transmit Request Bit | ts Register Bit Map |

|-------------------------------------|---------------------|

|-------------------------------------|---------------------|

M6016/T4.2.7-1

## 4.2.8 Receive Accept Bits Register (RX)

The RX register has a receive-accept bit for each of the 16 channels. Provided the GO bit for a channel is set, setting the corresponding RX bit notifies the VMIVME-6016 that the data in the user receive buffer has been accepted and that new data can be put into the user receive buffer from the internal ring buffer. Bit 15 (the MSB) corresponds to channel 15, bit 14 is for channel 14, and similar mapping goes through bit 0 (the LSB), which is for channel 0. Note that because there is no internal ring buffer in the on-board ring buffer case (UB\_RING = 1, see Section 4.3.11), the RX bits for channels configured this way have no function and are ignored. This register should be modified using an indivisible RMW operation. See Section 4.4.9 for details.

| Table 4.2.8-1. | Receive Accep | ot Bits Regist | er Bit Map |

|----------------|---------------|----------------|------------|

|                |               |                |            |

|               | Global Offset \$0A RX (Read/Write) |               |               |               |               |               |               |  |  |  |  |

|---------------|------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|--|--|--|--|

| Bit 15        | Bit 14                             | Bit 13        | Bit 12        | Bit 11        | Bit 10        | Bit 09        | Bit 08        |  |  |  |  |

| Channel<br>15 | Channel<br>14                      | Channel<br>13 | Channel<br>12 | Channel<br>11 | Channel<br>10 | Channel<br>09 | Channel<br>08 |  |  |  |  |

| Bit 07        | Bit 06                             | Bit 05        | Bit 04        | Bit 03        | Bit 02        | Bit 01        | Bit 00        |  |  |  |  |

| Channel<br>07 | Channel<br>06                      | Channel<br>05 | Channel<br>04 | Channel<br>03 | Channel<br>02 | Channel<br>01 | Channel<br>00 |  |  |  |  |

M6016/T4.2.8-1

#### 4.2.9 Send Break Bits Register (BREAK)

The BREAK register has a bit for each of the 16 channels. After the Channel Control Blocks and the Global Registers have been set up, setting the BREAK bit for a given channel to one (1), and then setting the TXBRK bit, makes the VMIVME-6016 send a BREAK signal on that channel. The bit automatically resets to zero (0) when the BREAK signal starts. The BREAK is an RS-232 spacing level lasting for a number of milliseconds set by the BRK\_DUR register in the Channel Control Block.

|               | Global Offset \$0C BREAK (Read/Write) |               |               |               |               |               |               |  |  |  |  |

|---------------|---------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|--|--|--|--|

| Bit 15        | Bit 14                                | Bit 13        | Bit 12        | Bit 11        | Bit 10        | Bit 09        | Bit 08        |  |  |  |  |

| Channel<br>15 | Channel<br>14                         | Channel<br>13 | Channel<br>12 | Channel<br>11 | Channel<br>10 | Channel<br>09 | Channel<br>08 |  |  |  |  |

| Bit 07        | Bit 06                                | Bit 05        | Bit 04        | Bit 03        | Bit 02        | Bit 01        | Bit 00        |  |  |  |  |

| Channel<br>07 | Channel<br>06                         | Channel<br>05 | Channel<br>04 | Channel<br>03 | Channel<br>02 | Channel<br>01 | Channel<br>00 |  |  |  |  |

| Table 4.2.9-1. | Send Break | <b>Bits Register</b> | Bit Map |

|----------------|------------|----------------------|---------|

|                |            |                      |         |

M6016/T4.2.9-1

#### 4.2.10 Control Register 2 (CR2)

This register controls the VMEbus request level, release mode, and fairness timeout for master accesses to the VMEbus.

|                                                                                                                 | Global Offset \$0E CR2 (Read/Write) |      |     |         |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|-------------------------------------|------|-----|---------|--|--|--|--|--|--|--|

| Bit 07         Bit 06         Bit 05         Bit 04         Bit 03         Bit 02         Bit 01         Bit 00 |                                     |      |     |         |  |  |  |  |  |  |  |

| BRL                                                                                                             | EVEL                                | RELI | MOD | FAIR_TO |  |  |  |  |  |  |  |

Table 4.2.10-1. Control Register 2 Bit Map

M6016/T4.2.10-1

**Bits 07-06:** Bus Request Level (BRLEVEL) – This field controls the VMEbus bus request level for the VMEbus DMA accesses during transfers. The default value is binary 11, indicating a bus request level of 3, the highest value available.

**Bits 05-04:** VMEbus Release Mode (RELMOD) – This field determines the VMEbus Release Mode when the VMIVME-6016 is the bus Master. The Release Mode codes are:

| Bit 05 | Bit 04 | Code Description         |                      |  |

|--------|--------|--------------------------|----------------------|--|

| 0      | 0      | RELROR                   | Release on Request   |  |

| 0      | 1      | RELRWD Release when Done |                      |  |

| 1      | 0      | RELROC                   | Release on BCLR*     |  |

| 1      | 1      | RELBCAP                  | Bus capture and hold |  |

The default value for this field is binary 00, indicating Release on Request mode.

**Bits 03-00:** VMEbus Fairness Timeout (FAIR\_TO) – The value in this bit field determines how many 2 microsecond intervals, if any, the VMIVME-6016 will wait before asserting its VMEbus request if another VMEbus master is already using the bus. This fair-request scheme of bus arbitration avoids the bus starvation that can occur when multiple bus masters exist, especially multiple masters at the same priority level. A value of zero (0) here disables the fairness timeout and a value of binary 1111 causes the VMIVME-6016 to wait indefinitely for the other bus master to relinquish control. Note that the actual timeout value may be up to 2 microseconds longer than programmed. The default value for this field is binary 0010, indicating a 4 microsecond timeout.

#### 4.2.11 Master Size and Address Modifier Register (SZ\_AM)

The Master Size and Address Modifier Register is a read/write byte. This register contains the information needed to read or write data directly to or from VMEbus memory.

| Global Offset \$10 SZ_AM (Read/Write) |        |         |        |        |        |        |        |  |

|---------------------------------------|--------|---------|--------|--------|--------|--------|--------|--|

| Bit 07                                | Bit 06 | Bit 05  | Bit 04 | Bit 03 | Bit 02 | Bit 01 | Bit 00 |  |

| VME                                   | SIZE   | ADDRMOD |        |        |        |        |        |  |

Table 4.2.11-1. Master Size and Address Modifier Register Bit Map

M6016/T4.2.11-1

**Bits 07-06:** VMESIZE – contains a two-bit code representing the data width of the VMEbus access. The codes are:

| Bit 07 | Bit 06 | Code        | Description                  |  |  |

|--------|--------|-------------|------------------------------|--|--|

| 0      | 0      | VME_SIZE_32 | 32-bit size as VMEbus master |  |  |

| 1      | 0      | VME_SIZE_16 | 16-bit size as VMEbus master |  |  |

| 0      | 1      | VME_SIZE_8  | 8-bit size as VMEbus master  |  |  |

**Bits 05-00:** ADDRMOD – directly corresponds to the VMEbus address modifier (AM) bits AM5-AM0, bit 5 corresponding to AM5 through bit 0 corresponding to AM0. Typical (hexadecimal) VMEbus address modifier values are:

| Value | Description                                 |

|-------|---------------------------------------------|

| \$09  | Extended (A32) Nonprivileged Data           |

| \$0A  | Extended (A32) Nonprivileged Program        |

| \$0B  | Extended (A32) Nonprivileged Block Transfer |

| \$0D  | Extended (A32) Supervisory Data             |

| \$0E  | Extended (A32) Supervisory Program          |

| \$0F  | Extended (A32) Supervisory Block Transfer   |

| \$29  | Short I/O (A16) Nonprivileged Data          |

| \$2D  | Short I/O (A16) Supervisory Data            |

| \$39  | Standard (A24) Nonprivileged Data           |

| \$3A  | Standard (A24) Nonprivileged Program        |

| \$3B  | Standard (A24) Nonprivileged Block Transfer |

| \$3D  | Standard (A24) Supervisory Data             |

| \$3E  | Standard (A24) Supervisory Program          |

| \$3F  | Standard (A24) Supervisory Block Transfer   |

The power up or reset default value for the SZ\_AM register is \$B9 indicating standard A24 nonprivileged VMEbus addressing using 16-bit transfers.

#### 4.2.12 Self-Test Procedure Register (ST\_PROC)

This register determines the set of self-test procedures that the CPU executes when the SLFTST bit in the CR0 register is set to one.

| Global Offset \$11 ST_PROC (Read/Write) |                 |            |            |           |           |            |           |  |  |  |

|-----------------------------------------|-----------------|------------|------------|-----------|-----------|------------|-----------|--|--|--|

| Bit 07                                  | Bit 06          | Bit 05     | Bit 04     | Bit 03    | Bit 02    | Bit 01     | Bit 00    |  |  |  |

| RESERVED                                | 0               | TEST_DMA_R | TEST_DMA_W | TEST_BERR | TEST_UART | TEST_TIMER | TEST_VINT |  |  |  |

|                                         | M6016/T4.2.12-1 |            |            |           |           |            |           |  |  |  |

Table 4.2.12-1. Self-Test Procedure Register Bit Map

The following table is a brief summary of the tests. See Section 4.6 for details on self-testing.

| Bit   | Code       | Description                        |

|-------|------------|------------------------------------|

| Bit 5 | TEST_DMA_R | VMEbus DMA read (bus> board) test  |

| Bit 4 | TEST_DMA_W | VMEbus DMA write (board> bus) test |

| Bit 3 | TEST_BERR  | Self-access BERR test              |

| Bit 2 | TEST_UART  | UART test (local loopback)         |

| Bit 1 | TEST_TIMER | Timer test                         |

| Bit 0 | TEST_VINT  | VMEbus interrupt test              |

## 4.2.13 Error Interrupt Control Register (ER\_MSK)

The Error Interrupt Control Register is a read/write byte. Bits not mentioned below must remain set to zero (0).

| Table 4.2.13-1. | Error Inter | rupt Control | Register Bit | Map |

|-----------------|-------------|--------------|--------------|-----|

|                 |             |              |              |     |

| Global Offset \$12 ER_MSK (Read/Write)                                                          |          |                                                      |  |  |  |        |        |  |  |

|-------------------------------------------------------------------------------------------------|----------|------------------------------------------------------|--|--|--|--------|--------|--|--|

| Bit 07         Bit 06         Bit 05         Bit 04         Bit 03         Bit 02         Bit 0 |          |                                                      |  |  |  | Bit 01 | Bit 00 |  |  |

| REGBUSY_MSK                                                                                     | RFNZ_MSK | RFNZ_MSK ST_FAIL_MSK HDWE_ERR_MSK BERR_MASK ER_LEVEL |  |  |  |        |        |  |  |

M6016/T4.2.13-1

**Bit 07:** Register Busy Transition to Zero (REGBUSY\_MSK) – When this bit is set to one (1), a global interrupt will occur whenever data written to the CR0, CR1, GO, TX, or the RX registers has been interpreted by the firmware of the VMIVME-6016. This interrupt may be used as a handshake method in place of setting and polling the REGBUSY bit of the GST register.

- **<u>Bit 06:</u>** Reserved Field Nonzero (RFNZ\_MSK) When this bit is set to one (1), a Reserved Field set to nonzero (RFNZ status) can trigger this interrupt.

- **<u>Bit 05:</u>** Self-Test Failed (ST\_FAIL\_MSK) When this bit is set to one (1), a self-test failure (STFAIL status) can trigger this interrupt.

- **<u>Bit 04:</u>** Hardware Error (HDWE\_ERR\_MSK) When this bit is set to one (1), a hardware error (HDWEERR status) can trigger this interrupt.

- **Bit 03:** Bus Error (BERR\_MSK) When this bit is set to one (1), a VMEbus error (BERR status) caused by a transfer operation initiated by this board can trigger this interrupt.

- **Bits 02-00:** VMEbus Interrupt Level (ER\_LEVEL) These three bits set the level of the error interrupt from 1-7. If all three bits are clear, the interrupt is effectively disabled since there is no VMEbus level 0 interrupt.

#### 4.2.14 Error Interrupt Vector Register (ER\_VEC)

The Error Interrupt Vector register is a byte-wide read/write interrupt vector register. This register should be initialized to hold a standard VMEbus interrupt vector.

| Table 4.2.14-1. | Error | Interrupt | Vector | Register | Bit Map |

|-----------------|-------|-----------|--------|----------|---------|

|                 |       |           |        |          |         |

| Global Offset \$13 ER_VEC (Read/Write) |              |        |        |        |        |        |        |  |  |

|----------------------------------------|--------------|--------|--------|--------|--------|--------|--------|--|--|

| Bit 07                                 | Bit 06       | Bit 05 | Bit 04 | Bit 03 | Bit 02 | Bit 01 | Bit 00 |  |  |

| VECTOR                                 |              |        |        |        |        |        |        |  |  |

|                                        | M6016/T4.2.1 |        |        |        |        |        |        |  |  |

#### 4.2.15 Buffer Base Register (BUFBASE)

The Buffer Base register is a read/write longword. When the VMIVME-6016 is in master mode (MASTER bit in CR0), this register contains the VMEbus address for all the user buffers. The contents of the Master Size and Address Modifier Register (SZ\_AM) are used to determine access type when addressing the buffers. Note that during VMEbus standard (A24) addressing, the most significant byte of BUFBASE is ignored.

When the VMIVME-6016 is in slave mode, BUFBASE determines the standard or extended VMEbus base address of the on-board memory block used for user buffers. The SLV\_32 bit in CR0 determines whether the VMIVME-6016 responds to standard (A24) or extended (A32) addressing. The slave mode base address must be a multiple of a number that depends on the amount of memory populated:

| Total Memory | User Memory | Slave Base Multiplier |

|--------------|-------------|-----------------------|

| 256 Kbytes   | 128 Kbytes  | 256 Kbytes (\$40000)  |

| 512 Kbytes   | 256 Kbytes  | 512 Kbytes (\$80000)  |

| 1 Mbyte      | 512 Kbytes  | 1 Mbyte (\$100000)    |

| 2 Mbytes     | 1 Mbyte     | 2 Mbytes (\$200000)   |

#### 4.2.16 Global Status Register (GST)

The Global Status register is a 16-bit register that contains bits that reflect VMIVME-6016 status for conditions independent of channel number. Bits not mentioned below must remain set to zero (0). VMIC recommends that this register be modified using indivisible RMW operations. See Section 4.4.9 for details. To modify just the REGBUSY bit, a byte write can be performed to offset \$19 instead of using an RMW operation.

|         | Global Offset \$18 GST (Read/Write) |        |        |        |        |         |                 |  |  |  |

|---------|-------------------------------------|--------|--------|--------|--------|---------|-----------------|--|--|--|

| Bit 15  | Bit 14                              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 09  | Bit 08          |  |  |  |

| ANYERR  | GLBILL                              | STBUSY | SCON   | RFNZ   | STFAIL | HDWEERR | BERR            |  |  |  |

|         |                                     |        |        |        |        |         | M6016/T4.2.16-1 |  |  |  |

| Bit 07  | Bit 06                              | Bit 05 | Bit 04 | Bit 03 | Bit 02 | Bit 01  | Bit 00          |  |  |  |

| REGBUSY | 0                                   | 0      | 0      | 0      | 0      | 0       | 0               |  |  |  |

Table 4.2.16-1. Global Status Register Bit Map

**Bit 15:** Any Error (ANYERR) -- This bit is set to one (1) whenever one or more of the following bits are set:

| Bit     | Description                     |  |  |  |

|---------|---------------------------------|--|--|--|

| GLBILL  | Illegal Global Register Content |  |  |  |

| RFNZ    | Reserved Field Nonzero          |  |  |  |

| STFAIL  | Self-Test Error                 |  |  |  |

| HDWEERR | Hardware Error                  |  |  |  |

| BERR    | BERR* on VMEbus master cycle    |  |  |  |

**<u>Bit 14:</u>** Global Register Illegal (GLBILL) – This bit is set to one (1) whenever the VMIVME-6016 detects that the content of a global register violates the restrictions on it.

- **Bit 13:** Self-Test Busy (STBUSY) This bit is set when the VMIVME-6016 is busy running one of the tests controlled by the Run Self-Test bit (SLFTST) of the CR0 register. After initializing these tests, the host program should wait for this bit to clear before testing the Self-Test Failed bit (STFAIL) in this register to determine the success of the self-tests.

- **Bit 12:** VMEbus System Controller (SCON) This bit is set to one (1) if the VMIVME-6016 board is jumper-configured as a VMEbus slot 1 controller. See Section 5.3.2 for details.

- **Bit 11:** Reserved Field Nonzero (RFNZ) This bit is set to one (1) if any reserved bits in any VMIVME-6016 registers are nonzero. If this bit is set, the Any Error bit (bit 15) will also be set. Note that unused register space, which includes space or fields not mentioned in Sections 4.2 and 4.3, is also reserved and must be completely clear. All reserved bits are clear by default after power-up or reset.

- **Bit 10:** Self-Test Failed (STFAIL) This bit is set to one (1) if any of the self-tests requested by the Run Self-Test bit (SLFTST) of the CR0 Register have failed. This bit is not valid if the Self-Test Busy bit is set. If this bit is set, the Any Error bit (ANYERR) will also be set.

- **Bit 09:** Hardware Error (HDWEERR) If this bit is set to one (1), some local hardware error other than a VMEbus Error (BERR) has occurred. If this bit is set, the Any Error bit (ANYERR) will be set as well.

- **Bit 08:** VMEbus Error (BERR) This bit is set if the VMIVME-6016 initiates an operation that results in a bus error. Note that the VMIVME-6016 has a programmable bus timer if it is configured as the system controller (see Section 5.3.2 for details) and has only a fixed-interval bus timer (about 50 microseconds) otherwise. This bit will also be set, however, if a VMIVME-6016 DMA transfer points to the VMIVME-6016 board (a self access). If this bit is set, the Any Error bit (ANYERR) will be set as well.

- **Bit 07:** Register Busy (REGBUSY) Any write operation into any area of the CR0, CR1, GO, TX, or RX registers causes an interrupt to the firmware on the VMIVME-6016. Until the VMIVME-6016 firmware interprets the new data, the contents of these registers may not reflect the expected results. Register Busy provides a handshake method that allows the host computer software to ensure that the register contents have taken effect. The following code fragment illustrates the use of REGBUSY.

```

/*

* .....

* Sample code fragment to set a GO bit.

* GSTLO refers to lower byte of GST at offset $19.

* .....

*/

#define REGBSY 0X80

while((v6016->GSTLO & REGBSY) != 0); /* let previous finish */

v6016->GSTLO |= REGBSY; /* Avoid races by presetting REGBUSY */

v6016->GO |= 0x400; /* Set a GO bit */

```

The following code fragment may be used when reading the registers:

/\*

\* ......

\* Sample code fragment to read the CR0 register and

\* print a message if the LED is emitting light

\* .....

\*/

while((v6016->GSTLO & REGBSY)!= 0); /\*let previous finish \*/

if (v6016->CR0 & LEDN == 0) puts ( "The LED is on" );

#### NOTE:

# THE ABOVE HANDSHAKE APPLIES ONLY TO THE CR0, CR1, GO, TX, AND RX REGISTERS; THE REMAINING VMIVME-6016 REGISTERS MAY BE WRITTEN OR READ WITHOUT WAITING FOR REGBUSY TO BE ZERO.

The REGBUSY\_MSK interrupt (see Section 4.2.13) may be used to get notification, rather than by polling the GST. See also Section 4.4.8.

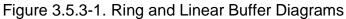

#### 4.2.17 Master Granularity (MAS\_GRN)

This register is meaningful only in master mode (user buffers off-board). If the number here is zero (0), it represents 256. The user buffer's TX and RX are each allocated this value times 4096 bytes in VMEbus space. Total buffer space is MAS\_GRN times 4096 times 32 buffers. The value of SZ\_UBUF for each channel determines how much of the buffer space allocated for the channel is actually used.

| Global Offset \$1A MAS_GRN (Read/Write) |        |        |        |        |        |        |        |  |

|-----------------------------------------|--------|--------|--------|--------|--------|--------|--------|--|

| Bit 07                                  | Bit 06 | Bit 05 | Bit 04 | Bit 03 | Bit 02 | Bit 01 | Bit 00 |  |

| VALUE                                   |        |        |        |        |        |        |        |  |

Table 4.2.17-1. Master Granularity Register Bit Map

M6016/T4.2.17-1

#### 4.3 CHANNEL CONTROL BLOCKS

Each of the 16 channels of the VMIVME-6016 has a 14-byte Channel Control Block associated with it. These CCBs follow the Global Registers described in Section 4.2, in ascending order, from channel 0 through channel 15. Table 4.3.1 shows the structure of one of the CCBs, followed by its description. Each CCB has the same mapping. The CCB registers are offsets from the base offset of the associated CCB. The Global Registers and the CCBs together take up exactly 256 bytes of short I/O space.

| Name    | Meaning                                                                                                         |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------|--|--|

| CST     | Channel Status                                                                                                  |  |  |

| CH_MSK  | Channel Interrupt Mask                                                                                          |  |  |

| CH_VEC  | Channel Interrupt Vector                                                                                        |  |  |

| EOB     | End-of-block code                                                                                               |  |  |

| XOFF    | Flow control XOFF code                                                                                          |  |  |

| XON     | Flow control XON code                                                                                           |  |  |

| BRK_DUR | BREAK duration in ms +0/-1                                                                                      |  |  |

| SZ_RING | Internal Ring size                                                                                              |  |  |

| LO_RING | Internal Ring low water mark                                                                                    |  |  |

| HI_RING | Internal Ring high water mark                                                                                   |  |  |

| CH_CON1 | Channel Control Byte 1                                                                                          |  |  |

| CH_CON2 | Channel Control Byte 2                                                                                          |  |  |

| SZ_UBUF | User Buffer Size                                                                                                |  |  |

|         | CST<br>CH_MSK<br>CH_VEC<br>EOB<br>XOFF<br>XON<br>BRK_DUR<br>SZ_RING<br>LO_RING<br>HI_RING<br>CH_CON1<br>CH_CON2 |  |  |

Table 4.3-1. VMIVME-6016 Channel Control Block Map

The registers in a CCB are valid only for the particular channel with which the CCB is associated. The VMIVME-6016 can modify the Channel Status (CST) registers at any time. It does not modify any other register in any CCB, except to set up default conditions at power up or hard reset time.

The user should not modify any register in a CCB while its channel is active (associated GO bit set to one).

# 4.3.1 Channel Status Register (CST)