# VMIVME-2511 Programmable I/O Board

**Product Manual**

12090 South Memorial Parkway Huntsville, Alabama 35803-3308, USA (256) 880-0444 ◆ (800) 322-3616 ◆ Fax: (256) 882-0859

#### COPYRIGHT AND TRADEMARKS

© Copyright July 2001. The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

AMXbus, BITMODULE, COSMODULE, DMAbus, IOMax, IOWorks Foundation, IOWorks Manager, IOWorks Server, MAGICWARE, MEGAMODULE, PLC ACCELERATOR (ACCELERATION), Quick Link, RTnet, Soft Logic Link, SRTbus, TESTCAL, "The Next Generation PLC", The PLC Connection, TURBOMODULE, UCLIO, UIOD, UPLC, Visual Soft Logic Control(ler), *VMEaccess*, VMEbus Access, *VMEmanager*, *VMEmonitor*, VMEnet, VMEnet II, and *VMEprobe* are trademarks and The I/O Experts, The I/O Systems Experts, The Soft Logic Experts, and The Total Solutions Provider are service marks of VMIC.

The I/O man figure, IOWorks, IOWorks man figure, UIOC, Visual IOWorks, and the VMIC logo are registered trademarks of VMIC.

ActiveX, Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, Windows NT, and XENIX are registered trademarks of Microsoft Corporation.

Celeron and MMX are trademarks, and Intel and Pentium are registered trademarks of Intel Corporation.

PICMG and CompactPCI are registered trademarks of PCI Industrial Computer Manufacturers' Group.

Other registered trademarks are the property of their respective owners.

#### **VMIC**

#### All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless granted express written permission from VMIC.

Revised 7-12-01

# Table of Contents

| List of Figures                                                   | 5  |

|-------------------------------------------------------------------|----|

| List of Tables                                                    | 7  |

| VMIC Safety Summary                                               | 9  |

| Safety Symbols                                                    | 11 |

| Chapter 1 - Overview                                              | 13 |

| Functional Description                                            | 14 |

| General Description                                               | 15 |

| PA0 to PA7 and PB0 to PB7 (Port A and Port B)                     | 16 |

| H1 to H4 (Handshake Pins (I/O depending on the mode and submode)) | 16 |

| Port C (PC0 to PC7/Alternate Function)                            | 16 |

| Port Control Structure                                            | 17 |

| Reference Material List                                           | 21 |

| Description and Specifications                                    | 22 |

| Motorola MC68153 BIM and MC68230 PI/T                             | 23 |

| Chapter 2 - Theory of Operation                                   | 25 |

| Operational Overview                                              | 30 |

| I/O Data Transfer Description                                     | 31 |

| Interrupt Capability                                              | 32 |

| The MC68230 Parallel Interface/Timer                              | 33 |

| Chapter 3 - Programming                                           | 35 |

| BIM and PI/T Register Map                                         | 36 |

| Detailed Programming                                              | 47 |

| Programming the MC68153 BIM                                       | 47 |

| Programming the MC68230 PI/T                                      |    |

| Timer Programming                                                 | 48 |

# VMIVME-2511 Programmable I/O Board Product Manual

| Interrupt Programming                           |    |

|-------------------------------------------------|----|

| Chapter 4 - Configuration and Installation      |    |

| Unpacking Procedures                            |    |

| Physical Installation                           |    |

| Switch and Jumper Locations                     |    |

| Address Modifiers                               |    |

| Jumper and I/O Configuration                    |    |

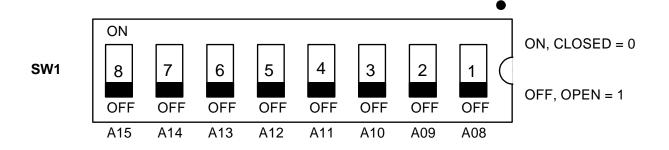

| Address Selection Switches                      |    |

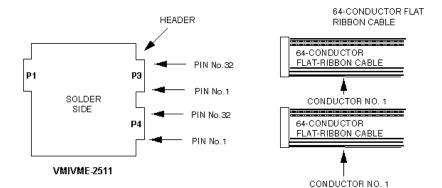

| I/O Cable and Card-Edge Connector Configuration |    |

| Chapter 5 - Maintenance                         | 67 |

| Maintenance Prints                              |    |

# List of Figures

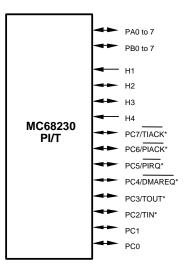

| Figure 1 PI/T Pin Assignments                                                   | 15 |

|---------------------------------------------------------------------------------|----|

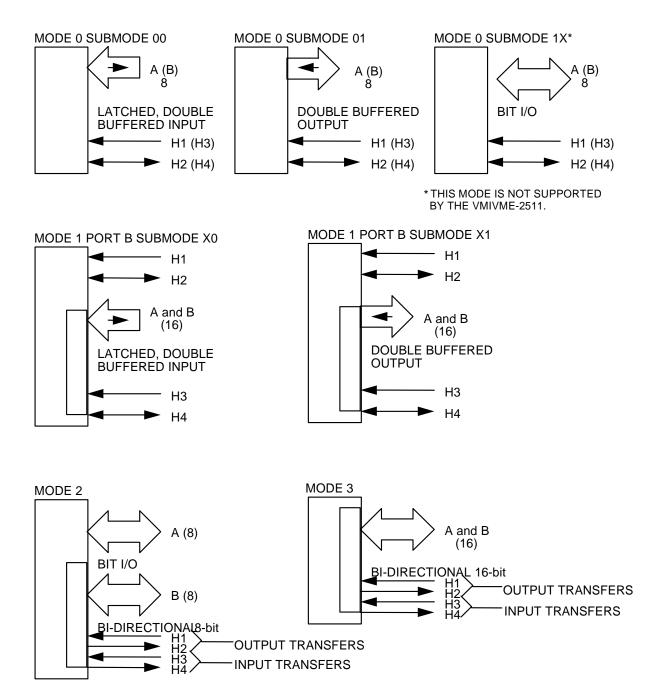

| Figure 2 Port Mode Layout                                                       | 20 |

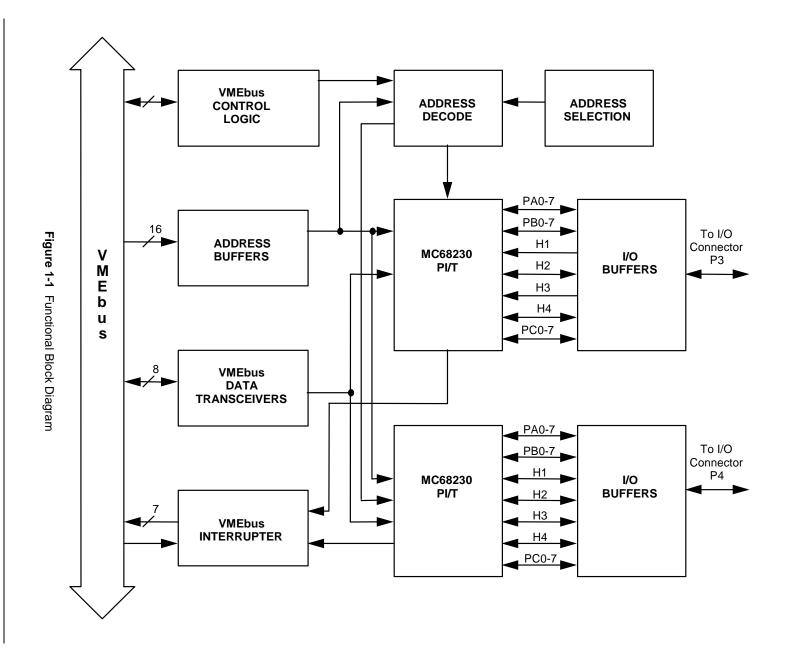

| Figure 1-1 Functional Block Diagram                                             | 26 |

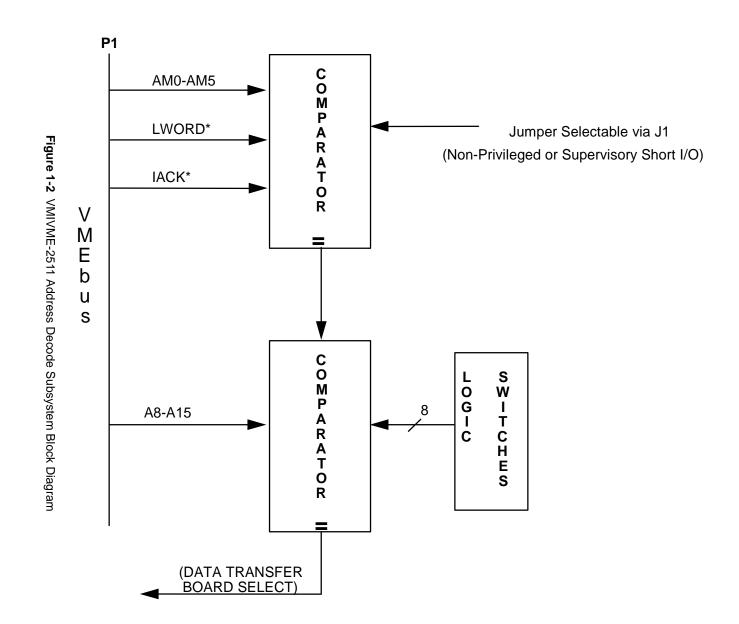

| Figure 1-2 VMIVME-2511 Address Decode Subsystem Block Diagram                   | 27 |

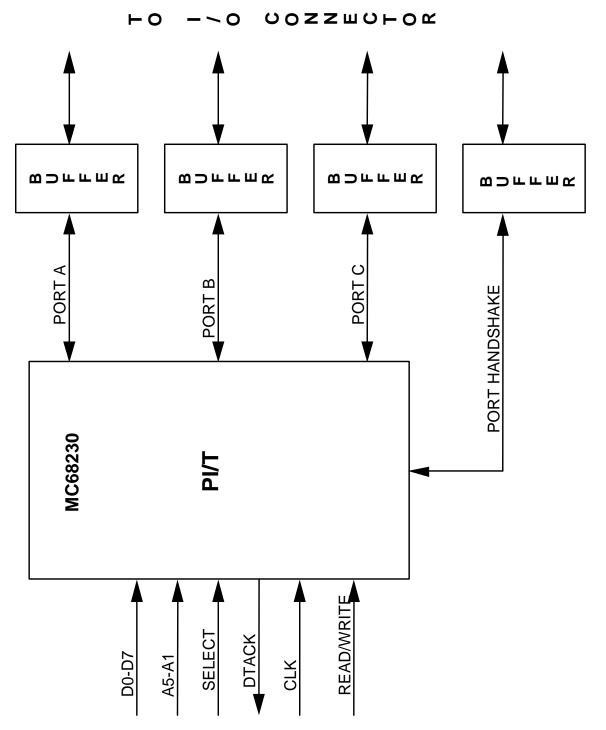

| Figure 1-3 Block Diagram of Parallel Interface/Timer and I/O Port Control Logic | 28 |

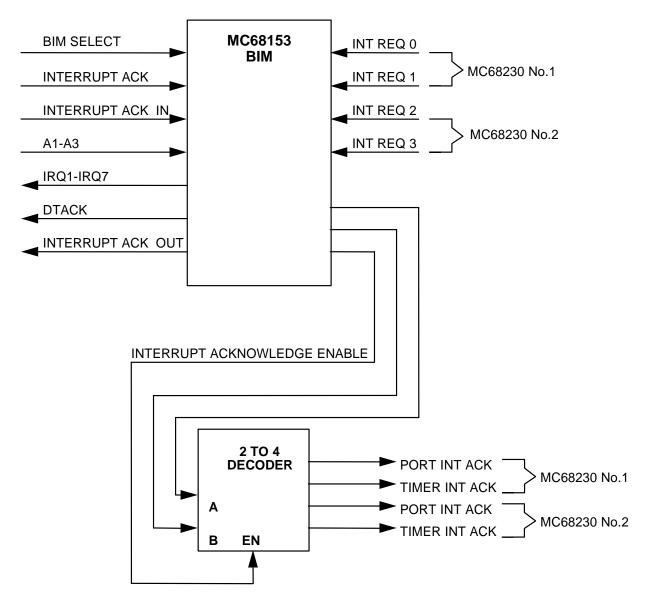

| Figure 1-4 VMIVME-2511 VMEbus Interrupter System                                | 29 |

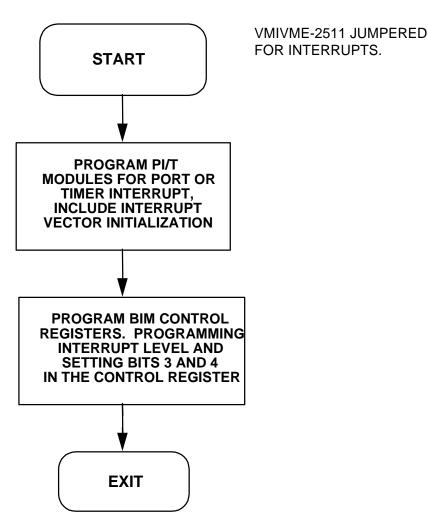

| Figure 2-1 Interrupt Programming Sequence                                       | 49 |

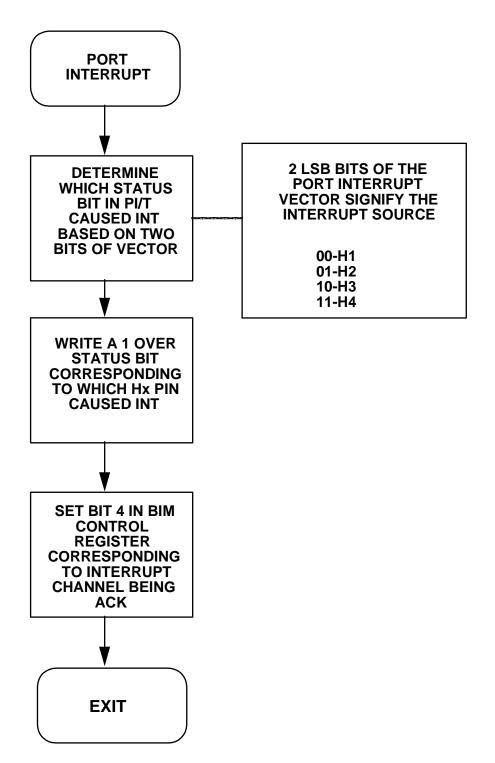

| Figure 2-2 Port Interrupt Routine                                               | 50 |

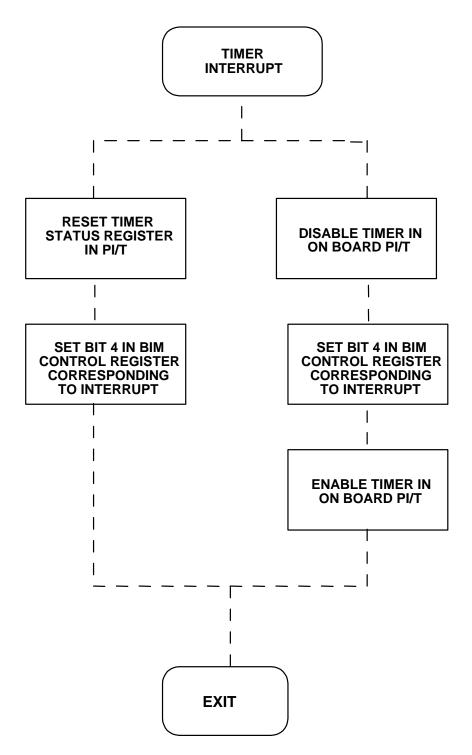

| Figure 2-3 Timer Interrupt Sequence                                             | 51 |

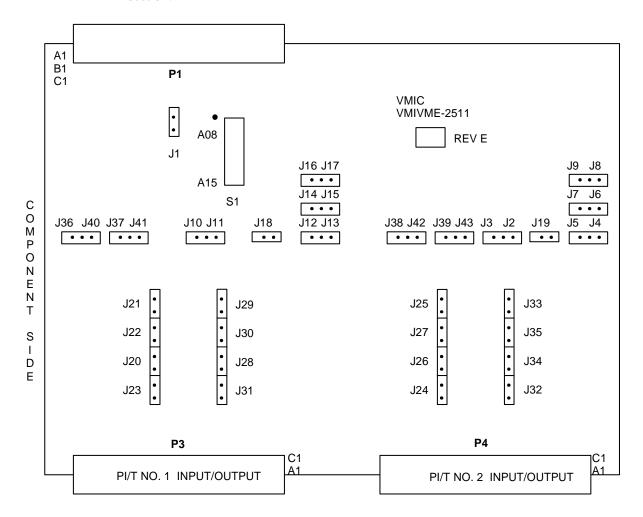

| Figure 3-1 Switch and Jumper Locations                                          | 56 |

| Figure 3-2 Address Select Switch, SW1                                           | 59 |

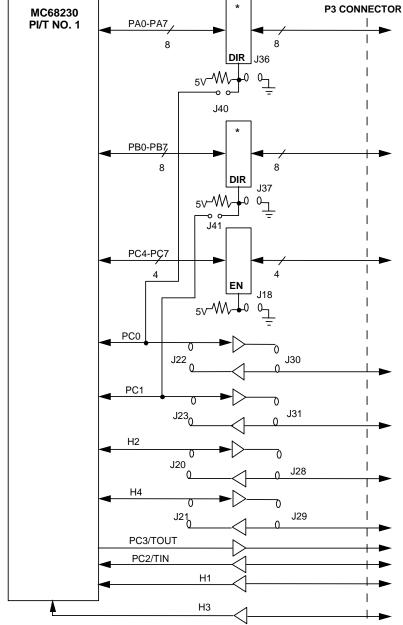

| Figure 3-3 I/O and Jumper Block Diagram for PI/T No. 1                          | 61 |

| Figure 3-4 I/O and Jumper Block Diagram for PI/T No. 2                          | 62 |

| Figure 3-5 Cable Connector Configuration                                        | 65 |

# List of Tables

| Table 1 PI/T I/O Channel Definitions                       |    |

|------------------------------------------------------------|----|

| Table 2 Port Mode Control Summary                          | 18 |

| Table 2-1 PI/T No. 1 (P3 Connector Byte Address Locations) | 36 |

| Table 2-2 BIM Register Map.                                | 37 |

| Table 2-3 PI/T No.1 Register Map                           | 38 |

| Table 2-4 PI/T No. 2 Register Map.                         | 42 |

| Table 2-5 PI/T No. 1 (P3 Connector Byte Address Locations) | 46 |

| Table 2-6 BIM Control Registers and Interrupt Source       | 47 |

| Table 2-7 PI/T I/O Channel Definitions                     | 48 |

| Table 3-1 Jumper Definition Table                          | 63 |

| Table 3-2 P3-PI/T No. 1 Pin and Function Assignments       | 65 |

| Table 3-3 P4-PI/T No. 2 Pin and Function Assignments       | 66 |

# **VMIC Safety Summary**

**NOTE:** The following general safety precautions must be observed during all phases of the operation, service and repair of this product. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture and intended use of this product. VMIC assumes no liability for the customer's failure to comply with these requirements.

#### **Ground the System**

To minimize shock hazard, the chassis and system cabinet must be connected to an electrical ground. A three-conductor AC power cable should be used. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet.

#### Do Not Operate in an Explosive Atmosphere

Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.

#### **Keep Away from Live Circuits**

Operating personnel must not remove product covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### Do Not Service or Adjust Alone

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### **Do Not Substitute Parts or Modify System**

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to VMIC for service and repair to ensure that safety features are maintained.

# **Dangerous Procedure Warnings**

Warnings, such as the example below, precede only potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

**WARNING:** Dangerous voltages, capable of causing death, are present in this system. Use extreme caution when handling, testing and adjusting.

# Safety Symbols

General definitions of safety symbols used in this manual:

| Symbol       | Description                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| <u></u>      | Product manual symbol: the product is marked with this symbol when it is necessary for the user to refer to the product manual in order to protect against damage to the system.                                                                                                                                           |  |  |  |  |  |

| <b>4</b>     | Indicates dangerous voltage (terminals fed from the interior by voltage exceeding 1000 volts are so marked).                                                                                                                                                                                                               |  |  |  |  |  |

|              | Protective conductor terminal. For protection against electrical shock in case of a fault. Used with field wiring terminals to indicate the terminal which must be connected to ground before operating equipment.                                                                                                         |  |  |  |  |  |

|              | Low-noise or noiseless, clean ground (earth) terminal. Used for a signal common, as well as providing protection against electrical shock in case of a fault. Before operating the equipment, terminal marked with this symbol must be connected to ground in the manner described in the installation (operation) manual. |  |  |  |  |  |

| → OR <u></u> | Frame or chassis terminal. A connection to the frame (chassis) of the equipment which normally includes all exposed metal structures.                                                                                                                                                                                      |  |  |  |  |  |

|              | Alternating current (power line).                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|              | Direct current (power line).                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|              | Alternating or direct current (power line).                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Symbol   | Description                                                                                                                                                                                                                                 |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| WARNING: | <b>WARNING</b> denotes a hazard. It calls attention to an operating procedure, a practice, a condition or the like, which, if not correctly performed or adhered to, could result in injury or death to personnel.                          |  |  |  |

| CAUTION: | <b>CAUTION</b> denotes a hazard. It calls attention to an operating procedure, a practice, a condition or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the system. |  |  |  |

| NOTE:    | <b>NOTE</b> denotes important information. It calls attention to an operating procedure, a practice, a condition or the like, which is essential to highlight.                                                                              |  |  |  |

# **Overview**

#### **Contents**

| Functional Description 1              | 4   |

|---------------------------------------|-----|

| General Description                   | . 5 |

| Port Control Structure                | 7   |

| Reference Material List               | !1  |

| Description and Specifications        | 22  |

| Motorola MC68153 BIM and MC68230 PI/T | 23  |

### Introduction to the VMIVME-2511

The VMIVME-2511 is a VMEbus-compatible, programmable I/O board. It utilizes two Motorola MC68230 Parallel Interface/Timer I.C.s and one Motorola MC68153 Bus Interrupter Module. The board also has the following features:

- 48 bits of I/O, unidirectional 8-bit and 16-bit, or bidirectional 8-bit and 16-bit

- $\bullet$  Interrupt generation logic allowing four interrupt sources (one timer interrupt and one port interrupt per MC68230)

- Optional high current drivers with 64 mA sink capability

- Two 24-bit programmable timers

- Software programmable timer modes

- Selectable handshake timer provides an interface flexible enough for connection to a wide variety of low, medium or high-speed peripherals or other computer systems

# **Functional Description**

The VMIVME-2511 Programmable I/O Board consists of VMEbus foundation logic, interrupt control logic and I/O control logic associated with the parallel interface/timer modules. The VMEbus foundation logic contains address decoding logic and data transfer control logic allowing the VMEbus to write and read 8-bit data transfers. The interrupt control logic utilizes the Motorola MC68153 BIM which allows port and timer interrupts from each parallel interface/timer. The interrupt requests to the CPU are issued by the MC68153 when requested to do so by a Parallel Interface/Timer (MC68230). The parallel I/O ports are programmable to allow unidirectional 8-bit or 16-bit ports and bidirectional 8-bit or 16-bit ports. A high current driver option is also available. When the high current option is employed, ports A and B are programmable as outputs only.

## **General Description**

The VMIVME-2511 is designed utilizing two Motorola MC68230 Parallel Interface/Timers (PI/Ts) and one MC68153 Bus Interrupter Module (BIM) to support all board functions as shown in Figure 1.

The VMIVME-2511 is capable of handling four interrupt requests. Each PI/T module is capable of two requests, a port interrupt request and a timer interrupt request. The four interrupt request signals (two from PI/T No. 1 and two from PI/T No. 2) are connected to the BIM, giving full interrupt support for both PI/T modules. Each PI/T module has two on-board interrupt vector registers programmable by the user. Table 1 on page 17 provides a summary of operational modes for the PI/T.

The MC68230 Parallel Interface/Timer provides a versatile, double-buffered, parallel interface, and an operating system oriented timer to VMEbus systems. The parallel interfaces operate in unidirectional or bi-directional modes, either 8 or 16 bits wide. In the unidirectional mode, an associated data direction register determines whether the port pins are inputs or outputs. In the bi-directional mode, the data direction registers are ignored, and the direction is determined dynamically by the state of four handshake pins. These programmable handshake pins provide an interface flexible enough for connection to a wide variety of low, medium or high-speed peripherals or the other computer systems. The PI/T ports allow use of vectored or auto vectored interrupts, and can generate periodic interrupts, a square wave or a single interrupt after a programmed time period. Also, the PI/T ports can be used for elapsed time measurement, or as a device watchdog. MC68230 I/O pins available to the user are shown in Figure 1.

Figure 1 PI/T Pin Assignments

**NOTE:** (\*) in the previous figure designates an individually programmable dual function pin.

#### PA0 to PA7 and PB0 to PB7 (Port A and Port B)

Ports A and B are 8-bit ports that may be linked to form a 16-bit port in certain modes. The ports may be controlled in conjunction with the handshake pins H1 to H4. For stabilization during system power-up, Ports A and B have internal pull-up resistors to VCC. All port pins are active high.

#### H1 to H4 (Handshake Pins (I/O depending on the mode and submode))

Handshake pins H1 to H4 are multi-purpose pins that (depending on the operational mode) may provide an interlocked handshake, a pulsed handshake, an interrupt input (independent of data transfers) or simple I/O pins. For stabilization during system power-up, H2 and H4 have internal pull-up resistors to VCC. Their sense (active high or low) may be programmed in the port general control register bits 3 to 0. The instantaneous level of the handshake pins can be read from the port status register independent of the mode.

#### Port C (PC0 to PC7/Alternate Function)

This port can be used as eight general-purpose I/O pins (PC0 to PC7), or any combination of six special function pins and two general-purpose I/O pins (PC0 to PC1). (Each dual function pin can be standard I/O or a special function independent of the other Port C pins.). The dual function pins are defined in the following paragraphs. When used as Port C pin, these pins are active high. They may be individually programmed as inputs or outputs by the Port C data direction register.

The alternate functions (TIN, TOUT and TIACK) are timer I/O pins. TIN may be used as a rising-edge triggered external clock input or an external run/halt control pin (the timer is in the run state if run/halt is high, and in the halt state if run/halt is low). TOUT may provide an active low timer interrupt request output or a general purpose square-wave output, initially high. TIACK is an active low high-impedance input used for timer interrupt acknowledge.

Port A and B functions have an independent pair of active low interrupt request (PIRQ) and interrupt acknowledge (PIACK) pins.

# **Port Control Structure**

The primary focus of most applications will be on Ports A and B, the handshake pins and the port interrupt pins. They are controlled using the port general control register, which contains a 2-bit field that specifies a set of four operation modes. These modes govern the overall operation of the ports and determine their interrelationships. Some modes require additional information from each port's control register to further define its operation. In each port control register, there is a 2-bit submode field that serves this purpose. Each port mode/submode combination specifies a set of programmable characteristics that fully define the behavior of that port and the behavior of two of the handshake pins. This structure is summarized in Table 1 below and Table 2 on page 18.

Table 1 PI/T I/O Channel Definitions

| Pin(s)       | Description                                                              |  |  |  |  |

|--------------|--------------------------------------------------------------------------|--|--|--|--|

| (PA0 to PA7) | All eight bits, input or output depending on jumper configuration chosen |  |  |  |  |

| (PB0 to PB7) | All eight bits, input or output depending on jumper configuration chosen |  |  |  |  |

| (PC4 to PC7) | All four bits, input or output depending on jumper configuration chosen  |  |  |  |  |

| H1           | Input only                                                               |  |  |  |  |

| H2           | Configured as input or output                                            |  |  |  |  |

| Н3           | Input only                                                               |  |  |  |  |

| H4           | Configured as input or output                                            |  |  |  |  |

| PC0          | Configured as input or output                                            |  |  |  |  |

| PC1          | Configured as input or output                                            |  |  |  |  |

| PC2/TIN      | Input only                                                               |  |  |  |  |

| PC3/TOUT     | Output only                                                              |  |  |  |  |

Table 2 Port Mode Control Summary

| Mode 0 (Unidirectio | Mode 0 (Unidirectional 8-bit Mode) |                 |                                                                                                                                        |

|---------------------|------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Port A              | Submode                            | 00              | Double-buffered input                                                                                                                  |

|                     |                                    | H1              | Latches input data                                                                                                                     |

|                     |                                    | H2              | Status/interrupt generating input, general-purpose output or operation with H1 in the interlocked or pulsed input handshake protocols  |

|                     | Submode                            | 01              | Double-buffered output                                                                                                                 |

|                     |                                    | H1              | Indicates data received by peripheral                                                                                                  |

|                     |                                    | H2              | Status/interrupt generating input, general-purpose output or operation with H1 in the interlocked or pulsed output handshake protocols |

|                     | Submode                            | 1X              | Bit I/O*                                                                                                                               |

|                     |                                    | H1              | Status/interrupt generating input                                                                                                      |

|                     |                                    | H2              | Status/interrupt generating input or general purpose output                                                                            |

| Port B              |                                    | H3<br>and<br>H4 | Identical to Port A, H1 and H2                                                                                                         |

| Mode 1 (Unidirectional 16-bit Mode) |         |    |                                                                                                                                       |

|-------------------------------------|---------|----|---------------------------------------------------------------------------------------------------------------------------------------|

| Port A                              | Submode | XX | (Not used)                                                                                                                            |

| Doubled-buffered data               |         | H1 | Status/interrupt generating input                                                                                                     |

| (Most significant)                  |         | H2 | Status/interrupt generating input or general-purpose output                                                                           |

| Port B                              |         | X0 | Unidirectional 16-bit input                                                                                                           |

| Double-buffered data                |         | Н3 | Indicated data received by peripheral                                                                                                 |

| (Least significant)                 |         | H4 | Status/interrupt generating input, general-purpose output or operation with H3 in the interlocked or pulsed output handshake protocol |

Table 2 Port Mode Control Summary (Continued)

| Mode 2 (Bi-directional 8-bit Mode) |         |    |                                                                           |

|------------------------------------|---------|----|---------------------------------------------------------------------------|

| Port A                             | Submode | XX | Not used                                                                  |

| Bit I/O (With no handshaking pins) |         |    |                                                                           |

| Port B                             | Submode | XX | (Not used)                                                                |

| Bi-directional 8-bit               |         | H1 | Indicates output data received by peripheral                              |

| data (double- buffered)            |         | H2 | Operation with H1 in the interlocked or pulsed output handshake protocols |

|                                    |         | Н3 | Latches input data                                                        |

|                                    |         | H4 | Operation with H3 in interlocked or pulsed input handshake protocols      |

| Mode 3 (Bi-directional 16-bit Mode) |         |    |                                                                           |

|-------------------------------------|---------|----|---------------------------------------------------------------------------|

| Port A                              | Submode | XX | (Not used)                                                                |

| Double-buffered data                |         |    |                                                                           |

| (Most significant)                  |         |    |                                                                           |

| Port B                              | Submode | XX | (Not used)                                                                |

| Double-buffered data                |         | H1 | Indicates output data received by peripheral                              |

| (Least significant)                 |         | H2 | Operation with H1 in the interlocked or pulsed output handshake protocols |

|                                     |         | Н3 | Latches input data                                                        |

|                                     |         | H4 | Operation with H3 in the interlocked or pulsed input handshake protocols  |

Figure 2 Port Mode Layout

### **Reference Material List**

Refer to "The VMEbus Specification" for a detailed explanation of the VMEbus. "The VMEbus Specification" is available from:

VITA

VMEbus International Trade Association

10229 N. Scottsdale Road

Scottsdale, AZ 85253

(602) 951-8866

The following Application and Configuration Guides are available from VMIC to assist in the selection, specification and implementation of systems based on VMIC's products:

| Title                                                        | Document No.   |

|--------------------------------------------------------------|----------------|

| Digital Input Board Application Guide                        | 825-000000-000 |

| Low Level Analog I/O Configuration Guide                     | 825-000000-001 |

| Change-of-State Application Guide                            | 825-000000-002 |

| Digital I/O (with Built-in-Test) Product Line Description    | 825-000000-003 |

| Synchro/Resolver (Built-in-Test) Configuration Guide         | 825-000000-004 |

| Analog I/O Products (with Built-in-Test) Configuration Guide | 825-000000-005 |

| Connector and I/O Cable Application Guide                    | 825-000000-006 |

# **Description and Specifications**

The following are sources for description and specification information.

The 48-bit Digital Parallel Input/Output Board specification (Document number 800-022511-000) is available from:

VMIC 12090 South Memorial Parkway Huntsville, AL 35803-3308 PH: 256-880-0444 1-800-240-7782 FX: 256-650-7245

Email: customer.service@vmic.com Internet: www.vmic.com PDF for the VMIVME-2511: www.analog.digital.vmic.com/pdf/800-022511-000.pdf

The TS68230CP8 HCMOS Parallel Interface/Timer specification is available from:

STMicroelectronics 1000 East Bell Road Phoenix, AZ 85022 PH: 602-485-6100 FX: 602-485-6102 Internet: www.us.st.com

PDF for the TS68230CP8: www.us.st.com/stonline/books/pdf/docs/2353.pdf

The Epic Ei68C153 Bus Interrupter Module (VME) specification is available from:

Epic Semiconductor, Inc. 4801 S. Lakeshore Dr. Suite 203 Tempe, AZ 85282 PH: 480-730-1000 FX: 480-838-4740

Internet: www.epicsemi.com PDF for the Ei68C153: www.epicsemi.com/153.pdf

### Motorola MC68153 BIM and MC68230 PI/T

The VMIVME-2511 was originally manufactured using the Motorola MC68153 BIM and MC68230 PI/T, both of which are now out of production. The Epic Ei68C153 BIM and STMicroelectronics TS68230CP8 PI/T are being used as replacements on all newly-manufactured VMIVME-2511 boards. Any references to the Ei68C153 and TS68230CP8 in this document are also applicable to the MC68153 and MC68230.

# Theory of Operation

### **Contents**

| Operational Overview                 | 30 |

|--------------------------------------|----|

| I/O Data Transfer Description        | 3  |

| Interrupt Capability                 | 32 |

| The MC68230 Parallel Interface/Timer |    |

### Introduction

The VMIVME-2511 consists of eight major subsystems as illustrated in Figure 1-1 on page 26. Each subsystem is further broken down into more detailed block diagrams as shown in Figure 1-2 on page 27 through Figure 1-4 on page 29.

Figure 1-2 shows the address decoding scheme and the address modifier jumper (J1), which is used to select the short I/O space to be used. A block diagram of the connections for the PI/T is shown in Figure 1-3 on page 28, while Figure 1-4 shows the basic configuration of the BIM.

Figure 1-3 Block Diagram of Parallel Interface/Timer and I/O Port Control Logic

Figure 1-4 VMIVME-2511 VMEbus Interrupter System

# **Operational Overview**

As noted in the functional block diagram in Figure 1-1 on page 26, the VMIVME-2511 utilizes two MC68230 modules. Each MC68230 Parallel Interface/Timer module (PI/T) has three I/O ports and some additional handshake interface. The handshake signals and the I/O ports of each module are in turn mapped into a single I/O connector. The module that is associated with the P3 connector will be referred to in the discussion which follows as PI/T No. 1. The module associated with the P4 connector will be referred to as PI/T No. 2. Although the discussions may be about PI/T No. 1, they are equally applicable to PI/T No. 2.

To perform I/O data transfers with the VMIVME-2511, prepare the appropriate PI/T for the type of transfer to be made and then process the data. The PI/T to be used will depend upon the input channel of interest. The type of transfer will have to be programmed in the control registers of the PI/T. See "Description and Specifications" on page 22, and "Motorola MC68153 BIM and MC68230 PI/T" on page 23 for information on obtaining a specification containing a detailed description of the set-up and use of the MC68230.

To achieve interrupt processing with the VMIVME-2511, the chosen PI/T module is programmed for port or timer interrupts. Then, if the proper channel of the MC68153 Bus Interrupter Module (BIM) is enabled, the particular interrupt source of interest will be acknowledged by the system processor. Some jumper selection is required, because the port channels of the PI/T modules can serve as I/O channels, interrupt requests or acknowledge signals.

# I/O Data Transfer Description

The VMIVME-2511 performs I/O transfers via connectors P3 and P4, which are accessible from the front panel of the board. The I/O transfers are done through the port registers in the desired PI/T module. While reading this section, please refer to logic diagram 141-022511-000 and the MC68230 specification. The VMIVME-2511 supports all of the data I/O modes in the PI/T modules, while providing a data buffer to the external host equipment if the high current option is not ordered.

To perform bi-directional operations, the two general purpose I/O pins of Port C (PC0 and PC1) are used. They must be programmed for output only operations. They are used to control the direction of the Ports A and B data buffers. PC0 controls Port A and PC1 controls Port B. To perform a data transfer set the level of the appropriate Port C line and then process the data. A low level on one of these Port C lines will place the associated data buffer in the output mode. A high level on the Port C line will put the data buffer in the input mode.

These operations require jumpering. Please refer to Figure 3-3 on page 61 and Figure 3-4 on page 62, as well as Table 3-1 on page 63, while reading this paragraph. The jumpers involved are J22, J23, J26, J27, J30, J31 and J34 through J43. If the Port C lines of PI/T No. 1 are to control its data buffers, then jumpers J40 and J41 are installed while J22, J23, J30, J31, J36 and J37 are NOT installed. These last jumpers are used when the Port C lines are used as general purpose I/O lines. The remaining jumpers are used with PI/T No. 2. Thus, PI/T No. 1 can be configured differently from PI/T No. 2.

For uni-directional operations, the buffers can be preset for input or output by installing or not installing jumpers J36 through J39. If these jumpers are installed, the associated port pins are outputs only. If these jumpers AND jumpers J40 through J43 are NOT installed, the associated port pins are inputs only. In either of these modes, the Port C pins "zero" and "one" are available for the types of tasks stated in the MC68230 specification.

Regardless of the type of operation stated above, the rest of the Port C pins can be used as stated in the MC68230's specification. However, these lines have jumper options that must be observed. These options are defined in Chapter 3, "Configuration and Installation".

**NOTE:** See "Description and Specifications" on page 22 and "Motorola MC68153 BIM and MC68230 PI/T" on page 23 for information on obtaining the MC68230 specification.

31

# **Interrupt Capability**

The VMIVME-2511 is capable of handling four interrupt requests. Each PI/T module is capable of two requests (a port interrupt request and a timer interrupt request). The four interrupt request signals (two from PI/T No. 1 and two from PI/T No. 2) are connected to the MC68153 BIM, giving full interrupt support for both PI/T modules. Each PI/T module has two on-board interrupt vector registers programmable by the user. Programming information concerning the BIM and PI/T modules will be found in the programming section that follows, and in the MC68153 specification.

**NOTE:** See "Description and Specifications" on page 22 and "Motorola MC68153 BIM and MC68230 PI/T" on page 23 for information on obtaining the MC68153 specification.

### The MC68230 Parallel Interface/Timer

The MC68230 PI/T provides a versatile parallel I/O interface to a wide variety of peripheral and computer systems. Each 8-bit port is double buffered and each port (Ports A and B) has two handshake lines to provide for orderly transfer of data to and from the MC68230. See the MC68230 specification for the port control structure, handshaking definition and I/O interface timing diagrams. Port C of each MC68230 may be used as six general purpose I/O lines (C0, C1, C4-C7) with C2 and C3 used as the timer clock input and timer clock output, respectively. Alternatively, Port C (C4-C7) may be programmed to support the MC68230's interrupt structure. C2 and C3 remain the timer input/output pins, and C0 and C1 stay as general purpose I/O pins.

The MC68230 may indicate a need for service in one of two ways. The processor may poll the Port Status Register (PSR) to check the state of the handshake pins or the MC68230 may be programmed for interrupts. These interrupts may occur on the assertion of any of the handshake pins, H1 and H2 for port A or H3 and H4 for Port B or at the end of a timer count. This is further explained in the MC68230 specification.

**NOTE:** See "Description and Specifications" on page 22 and "Motorola MC68153 BIM and MC68230 PI/T" on page 23 for information on obtaining the MC68230 specification.

# **Programming**

#### **Contents**

| BIM and PI/T Register Map | . 30 |

|---------------------------|------|

| Detailed Programming      | . 4  |

#### Introduction

The operation of the Parallel Interface/Timer (PI/T) module can be limited due to the buffers being used to drive port data to the P3 and P4 connectors. This limitation restricts the use of some port pins in some port modes, such as bi-directional data transfer. Before reading the next section the reader should have an understanding of the Programmers Model section of the MC68230 data specifications. Read "Theory of Operation" on page 25 and "Physical Installation" on page 55 so that the programming will be consistent with the jumper configuration of the I/O ports. For programming concerning interrupts, the reader should have an understanding of the BIM, which is described in the BIM and PI/T specifications (see "Description and Specifications" on page 22 and "Motorola MC68153 BIM and MC68230 PI/T" on page 23 for more information), to supplement the description which follows.

# **BIM and PI/T Register Map**

The Bus Interface Module, (BIM) MC68153 contains eight 8-bit registers, while each of the PI/T modules contain 32 eight-bit registers of which only 23 are used. All of the registers are addressed on odd-byte locations only. Of the 15 address bits A1-A15, only eight (A15-A8) are decoded for board select with the BIM mapped first RI/T1 second and PI/T2 last. The BIM register map is shown in Table 2-2 on page 37. The PI/T No. 1 register map is shown in Table 2-3 on page 38. The PI/T No. 2 register map is shown in Table 2-4 on page 42. The bit definitions of each register in the MC68153 BIM and the MC68230 PI/T will be found in the specifications for these parts. See "Description and Specifications" on page 22 and "Motorola MC68153 BIM and MC68230 PI/T" on page 23 for more information.

Table 2-1

PI/T No. 1 (P3 Connector Byte Address Locations)

| Binary Ad                            | dress |                     |       |    |                               |

|--------------------------------------|-------|---------------------|-------|----|-------------------------------|

| A15                                  | A8    | A7                  |       | A0 |                               |

| XXXXX                                | XXX   | 0 1 0 0             | 0 0 0 | 1  | Port General Control Register |

| Base Switch                          |       | Individual Register |       |    | <b>A</b>                      |

| Switch Selectal                      | ble   | Addresses           |       |    | <b>\</b>                      |

| XXXXXX                               | XXX   | 0 1 1 1             | 1 1 1 | 1  | Timer Status Register         |

| Hex Add                              | ress  |                     |       |    |                               |

| \$XX41 through \$XX47 for PI/T No. 1 |       |                     |       |    |                               |

Table 2-2 BIM Register Map

|          |    | Bina | ry A | ddre | SS |    |            |                    |        |        |        |          |            |        |        |        |

|----------|----|------|------|------|----|----|------------|--------------------|--------|--------|--------|----------|------------|--------|--------|--------|

| A15 - A8 | Α7 | A6   | A5   | A4   | А3 | A2 | <b>A</b> 1 | A0                 |        |        |        |          |            |        |        |        |

|          |    |      |      |      |    |    |            |                    |        |        |        | Control  | Register   | 0      |        |        |

| Y Y      | 0  | 0    | X    | X    | 0  | 0  | 0          | 1                  | IDB 07 | IDB 06 | IDB 05 | IDB 04   | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |                    | F      | FAC    | X/IN   | IRE      | IRAC       | L2     | L1     | L0     |

|          |    |      |      |      |    |    |            |                    |        |        |        | Control  | Register   | 1      |        |        |

| Y Y      | 0  | 0    | X    | X    | 0  | 0  | 1          | 1                  | IDB 07 | IDB 06 | IDB 05 | IDB 04   | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |                    | F      | FAC    | X/ĪN   | IRE      | IRAC       | L2     | L1     | L0     |

|          |    |      |      |      |    |    |            |                    |        |        |        | Control  | Register   | 2      |        |        |

| Y Y      | 0  | 0    | X    | X    | 0  | 1  | 0          | 1                  | IDB 07 | IDB 06 | IDB 05 | IDB 04   | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |                    | F      | FAC    | X/IN   | IRE      | IRAC       | L2     | L1     | L0     |

|          |    |      |      |      |    |    |            | Control Register 3 |        |        |        |          |            |        |        |        |

| Y Y      | 0  | 0    | X    | X    | 0  | 1  | 1          | 1                  | IDB 07 | IDB 06 | IDB 05 | IDB 04   | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |                    | F      | FAC    | X/ĪN   | IRE      | IRAC       | L2     | L1     | L0     |

|          |    |      |      |      |    |    |            |                    |        |        |        | Vector F | Register ( | )      |        |        |

| Y Y      | 0  | 0    | X    | X    | 1  | 0  | 0          | 1                  | IDB 07 | IDB 06 | IDB 05 | IDB 04   | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |                    | V7     | V6     | V5     | V4       | V3         | V2     | V1     | V0     |

|          |    |      |      |      |    |    |            |                    |        |        |        | Vector F | Register 1 | I      |        |        |

| Y Y      | 0  | 0    | X    | X    | 1  | 0  | 1          | 1                  | IDB 07 | IDB 06 | IDB 05 | IDB 04   | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |                    | V7     | V6     | V5     | V4       | V3         | V2     | V1     | V0     |

|          |    |      |      |      |    |    |            |                    |        |        |        | Vector F | Register 2 | 2      |        |        |

| Y Y      | 0  | 0    | X    | X    | 1  | 1  | 0          | 1                  | IDB 07 | IDB 06 | IDB 05 | IDB 04   | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |                    | V7     | V6     | V5     | V4       | V3         | V2     | V1     | V0     |

|          |    |      |      |      |    |    |            |                    |        |        |        | Vector F | Register 3 | 3      |        |        |

| Y Y      | 0  | 0    | X    | X    | 1  | 1  | 1          | 1                  | IDB 07 | IDB 06 | IDB 05 | IDB 04   | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |                    | V7     | V6     | V5     | V4       | V3         | V2     | V1     | V0     |

$\Upsilon$  - Represents user switch selectable positions. See DIP switch selection for address selection.

F - Flag Bit IRE - Interrupt Enable

FAC - Flag Auto Clear IRAC - Interrupt Auto-Clear

$X/\overline{IN}$  - External/ $\overline{Internal}$  (Vector Source) L2, L1 and L0 - Interrupt Level

Table 2-3 PI/T No.1 Register Map

|          |    | Bina | ry A | ddre | SS |    |            |    |                                |        |               |               |             |                   |                            |             |

|----------|----|------|------|------|----|----|------------|----|--------------------------------|--------|---------------|---------------|-------------|-------------------|----------------------------|-------------|

| A15 - A8 | Α7 | A6   | A5   | A4   | А3 | A2 | <b>A</b> 1 | A0 |                                |        |               |               |             |                   |                            |             |

|          |    |      |      |      |    |    |            |    |                                |        | Port          | General (     | Control R   | egister           |                            |             |

| X X      | 0  | 1    | 0    | 0    | 0  | 0  | 0          | 1  | IDB 07                         | IDB 06 | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |    | Port N<br>Con                  |        | H34<br>Enable | H12<br>Enable | H4<br>Sense | H3<br>Sense       | H2<br>Sense                | H1<br>Sense |

|          |    |      |      |      |    |    |            |    |                                |        | Port          | Service R     | equest R    | egister           |                            |             |

| x x      | 0  | 1    | 0    | 0    | 0  | 0  | 1          | 1  | IDB 07                         | IDB 06 | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |    | *                              |        | CRQ<br>lect   |               | rupt<br>FS  |                   | ort Interru<br>iority Cont |             |

|          |    |      |      |      |    |    |            |    | Port A Data Direction Register |        |               |               |             |                   |                            |             |

| X X      | 0  | 1    | 0    | 0    | 0  | 1  | 0          | 1  | IDB 07                         | IDB 06 | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |    | Bit 7                          | Bit 6  | Bit 5         | Bit 4         | Bit 3       | Bit 2             | Bit 1                      | Bit 0       |

|          |    |      |      |      |    |    |            |    |                                |        | Port l        | B Data Di     | rection R   | egister           |                            |             |

| X X      | 0  | 1    | 0    | 0    | 0  | 1  | 1          | 1  | IDB 07                         | IDB 06 | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |    | Bit 7                          | Bit 6  | Bit 5         | Bit 4         | Bit 3       | Bit 2             | Bit 1                      | Bit 0       |

|          |    |      |      |      |    |    |            |    |                                |        | Port (        | C Data Di     | rection R   | egister           |                            |             |

| X X      | 0  | 1    | 0    | 0    | 1  | 0  | 0          | 1  | IDB 07                         | IDB 06 | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |    | Bit 7                          | Bit 6  | Bit 5         | Bit 4         | Bit 3       | Bit 2             | Bit 1                      | Bit 0       |

|          |    |      |      |      |    |    |            |    |                                |        | Port          | Interrupt     | Vector R    | egister           |                            |             |

| X X      | 0  | 1    | 0    | 0    | 1  | 0  | 1          | 1  | IDB 07                         | IDB 06 | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |    |                                | Int    |               | ctor Num      |             |                   | *                          | *           |

|          |    |      |      |      |    |    |            |    |                                | T      | Po            | ort A Con     | trol Regi   | ster              | T                          | ı           |

| X X      | 0  | 1    | 0    | 0    | 1  | 1  | 0          | 1  | IDB 07                         | IDB 06 | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |    | Port A Si                      | ubmode | ]             | H2 Contro     | ol          | H2 INT.<br>Enable | H1<br>SVCRQ                | H1<br>STCTL |

|          |    |      |      |      |    |    |            |    | Port B Control Register        |        |               |               |             |                   |                            |             |

| X X      | 0  | 1    | 0    | 0    | 1  | 1  | 1          | 1  | IDB 07                         | IDB 06 | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |    | Port B Su                      | ıbmode | ]             | H4 Contro     | ol .        | H4 INT.<br>Enable | H3<br>SVCRQ                | H3<br>STCTL |

<sup>\*</sup>Unused, read zero (0).

$\boldsymbol{X}\boldsymbol{X}$  - Represents user selectable positions. See DIP switch selection for address selection.

$\label{NOTE:equiv} \textbf{NOTE:} See \ MC68230 \ Specifications for port control \ register \ information.$

Table 2-3 PI/T No.1 Register Map (Continued)

|          |    | Bina | ry A | ddre | ss |    |            |    |             |             |             |             |            |        |        |        |

|----------|----|------|------|------|----|----|------------|----|-------------|-------------|-------------|-------------|------------|--------|--------|--------|

| A15 - A8 | Α7 | A6   | A5   | A4   | А3 | A2 | <b>A</b> 1 | A0 |             |             |             |             |            |        |        |        |

|          |    |      |      |      |    |    |            |    |             |             | I           | Port A Da   | ıta Regist | ter    |        |        |

| X X      | 0  | 1    | 0    | 1    | 0  | 0  | 0          | 1  | IDB 07      | IDB 06      | IDB 05      | IDB 04      | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |    | Bit 7       | Bit 6       | Bit 5       | Bit 4       | Bit 3      | Bit 2  | Bit 1  | Bit 0  |

|          |    |      |      |      |    |    |            |    |             |             | ļ           | Port B Da   | ıta Regist | ter    |        |        |

| X X      | 0  | 1    | 0    | 1    | 0  | 0  | 1          | 1  | IDB 07      | IDB 06      | IDB 05      | IDB 04      | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |    | Bit 7       | Bit 6       | Bit 5       | Bit 4       | Bit 3      | Bit 2  | Bit 1  | Bit 0  |

|          |    |      |      |      |    |    |            |    |             |             | Ро          | rt A Alter  | nate Reg   | ister  |        |        |

| X X      | 0  | 1    | 0    | 1    | 0  | 1  | 0          | 1  | IDB 07      | IDB 06      | IDB 05      | IDB 04      | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |    | Bit 7       | Bit 6       | Bit 5       | Bit 4       | Bit 3      | Bit 2  | Bit 1  | Bit 0  |

|          |    |      |      |      |    |    |            |    |             |             | Ро          | rt B Alter  | nate Reg   | ister  |        |        |

| X X      | 0  | 1    | 0    | 1    | 0  | 1  | 1          | 1  | IDB 07      | IDB 06      | IDB 05      | IDB 04      | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |    | Bit 7       | Bit 6       | Bit 5       | Bit 4       | Bit 3      | Bit 2  | Bit 1  | Bit 0  |

|          |    |      |      |      |    |    |            |    |             |             | ļ           | Port C Da   | ıta Regist | ter    |        |        |

| X X      | 0  | 1    | 0    | 1    | 1  | 0  | 0          | 1  | IDB 07      | IDB 06      | IDB 05      | IDB 04      | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |    | Bit 7       | Bit 6       | Bit 5       | Bit 4       | Bit 3      | Bit 2  | Bit 1  | Bit 0  |

|          |    |      |      |      |    |    |            |    |             |             |             | Port State  | us Regist  | er     |        |        |

| X X      | 0  | 1    | 0    | 1    | 1  | 0  | 1          | 1  | IDB 07      | IDB 06      | IDB 05      | IDB 04      | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |    | H4<br>Level | H3<br>Level | H2<br>Level | H1<br>Level | H4S        | H3S    | H2S    | H1S    |

|          |    |      |      |      |    |    |            |    | Level       | Level       | Level       |             | Used       |        |        |        |

| X X      | 0  | 1    | 0    | 1    | 1  | 1  | 0          | 1  | IDB 07      | IDB 06      | IDB 05      | IDB 04      | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      | _    | _  | _  |            |    |             |             |             |             |            |        |        |        |

|          |    |      |      |      |    |    |            |    |             |             |             | Not         | Used       |        |        |        |

| x x      | 0  | 1    | 0    | 0    | 1  | 1  | 1          | 1  | IDB 07      | IDB 06      | IDB 05      | IDB 04      | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|          |    |      |      |      |    |    |            |    |             |             |             |             |            |        |        |        |

${\bf XX}$  - Represents user selectable positions. See DIP switch selection for address selection.

Table 2-3 PI/T No.1 Register Map (Continued)

|     |     |   |    | Bina | ry A | ddre | ss |    |    |                                                                     |        |                    |        |            |            |          |              |                 |

|-----|-----|---|----|------|------|------|----|----|----|---------------------------------------------------------------------|--------|--------------------|--------|------------|------------|----------|--------------|-----------------|

| A15 | - A | 8 | Α7 | A6   | A5   | A4   | А3 | A2 | A1 | A0                                                                  |        |                    |        |            |            |          |              |                 |

|     |     |   |    |      |      |      |    |    |    |                                                                     |        |                    | Ti     | imer Con   | trol Regis | ster     |              |                 |

| Χ   | X   |   | 0  | 1    | 1    | 0    | 0  | 0  | 0  | 1                                                                   | IDB 07 | IDB 06             | IDB 05 | IDB 04     | IDB 03     | IDB 02   | IDB 01       | IDB 00          |

|     |     |   |    |      |      |      |    |    |    |                                                                     |        | UT/TIAC<br>Control | CK     | ZD<br>CTRL | *          |          | ock<br>ntrol | Timer<br>Enable |

|     |     |   |    |      |      |      |    |    |    |                                                                     |        |                    | Timer  | Interrup   | t Vector F | Register |              |                 |

| Χ   | X   |   | 0  | 1    | 1    | 0    | 0  | 0  | 1  | 1                                                                   | IDB 07 | IDB 06             | IDB 05 | IDB 04     | IDB 03     | IDB 02   | IDB 01       | IDB 00          |

|     |     |   |    |      |      |      |    |    |    |                                                                     | Bit 7  | Bit 6              | Bit 5  | Bit 4      | Bit 3      | Bit 2    | Bit 1        | Bit 0           |

|     |     |   |    |      |      |      |    |    |    | Not Used  1 IDB 07 IDB 06 IDB 05 IDB 04 IDB 03 IDB 02 IDB 01 IDB 00 |        |                    |        |            |            |          |              |                 |

| Χ   | X   |   | 0  | 1    | 1    | 0    | 0  | 1  | 0  | 1                                                                   | IDB 07 | IDB 06             | IDB 05 | IDB 04     | IDB 03     | IDB 02   | IDB 01       | IDB 00          |

|     |     |   |    |      |      |      |    |    |    |                                                                     |        |                    |        |            |            |          |              |                 |

|     |     |   |    |      |      |      |    |    |    |                                                                     |        |                    | Cour   | nter Prelo | ad Regis   | ter (HI) |              |                 |

| Χ   | X   |   | 0  | 1    | 1    | 0    | 0  | 1  | 1  | 1                                                                   | IDB 07 | IDB 06             | IDB 05 | IDB 04     | IDB 03     | IDB 02   | IDB 01       | IDB 00          |

|     |     |   |    |      |      |      |    |    |    |                                                                     | Bit 23 | Bit 22             | Bit 21 | Bit 20     | Bit 19     | Bit 18   | Bit 17       | Bit 16          |

|     |     |   |    |      |      |      |    |    |    |                                                                     |        |                    | Count  | ter Preloa | d Regist   | er (MID) |              |                 |

| Χ   | X   |   | 0  | 1    | 1    | 0    | 1  | 0  | 0  | 1                                                                   | IDB 07 | IDB 06             | IDB 05 | IDB 04     | IDB 03     | IDB 02   | IDB 01       | IDB 00          |

|     |     |   |    |      |      |      |    |    |    |                                                                     | Bit 15 | Bit 14             | Bit 13 | Bit 12     | Bit 11     | Bit 10   | Bit 09       | Bit 08          |

|     |     |   |    |      |      |      |    |    |    |                                                                     |        |                    | Count  | er Preloa  | d Registe  | er (LOW) |              |                 |

| Χ   | X   |   | 0  | 1    | 1    | 0    | 1  | 0  | 1  | 1                                                                   | IDB 07 | IDB 06             | IDB 05 | IDB 04     | IDB 03     | IDB 02   | IDB 01       | IDB 00          |

|     |     |   |    |      |      |      |    |    |    |                                                                     | Bit 07 | Bit 06             | Bit 05 | Bit 04     | Bit 03     | Bit 02   | Bit 01       | Bit 0           |

|     |     |   |    |      |      |      |    |    |    |                                                                     |        |                    |        | Not        | Used       |          |              |                 |

| Χ   | X   |   | 0  | 1    | 1    | 0    | 1  | 1  | 0  | 1                                                                   | IDB 07 | IDB 06             | IDB 05 | IDB 04     | IDB 03     | IDB 02   | IDB 01       | IDB 00          |

|     |     |   |    |      |      |      |    |    |    |                                                                     |        |                    |        |            |            |          |              |                 |

|     |     |   |    |      |      |      |    |    |    |                                                                     |        |                    | Co     | ounter Re  | egister (H | igh)     |              |                 |

| Χ   | X   |   | 0  | 1    | 1    | 0    | 1  | 1  | 1  | 1                                                                   | IDB 07 | IDB 06             | IDB 05 | IDB 04     | IDB 03     | IDB 02   | IDB 01       | IDB 00          |

|     |     |   |    |      |      |      |    |    |    |                                                                     | Bit 23 | Bit 22             | Bit 21 | Bit 20     | Bit 19     | Bit 18   | Bit 17       | Bit 16          |

<sup>\*</sup>Unused, read as zero (0).

$\boldsymbol{X}\boldsymbol{X}$  - Represents user selectable positions. See DIP switch selection for address selections.

Table 2-3 PI/T No.1 Register Map (Concluded)

|     |      |    | Bina | ry A | ddre | ss |    |            |    |        |        |        |           |            |        |        |        |

|-----|------|----|------|------|------|----|----|------------|----|--------|--------|--------|-----------|------------|--------|--------|--------|

| A15 | - A8 | Α7 | A6   | A5   | A4   | А3 | A2 | <b>A</b> 1 | A0 |        |        |        |           |            |        |        |        |

|     |      |    |      |      |      |    |    |            | ,  |        |        | С      | ounter R  | egister (N | IID)   |        |        |

| Χ   | X    | 0  | 1    | 1    | 1    | 0  | 0  | 0          | 1  | IDB 07 | IDB 06 | IDB 05 | IDB 04    | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|     |      |    |      |      |      |    |    |            |    | Bit 15 | Bit 14 | Bit 13 | Bit 12    | Bit 11     | Bit 10 | Bit 09 | Bit 08 |

|     |      |    |      |      |      |    |    |            |    |        |        | C      | ounter Re | egister (L | ow)    |        |        |

| Χ   | X    | 0  | 1    | 1    | 1    | 0  | 0  | 1          | 1  | IDB 07 | IDB 06 | IDB 05 | IDB 04    | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|     |      |    |      |      |      |    |    |            |    | Bit 07 | Bit 06 | Bit 05 | Bit 04    | Bit 03     | Bit 02 | Bit 01 | Bit 0  |

|     |      |    |      |      |      |    |    |            |    |        |        | T      | imer Sta  | tus Regis  | ter    |        |        |

| Χ   | X    | 0  | 1    | 1    | 1    | 0  | 1  | 0          | 1  | IDB 07 | IDB 06 | IDB 05 | IDB 04    | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|     |      |    |      |      |      |    |    |            |    | *      | *      | *      | *         | *          | *      | *      | ZDS    |

|     |      |    |      |      |      |    |    |            |    |        |        |        | Not       | Used       |        |        |        |

| Χ   | X    | 0  | 1    | 1    | 1    | 0  | 1  | 1          | 1  | IDB 07 | IDB 06 | IDB 05 | IDB 04    | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|     |      |    |      |      |      |    |    |            |    |        |        |        |           |            |        |        |        |

|     |      |    |      |      |      |    |    |            |    |        |        |        | Not       | Used       |        |        |        |

| X   | X    | 0  | 1    | 1    | 1    | 1  | 0  | 0          | 1  | IDB 07 | IDB 06 | IDB 05 | IDB 04    | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|     |      |    |      |      |      |    |    |            |    |        |        |        |           |            |        |        |        |

|     |      |    |      |      |      |    |    |            |    |        |        |        | Not       | Used       |        |        |        |

| Χ   | X    | 0  | 1    | 1    | 1    | 1  | 0  | 1          | 1  | IDB 07 | IDB 06 | IDB 05 | IDB 04    | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|     |      |    |      |      |      |    |    |            |    |        |        |        |           |            |        |        |        |

|     |      |    |      |      |      |    |    |            |    |        |        |        | Not       | Used       |        |        |        |

| Χ   | X    | 0  | 1    | 1    | 1    | 1  | 1  | 0          | 1  | IDB 07 | IDB 06 | IDB 05 | IDB 04    | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|     |      |    |      |      |      |    |    |            |    |        |        |        |           |            |        |        |        |

|     |      |    |      |      |      |    |    |            |    |        |        |        | Not       | Used       |        |        |        |

| Χ   | X    | 0  | 1    | 1    | 1    | 1  | 1  | 1          | 1  | IDB 07 | IDB 06 | IDB 05 | IDB 04    | IDB 03     | IDB 02 | IDB 01 | IDB 00 |

|     |      |    |      |      |      |    |    |            |    |        |        |        |           |            |        |        |        |

<sup>\*</sup>Unused, read as zero (0).

$<sup>\</sup>boldsymbol{X}\boldsymbol{X}$  - Represents user selectable positions. See DIP switch selection for address selections.

Table 2-4 PI/T No.2 Register Map

|          |    | Bina | ry A | ddre | SS |    |            |                                                                                           |               |            |               |               |             |                   |                            |             |

|----------|----|------|------|------|----|----|------------|-------------------------------------------------------------------------------------------|---------------|------------|---------------|---------------|-------------|-------------------|----------------------------|-------------|

| A15 - A8 | Α7 | A6   | A5   | A4   | А3 | A2 | <b>A</b> 1 | A0                                                                                        |               |            |               |               |             |                   |                            |             |

|          |    |      |      |      |    |    |            |                                                                                           |               |            | Port          | General (     | Control R   | egister           |                            |             |

| X X      | 1  | 0    | 0    | 0    | 0  | 0  | 0          | 1                                                                                         | IDB 07        | IDB 06     | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |                                                                                           | Port N<br>Con |            | H34<br>Enable | H12<br>Enable | H4<br>Sense | H3<br>Sense       | H2<br>Sense                | H1<br>Sense |

|          |    |      |      |      |    |    |            |                                                                                           |               |            | Port          | Service R     | equest R    | egister           |                            |             |

| X X      | 1  | 0    | 0    | 0    | 0  | 0  | 1          | 1                                                                                         | IDB 07        | IDB 06     | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |                                                                                           | *             | SVC<br>Sel | CRQ<br>ect    |               | rrupt<br>FS |                   | ort Interru<br>iority Cont |             |

|          |    |      |      |      |    |    |            | Port A Data Direction Register  1 IDB 07 IDB 06 IDB 05 IDB 04 IDB 03 IDB 02 IDB 01 IDB 00 |               |            |               |               |             |                   |                            |             |

| X X      | 1  | 0    | 0    | 0    | 0  | 1  | 0          | 1                                                                                         | IDB 07        | IDB 05     | IDB 04        | IDB 03        | IDB 02      | IDB 01            | IDB 00                     |             |

|          |    |      |      |      |    |    |            |                                                                                           | Bit 7         | Bit 6      | Bit 5         | Bit 3         | Bit 2       | Bit 1             | Bit 0                      |             |

|          |    |      |      |      |    |    |            |                                                                                           |               |            | Port I        | B Data Di     | rection R   | egister           |                            |             |

| X X      | 1  | 0    | 0    | 0    | 0  | 1  | 1          | 1                                                                                         | IDB 07        | IDB 06     | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |                                                                                           | Bit 7         | Bit 6      | Bit 5         | Bit 4         | Bit 3       | Bit 2             | Bit 1                      | Bit 0       |

|          |    |      |      |      |    |    |            |                                                                                           |               |            | Port (        | C Data Di     | rection R   | egister           |                            |             |

| X X      | 1  | 0    | 0    | 0    | 1  | 0  | 0          | 1                                                                                         | IDB 07        | IDB 06     | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |                                                                                           | Bit 7         | Bit 6      | Bit 5         | Bit 4         | Bit 3       | Bit 2             | Bit 1                      | Bit 0       |

|          |    |      |      |      |    |    |            |                                                                                           |               |            | Port          | Interrupt     | Vector R    | egister           |                            |             |

| X X      | 1  | 0    | 0    | 0    | 1  | 0  | 1          | 1                                                                                         | IDB 07        | IDB 06     | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |                                                                                           |               | Int        |               | ctor Num      |             |                   | *                          | *           |

|          |    |      |      |      |    |    |            |                                                                                           |               | 1          | Po            | ort A Con     | trol Regi   | ster              | r                          | r           |

| X X      | 1  | 0    | 0    | 0    | 1  | 1  | 0          | 1                                                                                         | IDB 07        | IDB 06     | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |                                                                                           | Port A Si     | ubmode     | I             | H2 Contro     | ol          | H2 INT.<br>Enable | H1<br>SVCRQ                | H1<br>STCTL |

|          |    |      |      |      |    |    |            |                                                                                           |               |            | Po            | ort B Con     | trol Regi   | ster              |                            |             |

| X X      | 1  | 0    | 0    | 0    | 1  | 1  | 1          | 1                                                                                         | IDB 07        | IDB 06     | IDB 05        | IDB 04        | IDB 03      | IDB 02            | IDB 01                     | IDB 00      |

|          |    |      |      |      |    |    |            |                                                                                           | Port B Su     | ıbmode     | I             | H4 Contro     | ol          | H4 INT.<br>Enable | H3<br>SVCRQ                | H3<br>STCTL |

<sup>\*</sup>Unused, read zero (0).

$\boldsymbol{X}\boldsymbol{X}$  - Represents user selectable positions. See DIP switch selection for address selection.

Table 2-4 PI/T No.2 Register Map (Continued)

|     |   |     |    | Bina | ry A | ddre | SS |    |            |    |             |             |             |             |            |        |        |        |

|-----|---|-----|----|------|------|------|----|----|------------|----|-------------|-------------|-------------|-------------|------------|--------|--------|--------|

| A15 | - | A8  | Α7 | A6   | A5   | Α4   | А3 | A2 | <b>A</b> 1 | Α0 |             |             |             |             |            |        |        |        |

|     |   |     |    |      |      |      |    |    |            |    |             |             |             | Port A Da   | ıta Regist | ter    |        |        |