# VMIACC-0559 CompactPCI® Rear Transition Utility Board

## **INSTALLATION GUIDE**

12090 South Memorial Parkway Huntsville, Alabama 35803-3308, USA (256) 880-0444 ◆ (800) 322-3616 ◆ Fax: (256) 882-0859

12090 South Memorial Parkway Huntsville, Alabama 35803-3308, USA (256) 880-0444 ◆ (800) 322-3616 ◆ Fax: (256) 882-0859

#### COPYRIGHT AND TRADEMARKS

© Copyright March 1998. The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

AMXbus, BITMODULE, COSMODULE, DMAbus, Instant OPC wizard logo, IOWorks Access, IOWorks Foundation, IOWorks man figure, IOWorks Manager, IOWorks Server, MAGICWARE, MEGAMODULE, PLC ACCELERATIOR (ACCELERATION), Quick Link, RTnet, Soft Logic Link, SRTbus, TESTCAL, "The Next Generation PLC", The PLC Connection, TURBOMODULE, UCLIO, UIOD, UPLC, Visual Soft Logic Control(ler), VMEaccess, VMEmanager, VMEmonitor, VMEnet, VMEnet II, and VMEprobe are trademarks of VMIC.

(Instant OPC wizard logo)

(IOWorks man figure)

The I/O man figure, IOWorks, UIOC, Visual IOWorks, and WinUIOC are registered trademarks of VMIC.

ActiveX is a trademark and Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, Windows NT, and XENIX are registered trademarks of Microsoft Corporation.

MMX is a trademark and Pentium is a registered trademark of Intel Corporation.

Other registered trademarks are the property of their respective owners.

#### **VMIC**

#### All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless granted express written permission from VMIC.

12090 South Memorial Parkway Huntsville, Alabama 35803-3308, USA (256) 880-0444 ◆ (800) 322-3616 ◆ Fax: (256) 882-0859

# INSTALLATION

#### Contents

| I | nstallation of the VMIACC-0559                             |

|---|------------------------------------------------------------|

| ( | Connectors                                                 |

|   | 40-pin IDE Header (E3)                                     |

|   | 34-pin Floppy Drive Header (E4)9                           |

|   | Jumpers E5 and E6 (Ring Indicator and Data Carrier Detect) |

|   | J3 Connector Pinout                                        |

|   | COM1 (J6) and COM2 (J5) Connector Pinouts                  |

#### Introduction

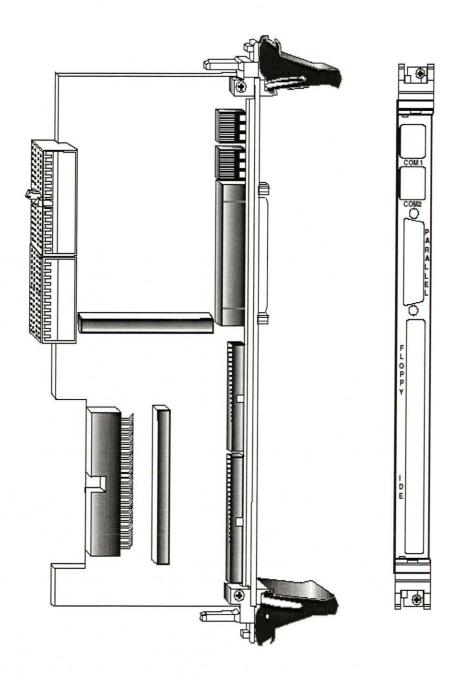

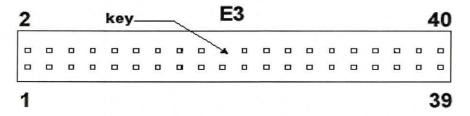

The VMIACC-0559 is a passive backplane adapter board designed to be used with VMIC's family of CPUs on CompactPCI® CPCI. The VMIACC-0559 provides IDE hard drive, floppy drive headers, two serial ports, and a parallel port for external connection to the CPU through the CPCI rear I/O. The adapter board uses a standard 40-pin header for the hard drive connector, and a 34-pin header for the floppy drive connector. The serial ports are RJ45 connectors, and the parallel port is the standard DB25 pin connector. See Figure 1 on page 6 for an illustration of the board and connector layout.

The CPCI J3 connector carries all associated signals from the 6U front installed CPU through the backplane to the VMIACC-0559 J3 connector. See Figure 1 on page 6 for an illustration of the board and connector layout. Figure 2 on page 7 is an illustration of the VMIACC-0559 installed in the CPCI rear I/O.

The following is a list of compatible boards:

VMICPCI-7593

VMICPCI-7594

Figure 1 VMIACC-0559 CompactPCI Rear Transition Utility Board

#### Installation of the VMIACC-0559

The VMIACC-0559 adapter board installs onto the rear I/O of the CompactPCI chassis using the J3 and J4 connectors. The board is designed for installation in CPCI chassis that have rear panel I/O connectors. See Figure 2 for an illustration of the installation. J4 on the VMIACC-0559 is used for keying purposes only, and is not electrically connected to the CPU board in the front of the chassis.

Figure 2 Installation of the VMIACC-0559 Adapter Board with a Typical CPU Board

The VMIACC-0559 adapter board is designed to be installed on backplanes with rear I/O connectors, backplanes without the rear I/O cannot be used.

#### Connectors

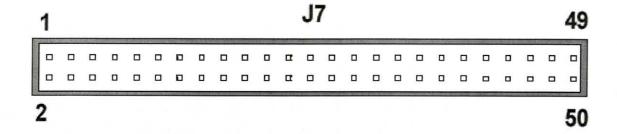

There are eight connectors and two headers on the utility board. J3 and J4 connectors are standard CPCI connectors. E4 is the 34-pin floppy drive header, and E3 is the 40-pin IDE hard drive header. There are two RJ-45 connectors on the front panel that are used for COM1 and COM2 serial ports. The front panel parallel port is a standard DB25 connector. P5 is the front panel floppy drive connector, and P6 is the front panel IDE hard drive connector. J7 the 50-pin connector on the board, is used for *future expansion*. Each connector along with its pinout is shown on the following pages.

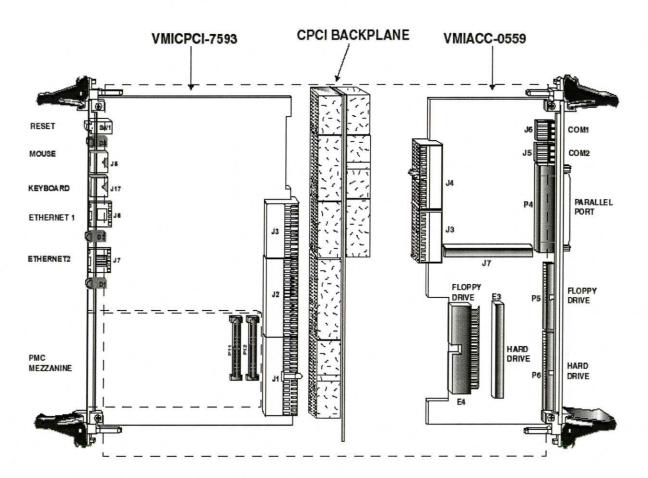

#### 40-pin IDE Header (E3)

Figure 3 E3 40-pin IDE Header

Table 1 E3 40-pin IDE Header Pinout

| Pin | Signal                 | Pin | Signal                  |

|-----|------------------------|-----|-------------------------|

| 1   | Reset Drive            | 2   | Signal Ground           |

| 3   | Bidirectional Data [7] | 4   | Bidirectional Data [8]  |

| 5   | Bidirectional Data [6] | 6   | Bidirectional Data [9]  |

| 7   | Bidirectional Data [5] | 8   | Bidirectional Data [10] |

| 9   | Bidirectional Data [4] | 10  | Bidirectional Data [11] |

| 11  | Bidirectional Data [3] | 12  | Bidirectional Data [12] |

| 13  | Bidirectional Data [2] | 14  | Bidirectional Data [13] |

| 15  | Bidirectional Data [1] | 16  | Bidirectional Data [14] |

| 17  | Bidirectional Data [0] | 18  | Bidirectional Data [15] |

| 19  | Signal Ground          | 20  | Key                     |

| 21  | Reserved               | 22  | Signal Ground           |

| 23  | Write Strobe           | 24  | Signal Ground           |

| 25  | Read Strobe            | 26  | Signal Ground           |

| 27  | Reserved               | 28  | Address Latch Enable    |

| 29  | Reserved               | 30  | Signal Ground           |

| 31  | Interrupt Request [14] | 32  | 16-bit Data Word Size   |

| 33  | Address Line [1]       | 34  | Diagnostic Test Passed  |

| 35  | Address Line [0]       | 36  | Address Line [2]        |

| 37  | Chip Select [0]        | 38  | Chip Select [1]         |

| 39  | Store/Activity Status  | 40  | Signal Ground           |

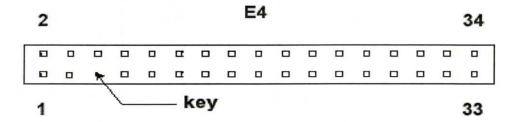

# 34-pin Floppy Drive Header (E4)

Figure 4 E4 34-pin Floppy Drive Header

Table 2 E4 34-pin Floppy Drive Pinout

| Pin | Signal | Pin | Signal                      |

|-----|--------|-----|-----------------------------|

| 1   | GND    | 2   | Drive Density 0             |

| 3   | GND    | 4   | N/C                         |

| 5   | Key    | 6   | Drive Density 1             |

| 7   | GND    | 8   | Index                       |

| 9   | GND    | 10  | Floppy Motor Enable [A]     |

| 11  | GND    | 12  | Floppy Drive Select [B]     |

| 13  | GND    | 14  | Floppy Drive Select [A]     |

| 15  | GND    | 16  | Floppy Motor Enable [B]     |

| 17  | GND    | 18  | Floppy Step Motor Direction |

| 19  | GND    | 20  | Floppy Step Pulse           |

| 21  | GND    | 22  | Floppy Write Data           |

| 23  | GND    | 24  | Floppy Write Enable         |

| 25  | GND    | 26  | Floppy Track [0]            |

| 27  | GND    | 28  | Floppy Write Protect        |

| 29  | GND    | 30  | Floppy Read Data            |

| 31  | GND    | 32  | Floppy Select Head [1]      |

| 33  | GND    | 34  | Floppy Disk Change          |

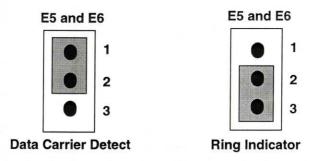

#### Jumpers E5 and E6 (Ring Indicator and Data Carrier Detect)

Jumpers E5 and E6 control the Ring Indicator and Data Carrier Detect signals for COM1 and COM2. E5 controls COM1, and E6 controls COM2. The following figure illustrates the jumper configuration for E5 and E6.

#### J4 Connector

Connector J4 is a standard CPCI connector with keying. Currently the connector is not electrically connected and is for keying and to support the board in the CPCI rear I/O.

Figure 5 J4 Connector

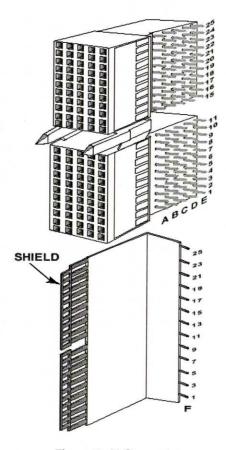

#### **J3 Connector Pinout**

The J3 connector is 19 rows of 5 pins each, 2 mm *Hard Metric* CPCI connector. An additional external metal shield is also used, labeled row F. This connector is used to route the serial, floppy, and hard drive signals to the rear I/O. The following figure illustrates the J3 connector; the table is the connector pinout.

TOTAL TOTAL STATE OF THE PARTY OF THE PARTY

Table 3 J3 Connector Pinout

| Pin<br>No. | Row A    | Row B    | Row C     | Row D    | Row E    | Row F |

|------------|----------|----------|-----------|----------|----------|-------|

| 19         | GND      | ACK#     | BUSY      | PE       | SLCT     | GND   |

| 18         | PD4      | PD5      | PD6       | PD7      | GND      | N/C   |

| 17         | PD1      | INIT#    | PD2       | SLIN#    | PD3      | GND   |

| 16         | N/C      | STB#     | AFD#      | PD0      | ERR#     | N/C   |

| 15         | N/C      | N/C      | N/C       | N/C      | N/C      | GND   |

| 14         | GND      | RI COM1  | DTR COM1  | DCD COM1 | TD COM1  | N/C   |

| 13         | RTS COM1 | RD COM1  | DSR COM1  | CTS COM1 | N/C      | GND   |

| 12         | RTS COM2 | N/C      | +5 V      | N/C      | +12 V    | N/C   |

| 11         | GND      | RI COM2  | DTR COM2  | CTS COM2 | TD COM2  | GND   |

| 10         | DAP0     | RD COM2  | DSR COM2  | DCD COM2 | DAP2PR   | N/C   |

| 9          | DAP1     | REDWC#   | IDEIORDY  | IDESELA  | IDEIOW0# | GND   |

| 8          | DIR#     | INDEX#   | IDECS01#  | DOP[8]   | DOP[6]   | N/C   |

| 7          | SIDE1#   | IDEIOR0# | HD_ACTA#  | DOP[9]   | DOP[7]   | GND   |

| 6          | RDATA#   | TRK0#    | IDECS03#  | DOP[10]  | DOP[2]   | N/C   |

| 5          | DRATE0#  | WDATA#   | IDEIRQ0   | DOP[11]  | DOP[3]   | GND   |

| 4          | DRVSB#   | STEP#    | IDE0ACK0# | DOP[12]  | DOP[4]   | N/C   |

| 3          | DSKCHG#  | MOTEB#   | IOCS16A#  | DOP[13]  | DOP[5]   | GND   |

| 2          | WPT#     | DRVSA#   | IDEDRQ0   | DOP[14]  | DOP[0]   | N/C   |

| 1          | WGATE#   | MOTEA#   | IDERST#   | DOP[15]  | DOP[1]   | GND   |

Figure 6 J3 Connector

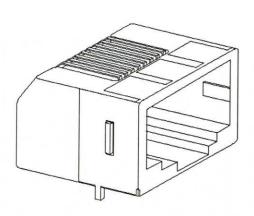

## COM1 (J6) and COM2 (J5) Connector Pinouts

The pinout and diagram for the two RJ-45 connectors that are used for COM1 and COM2 (serial ports) is shown in the following figure.

| RJ-45 CONNECTOR<br>(COM1 and COM2) |                                     |  |  |  |

|------------------------------------|-------------------------------------|--|--|--|

| PIN                                | Signal Name                         |  |  |  |

| 1                                  | *Data Carrier Detect/Ring Indicator |  |  |  |

| 2                                  | Clear to Send                       |  |  |  |

| 3                                  | Request to Send                     |  |  |  |

| 4                                  | Data Set Ready                      |  |  |  |

| 5                                  | Data Terminal Ready                 |  |  |  |

| 6                                  | Transmit Data                       |  |  |  |

| 7                                  | Receive Data                        |  |  |  |

| 8                                  | GND                                 |  |  |  |

Figure 7 COM1/COM2 Connector and Pinout

### 50-pin IDE Connector (E7)

This connector is currently not in use, and is for future expansion.

Figure 8 E7 50-pin IDE Connector

Table 4 E7 50-pin IDE Connector Pinout

| Pin      | Signal                     | Pin                | Signal              |

|----------|----------------------------|--------------------|---------------------|

| 2        | Vendor Specific (1)        | 1                  | Vendor Specific (1) |

| 4        | Vendor Specific (1)        | 3                  | Vendor Specific (1) |

| 6        | N/C (1)                    | 5                  | N/C (1)             |

| 8        | GND                        | 7                  | Reset-              |

| 10       | DD8                        | 9                  | DD7                 |

| 12       | DD9                        | 11                 | DD6                 |

| 14       | DD10                       | 13                 | DD5                 |

| 16       | DD11                       | 15                 | DD4                 |

| 18       | DD12                       | 17                 | DD3                 |

| 20       | DD13                       | 19                 | DD2                 |

| 22       | DD14                       | 21                 | DD1                 |

| 24       | DD15                       | 23                 | DD0                 |

| 26       | N/C                        | 25                 | GND                 |

| 28       | GND                        | 27                 | DMARQ               |

| 30       | GND                        | 29                 | DIOW-               |

| 32       | GND                        | 31                 | DIOR-               |

| 34       | CSEL                       | 33                 | DIORDY              |

| 36       | GND                        | 35                 | DMACK-              |

| 38       | Reserved                   | 37                 | INTRQ               |

| 40       | PDIAG-                     | 39                 | DA1                 |

| 42       | DA2                        | 41                 | DA0                 |

| 44       | CS1                        | 43                 | CS0-                |

| 46       | GND                        | 45                 | DASP-               |

| 48       | +5 V (Motor) (1)           | 47                 | +5 V (Logic) (1)    |

| 50       | TYPE- (0=ATA) (1)          | 49                 | GND (Return) (1)    |

| Note (1) | : Pins which are additiona | al to those of the | he 40-pin cable.    |

13

# Maintenance

#### Maintenance

This section provides information relative to the care and maintenance of VMIC's products. If the products malfunction, verify the following:

- Software

- · System configuration

- Electrical connections

- Jumper or configuration options

- Boards are fully inserted into their proper connector location

- Connector pins are clean and free from contamination

- No components of adjacent boards are disturbed when inserting or removing the board from the chassis

- Quality of cables and I/O connections

If products must be returned, contact VMIC for a Return Material Authorization (RMA) Number. **This RMA Number must be obtained prior to any return**.

# **Maintenance Prints**

User level repairs are not recommended. The drawings and diagrams in this manual are for reference purposes only.