# 24-Channel 16-bit PCI Analog-to-Digital Converter (ADC) Board

- · PCI local bus compliant

- 24 differential or single-ended inputs

- 16-bit A/D conversion

- Aggregate conversion rate 99.5 kHz

- · Program-selectable scanning of 8, 16, or 24 channels

- Sequentially digitizes selected channels and stores the results in RAM registers

- Jumper-selectable A/D ranges of 0 to +5 V, 0 to +10 V, ±2.5 V, ±5 V, and ±10 V

- · Optional low pass filters

- · Overvoltage protected inputs

- · Selectable output coding

- VMISFT-9450 software driver available for:

- Windows NT®

- VxWorks

- QNX

- Linux

#### **Applications**

- · Factory automation and instrumentation

- Process control

- · Laboratory instrumentation

- · Machine monitoring

- Data acquisition

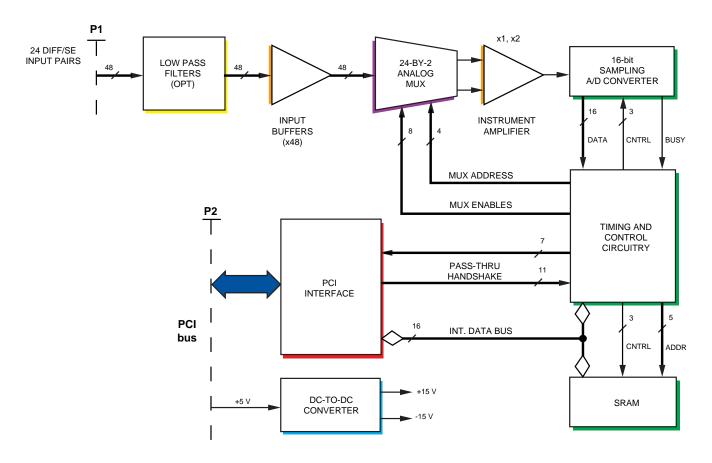

**INTRODUCTION** — The VMIPCI-3322 is designed to operate on the industrial standard 5 V PCI local bus and supports up to 24 channels of differential or single-ended inputs within the full-scale range of  $\pm 2.5$  V to  $\pm 10$  V. The board continuously scans the selected inputs, converts each sample to a digital value and stores the results in dual-port data registers. The number of channels scanned is program selectable between 8, 16, or 24. The output format is program selectable between straight/offset binary and two's complement.

The VMIPCI-3322 converts at an aggregate rate of 99.5 kHz. The channel sample rate is 99.5 kHz divided by the number of channels scanned.

A functional block diagram is provided in Figure 1 and the ordering information is provided on the first page of this document.

## **FUNCTIONAL CHARACTERISTICS**

(At +25 °C unless otherwise stated.)

**PCI Local Bus Compliance:** This product complies with the PCI Local Bus Specification, revision 2.1, for 5 V boards and for active PCI clock frequencies from 10 to 33 MHz

**Vendor Identification:** The PCI configuration register reserved for the Vendor Identification shall have the value 114A(HEX), which designates VMIC

**Device Identification:** The PCI configuration register reserved for the Device Identification shall have the

value 3322(HEX), which designates the VMIPCI-3322 board

Base Address Register 1: The PCI configuration register called Base Address Register 1 contains the starting address of a group of 128 I/O byte address are reserved for PCI bus access of the VMIPCI-3322 functions. The base address is dynamically specified by the system BIOS. The 128 I/O addresses access the 24 dual-port data registers, eight spare data registers, and a single Control and Status Register (CSR).

Control and Status Register (CSR): The CSR contains six control bits which control the following:

Fail/Status LED Software Reset Autoscan Enable

| Ordering Options               |   |   |   |   |   |   |   |   |

|--------------------------------|---|---|---|---|---|---|---|---|

| Dec. 16, 1999 800-853322-000 B |   | Α | В | С | _ | D | Е | F |

| VMIPCI-3322                    | _ |   |   | 0 | _ |   |   |   |

# A = Input Filter Option

0 = No Filter

1 = 50 Hz (-3 dB)

2 = 100 Hz (-3 dB) 3 = 500 Hz (-3 dB)

#### B = Input Option

0 = Differential Analog Inputs

1 = Single-Ended Analog Inputs

C = 0 (Option reserved for future use)

## Connector Data

The I/O connector of the VMIPCI-3322 is a 50-pin **D** subminiature receptacle of the type AMP 205870-1. There are several compatible cable plugs and backshells from several vendors. One compatible plug is the AMP 205212-2

For Ordering Information, Call: 1-800-322-3616 or 1-256-880-0444 • FAX (256) 882-0859 E-mail: info@vmic.com Web Address: www.vmic.com Copyright © August 1995 by VMIC Specifications subject to change without notice.

Output Data Format

Test bit

Selected Number of Channels Scanned (8, 16, 24)

When read back as status, the CSR echos back the states of the control bits and also includes an A/D calibration busy flag.

**Fail/Status LED:** The VMIPCI-3322 contains a Fail/Status LED located along the top edge of the board. The LED is only visible when the PC chassis cover is removed. The LED is controlled through a bit in the CSR.

**Output Data Format:** One control bit in the CSR selects the output data format between two's complement and offset binary

**Reset Operations:** A board reset occurs in response to a system reset or to a software reset. Immediately upon release of the reset, the A/D converter performs a self-calibration which takes 41 ms to complete. A reset also clears the CSR to zero so the LED will be on, autoscanning will be disabled, and the output data format is offset binary.

### **INPUT CHARACTERISTICS**

**Number of Input Channels:** 24 differential or single-ended channels

**Full-Scale A/D Ranges:**  $\pm 2.5$  V,  $\pm 5$  V,  $\pm 10$  V, 0 to +5 V, and 0 to +10 V, jumper-selectable

**Accuracy:** Maximum error =  $\pm 0.005$  percent Reading  $\pm 0.005$  percent Range  $\pm 100 \mu V$

**Stability:** Temperature drift, per  ${}^{\circ}C = TBD$

Input Noise:  $\left[0.6 + \frac{0.3}{G}\right]$  mVRMS

Input Bias Current: 40 nA maximum at zero input

Input Impedance:  $5 \ M\Omega$  minimum in parallel with  $50 \ pF$

Interchannel Crosstalk (DC to 1 kHz):

Adjacent Channel = 50 dB Alternate Channel = 90 dB

Common-Mode Voltage:  $[V_{CM} + (V_{DIFF}/2)] = \pm 12 \text{ V}$

**Common-Mode Rejection:** DC to 60 Hz with 350  $\Omega$  source imbalance

For the  $\pm 5$  V,  $\pm 10$  V, and 0 to +10 V ranges:

Minimum = 90 dB

Typical = 100 dB

For the  $\pm 2.5$  V and 0 to +5 V ranges:

Minimum = 75 dB Typical = 85 dB

Overvoltage Protection: ±35 V, sustained power On

or power Off

±80 V, transient (1 s maximum)

**Input Filters:** Optional low pass single-pole filters:

-3 dB at 50 Hz

-3 dB at 100 Hz

-3 dB at 500 Hz

The above values apply to differential inputs. The cutoff frequency doubles for single-ended inputs. The cutoff frequency has a tolerance of  $\pm 25$  percent.

The *no filter* maximum input frequency is the Nyquist limit:

2.073 kHz for 24 channels

3.109 kHz for 16 channels

6.219 kHz for 8 channels

Common-Mode/Floating Input Protection: All

inputs are referenced to the on-board analog ground through 22  $M\Omega$  resistors.

#### TRANSFER CHARACTERISTICS

Resolution: 16 bits

**Input Sampling:** Sequential, starting at channel 0

**Input Transfer Function:**

$E_{IN} = E_{LO} + [E_{FSR} \times (N_{ADC}/65,536)]$

Where:  $E_{IN}$  = Input Voltage

E<sub>LO</sub> = Lower End of Input Range E<sub>FSR</sub> = Full-Scale Input Range N<sub>ADC</sub> = A/D Converter Reading

Example: For a N<sub>ADC</sub> value of D99A HEX (55,706

decimal) in the ±10 V Range:

$E_{IN} = -10 + [20.000 \text{ x } (55,706/65,536)] = +7.000$

Integral Nonlinearity:  $\pm 0.005$  percent maximum from

best straight line

**Differential Nonlinearity:** ±0.0015 percent, no

missing codes at 16-bit resolution

A/D Conversion Rate: 99.5 kSPS

**Channel Sample Rate:** 99.5 ÷ 24 channels =

4.146 kSPS

99.5 ÷ 16 Channels = 6.219 kSPS 99.5 ÷ 8 Channels = 12.430 kSPS

Data Coding: Program selectable as two's complement

or straight/offset binary

# **DATA BUFFER MEMORY**

Buffer Size: 32 contiguous 16-bit data words

PCI bus Access Time: 270 ns typical (nonburst only)

## PHYSICAL/ENVIRONMENTAL

Temperature: 0 to 70 °C, operating

-40 to +85 °C, storage

Relative Humidity: 10 to 80 percent, noncondensing

**Altitude:** 0 to 10,000 feet, operating

**Cooling:** Forced air convection (standard PC slot)

**Dimensions:** 4.2-in. height x 9.4-in. length

(approximately 3/4 of full size)

**I/O Connector:** 50-pin D-subminiature receptacle

(AMP 205870-1)

Power: 2 A @ 5 VDC

**MTBF:** 179,953 hours (217F)

### **TRADEMARKS**

The VMIC logo is a registered trademark of VMIC. Windows NT is a registered trademark of Microsoft Corporation. Other registered trademarks are the property of their respective owners.

Figure 1. VMIPCI-3322 Functional Block Diagram