## SBS DAQ

E. Cisbani

INFN Rome &

Italian Institute of Health

SBS DOE Review

7/Nov/2016 - Georgetown

Contributions from:

- Dasuni Adikamar

- Alexandre Camsonne

- Mark Jones

- Paolo Musico

- Andrew Puckett

• ...

#### Outline

- GEP Event Rate

- Trigger and DAQ

- Fastbus for SBS: performance

- GEM readout

Overview at SBS Meeting 20/Oct/2016 presentation is in progress ...

#### Main guidelines

- Reuse available equipment (Fastbus) to reduce cost

- Exploit JLab CODA3 VME hardware largely based on powerful FPGA

- >100k GEM channels need processing in hardware

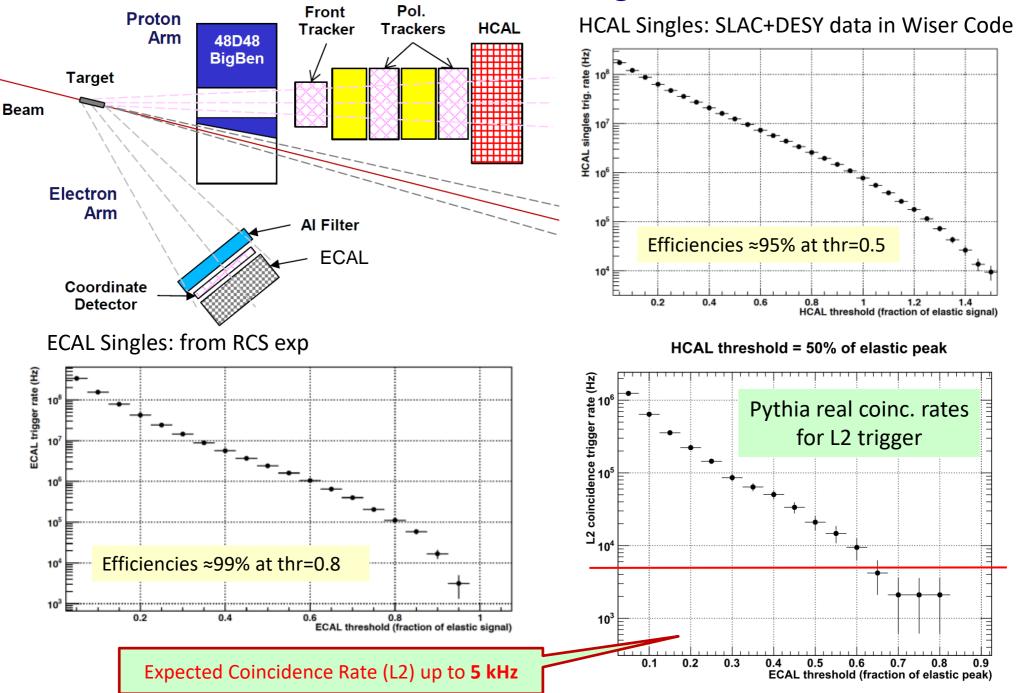

### **GEp - Most Demanding DAQ Rate**

## **DAQ Concepts**

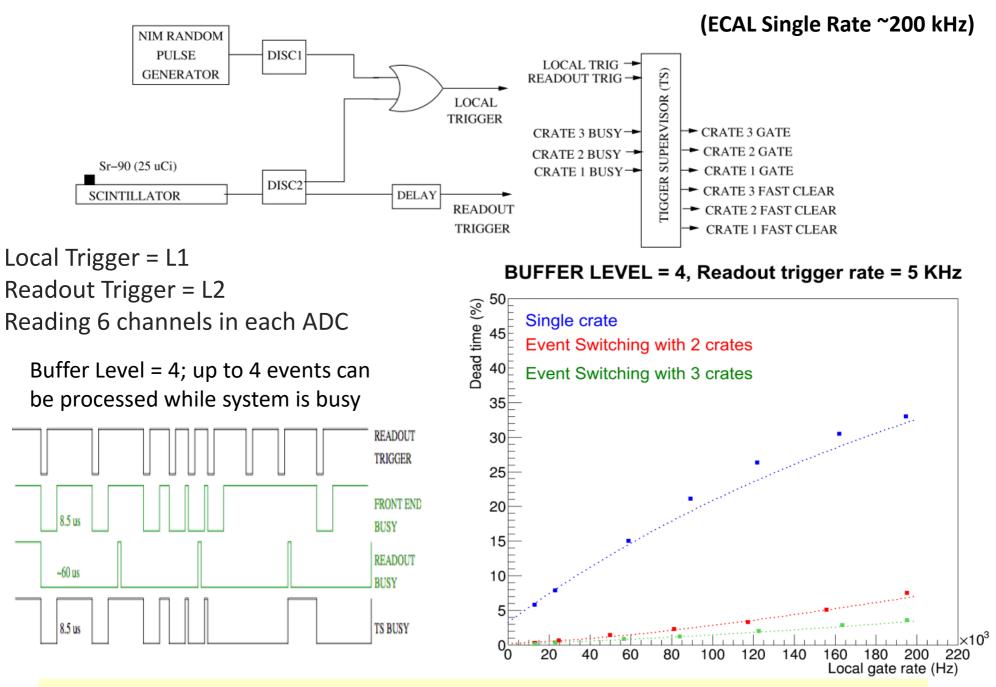

- Hybrid Fastbus & Pipelined VME+Optical Fiber Electronics

- Level 1 Trigger

- originated by the ECAL electron arm (~200 kHz rate)

- latency ~100 ns (analog sum and discrimination)

- GATE for Fastbus and non-pipelined components (ECAL)

#### Level 2 Trigger

originated by electron ECAL & proton HCAL & FPGA-based coincidence logic using elastic e-p angular constraints

#### *⇒* ≤5 *kHz DAQ rate*

- latency  $\leq$  1.8 µs (formation 0.8 µs max + fast clear timeout ~1 µs)

- Fastbus & VME Fast CLEAR after L2 timeout ⇒ ≈10% electronics dead time

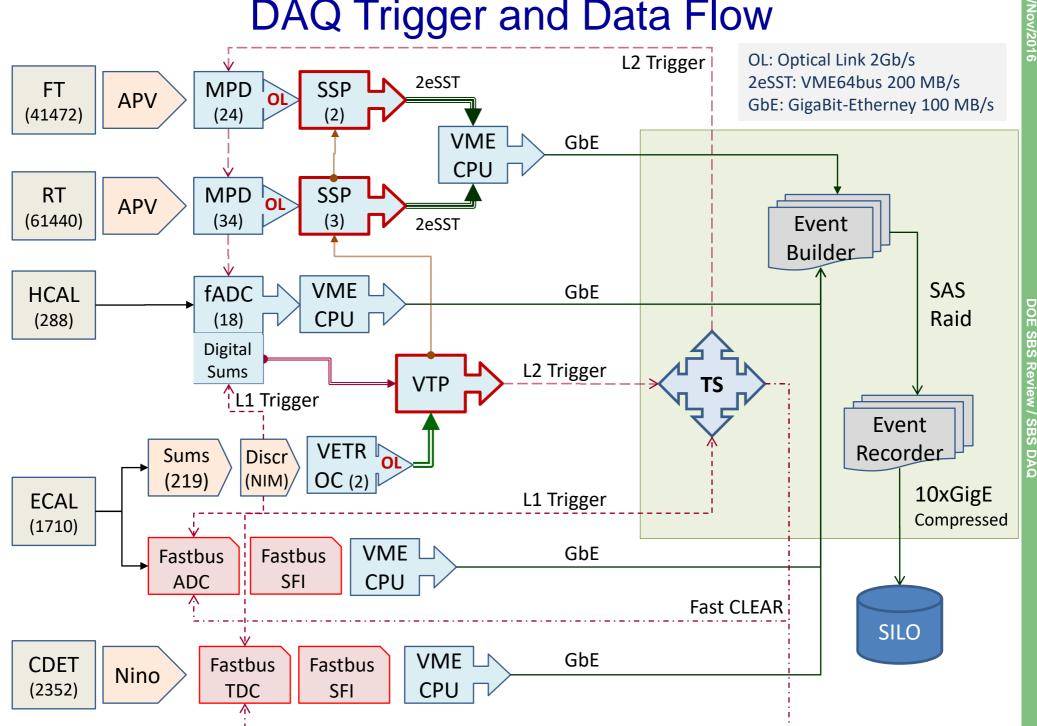

## DAQ Trigger and Data Flow

Many details aready implemented and/or tested. Overall picture finalized; small scale test in progress

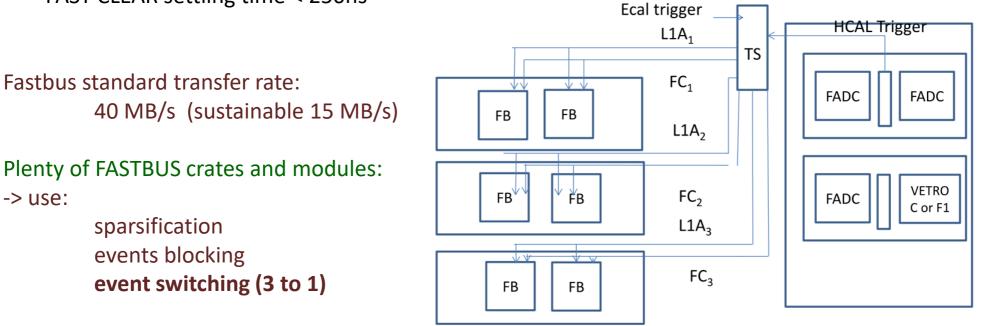

## FASTBUS for ECAL and CDET

Struck Fastbus Interface (SFI) is the Fastbus Master (18 available at JLab)

- Allows control the Fastbus modules through any VME CPU (Intel or old vxworks)

- Has slot for standard JLab Trigger Interface Module

New TI's for all ECAL e CDET Fastbus crates

Amplitude: 64 channel Lecroy ADC 1881M (113 available at JLab)

- $9\mu s$  encoding time in 12 bit resolution and  $12\mu s$  in 13 bit resolution.

- use the FAST CLEAR feature: module is ready to accept another event after 2µs.

Time: 96 channel Lecroy TDC 1877s (236 available at JLab)

- Built-in Data Zero Suppression and Data Compaction (sparsification)

- Capable of multihit with an event buffer of 8 events.

- Encoding time 1.7  $\mu s$  plus 50 ns per hit per channel giving a maximum encoding time of 78  $\mu s.$

- FAST CLEAR settling time < 250ns

## ECAL/Fastbus – Event Switching Dead Time Study

Fastbus tested readout guarantees deadtime well below 10% at maximum expected rate

/Nov/2016

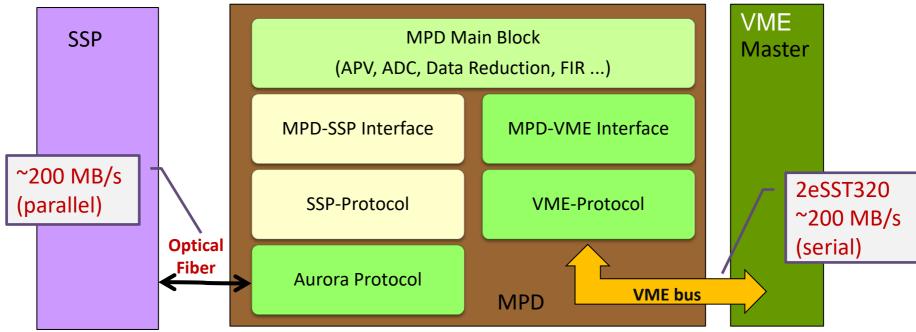

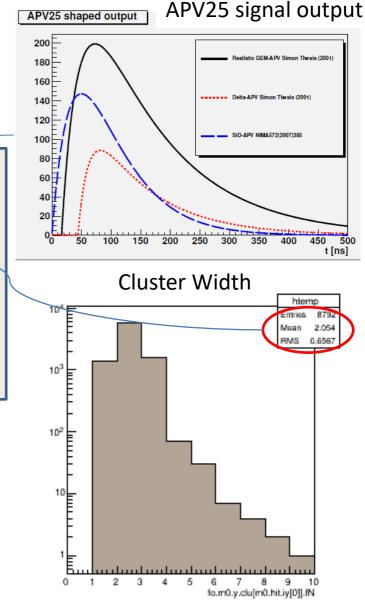

## **GEM – Readout Electronics**

- 128 analog ch / APV25 ASIC

- 3.4 µs trigger latency (analog pipeline)

- Capable of sampling signal at 40 MHz

- Multiplexed analog output (100 kHz readout rate)

- Up to 16 APV25 cards (2048 chs) on a single MPD (parallel readout)

- Altera Arriga GX FPGA / RAM: DDR2 (128 MB)

- Optical Fiber Link interface (Aurora ~2 Gb/s peak)

- 110 MHz system clock and Front panel coax clock

- Used HDMI-A for analog and digital signals

- VME/32, VME64, VME64-VXS compliant (up to 200 MB/s peak)

- 4 high speed line on the VXS available for data transfer

- Firmware v. 4.0 (74% resources):

- Finite-Impulse-Response Filter (16 parameters)

- Zero Suppression (sparse readout)

- Common mode and pedestal subtraction

- Remore reconfiguration

- ~2 ns trigger time resolution

- VME / Optical Fiber simultaneous implementation

|               | Channels | APV25 | MPDs |

|---------------|----------|-------|------|

| Front Tracker | 41472    | 324   | 24   |

| Rear Tracker  | 61440    | 480   | 34   |

## MPD Status (version 4.0)

- All VME cycles tested (using a STRUCK SIS-3104 controller) and in JLab/CODA DAQ except 2eSST

- Measured data transfer speeds agree with simulations

- 2eSST in JLab shows data misalignments

- Optical link MPD SSP:

- MPD can be configured by SSP; data transfer still suffer some misalignments but all data words are present

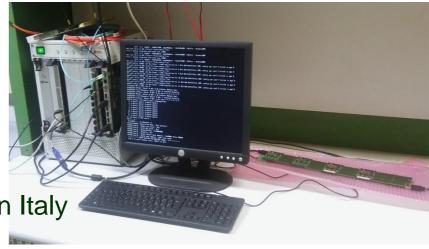

- CODA system (Intel CPU + SSP) now running in Italy

- deep test VME64x MPD SSP is in progress

Nov/2016

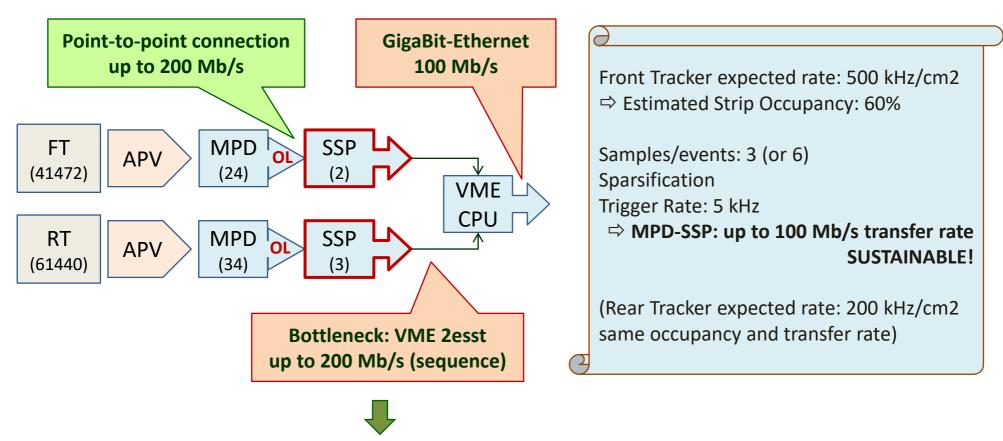

## GEp: GEM data rate

Need data processing on SSP (and MPD) to reduce data by factor of ~10 (<30% dead time):

- Time-Correlation (signal width 250 ns can be reduced to less than 80 ns  $\rightarrow$  factor 3)

- e-p geometrical constraints (ECAL HCAL alignment  $\rightarrow$  factor 4.5)

- x/y clustering with charge/time correlation ... to be investigated

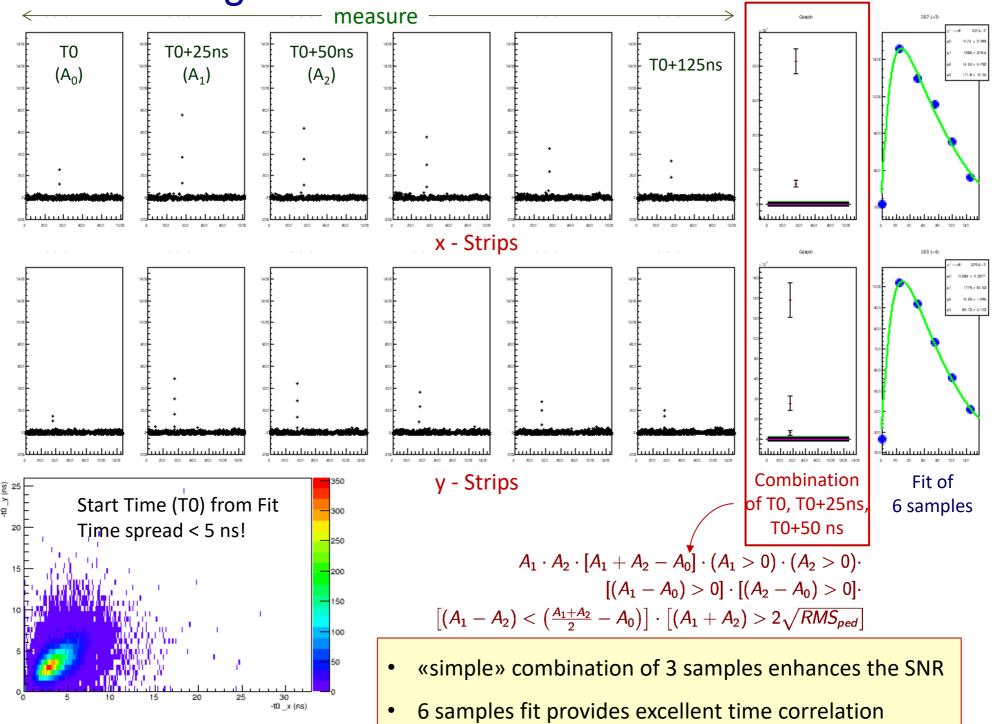

### GEM Signal Deconvolution / 2014 Test Data

DOE SBS

**Review / SBS DAQ**

DOE SBS

SBS DAQ

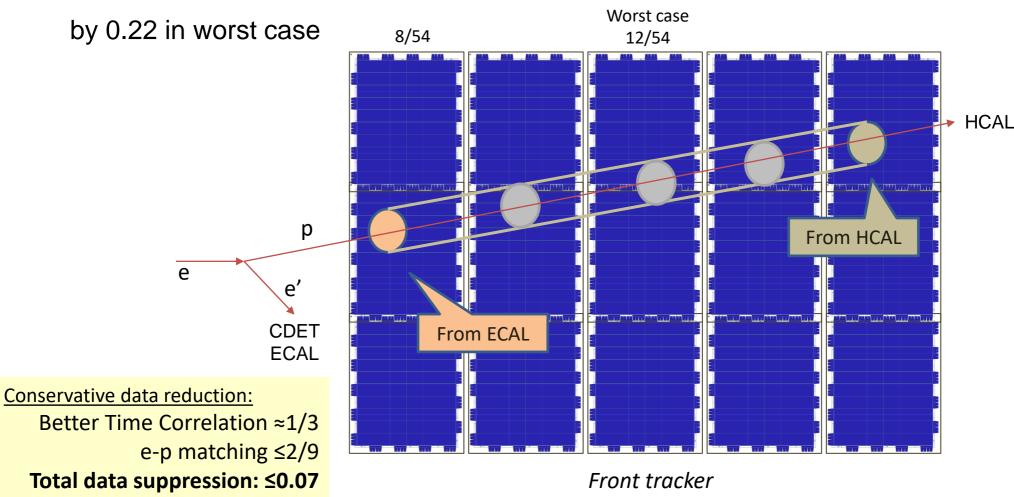

## GEM / geometrical e-p matching

- VTP has information on e-p geometrical matching by ECAL and HCAL

- VTP send a pattern to GEM-(MPD)SSP's (  $\approx$  41 bytes \* 5 kHz )

- (MPD)SSP filter APVs data streams according to geometrical matching (1

- APV = 5 cm ), e.g. 4 APV along each axis (20 cm x 20 cm) suppress FT data

## DAQ: Work force (FTE)

|                            | FTE | Coordination | VME<br>DAQ | Fastbus | HCAL<br>Trigger | GEM<br>MPD | BigBite |

|----------------------------|-----|--------------|------------|---------|-----------------|------------|---------|

| A. Camsonne/JLab           |     | X            |            |         | Х               | Х          |         |

| M. Jones/JLab              | 0.1 |              |            | Х       |                 |            |         |

| D. Adikaram/Hall A PostDoc | 0.4 |              |            | Х       |                 |            |         |

| J. Gu/JLab                 | 0.1 |              |            | Х       |                 |            |         |

| S. Malace/NSU PostDoc      | 0.4 |              |            | Х       |                 |            |         |

| B. Moffit/JLab             | 0.1 |              | Х          | Х       |                 | Х          |         |

| B. Raydo/JLab              | 0.2 |              | Х          |         | Х               | Х          |         |

| S. Riordan/SBU             |     |              |            |         |                 | ?          |         |

| D. Di/PhD Student          | 1.0 |              |            |         |                 | Х          |         |

| E. Cisbani/INFN Rome       | 0.2 |              |            |         |                 | Х          |         |

| P. Musico/INFN Genoa       | 0.2 |              |            |         |                 | Х          |         |

| E. McLelan                 |     |              |            | Х       |                 |            | X       |

## DAQ: Short Term plan

- Parassitic test run during DVCS/GMp experiment

- Small scale system running in Hall A

- GEM/MPD-SSP/CODA Integration

- GEM CODA decoding under finalization

- MPD-SSP optical link works: bug fixing busted by available system in Italy

- Algorithms

- Ongoing study of GEM firmware data processing for time correlation and e-p matching

## Summary

#### **Trigger:**

• Two Levels; exploiting powerful FPGA real-time processing to reduce readout rate

#### Fastbus:

• Tested: sparsification, event buffering and crate switching; dead time well below 10%

#### VME:

- FADC amplitudes and time information for HCAL

- MPD + Optical Link + SSP works, alignment bugs expected to be fixed soon

- "Smart" processing in MPD and/or SSP to reduce data by 1/10 addressed and candidate for solutions identified

#### JLab CODA3

hardware/software framework integration largely completed

## backup

## New TS Firmware

- New firmware implementing event switching in the TS up to 4 branches

- Inputs:

- T1 Lvl 1 trigger, T2 Lvl2,

- 4 busy inputs, 4 fast L1, 4 Fast Clear output

- A single TS for synchronization

- Single data stream

- Fully compatible with event blocking

- New TIs for Fastbus

- 250 MHz clock distribution on fiber : absolute timestamp and counters on the new TI (replace scalers)

## VETROC

- VETROC : VXS Electron Trigger Read Out Controller

- Logic input and output pipeline board up to 192 channels

- Optical link and VXS port to communicate with other pipelined electronics

- FPGA programmable logic

- Will be used to input the ECAL sum to the trigger module for geometrical matching of ECAL and HCAL

- Prototype being tested

- 2 boards procured for SBS

## VTP

- VTP : VXS Trigger Processor

- New generation of Trigger Processor

- Larger FPGA than previous CTP and GTP

- Will do HCAL clustering and geometrical matching with ECAL

- Allow readout of modules through VXS increasing the bandwidth to 16x8 Gbit /s could be used for FADC fast readout or SSP if required

- On board processor

- Board received, firmware and interface are being implemented

## 7/Nov/2016

## DAQ configuration for SBS GEP experiment

| GEp Detectors                  | Channels | Readout    | Type    |

|--------------------------------|----------|------------|---------|

| <u>SBS Proton arm</u>          |          |            |         |

| Front tracker (6 GEM chambers) | 41,472   | APV25 MPD  | VME     |

| Rear tracker (10 GEM chambers) | 61,440   | APV25 MPD  | VME     |

| HCAL                           | 288      | FADC $250$ | VME     |

| Electron arm                   |          |            |         |

| ECAL                           | 1710     | ADCs 1881M | Fastbus |

| ECAL sums                      | 219      | TDCs 1877S | Fastbus |

| CDET                           | 2688     | TDCs 1877S | Fastbus |

- Reuse the NIM and Fastbus equipment already available at JLab

- Lot's of channels on VME, Fiber Optics and new CODA

Additional components (modules):

- SSP: Sub-System Processor

- TS: Trigger Supervisor / TI: Trigger Interface

- VETROC: Trigger and Digital Readout

- VTP: VXS-Trigger Processor

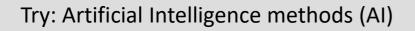

## APV Signal Analysis for Hit Discrimination in Firmware

## GOAL: Find a simple and robust function (to be implemented in firmware) that can discriminate real hits from background

One PhD student (L. Re) workin on that in Catania/Italy Supervisioned by M. Russo

## GEp: GEM Data rate

| Tracker | Area of interest              | Rate,               | Strip pitch, | Strip occu- | Number of pseudo-   | Number of       |

|---------|-------------------------------|---------------------|--------------|-------------|---------------------|-----------------|

|         | for tracking, cm <sup>2</sup> | kHz/cm <sup>2</sup> | mm           | pancy, %    | Corresks per event  | strip planes    |

| First   | 0.20 x 18                     | 400                 | 0.4          | 13.5        | 1.652(10-2          | 12              |

| Second  | $2\pi \ 0.35^2$               | 130                 | 1.6          | 7.4         | 8.7 × 10- Stj       | m. <sup>8</sup> |

| Third   | $\pi$ 4.8 <sup>2</sup>        | 64                  | 1.6          | 3.6         | $5.2 	imes 10^{-4}$ | "ation          |

| BigCal  | $\pi \ 1.2^{2}$               | 173                 | 1            | 2.4         | $2.8 	imes 10^{-2}$ | 2               |

- Expected Hits Rate (Front Tracker): ~ 500 kHz/cm2

- GEM signal width:  $\sim$  250 ns

- Cluster width (MIP particles): 2.5 strips

- Strip Occupancy: 60%

- Samples/Events: 3

- Bits/Sample = 24 = 12 ADC + 7 CH-APV + 5 CH-ADC

- Trigger rate: 5 kHz

- MPD-SSP Transfer Rate: 45.2 MB/s (after sparsification)

200 kHz/cm2 Rear Tracker – same occupancy and transfer rate

SSP to DAQ-CPU data rate is 200 MB/s (VME bus)

→ require MPD/SSP=4 and SSP/VME64\_crate=1

FEASIBLE BUT NOT EFFORDABLE!

We shall connect up to 12 MPD to a single SSP

⇒ need data processing on SSP (and MPD), reduce data by factor of ~10 (<30% dead time)

Better Time-Correlation, e-p geometrical constraints, x/y clustering with charge/time correlation

## Data Storage

| ov/2016 |

|---------|

|         |

|               |             | Days | Data rate<br>MB/s | Seconds  | Total<br>data TB | Double  | LTO5 in \$ | LTO6 in \$ | LTO7 in \$ |

|---------------|-------------|------|-------------------|----------|------------------|---------|------------|------------|------------|

| E12-12-09-019 | GMN         | 25   | 1000              | 2160000  | 2160             | 4320    | 216000     | 129600     | 86400      |

| E12-09-016    | GEN         | 50   | 1000              | 4320000  | 4320             | 8640    | 432000     | 259200     | 172800     |

| E12-07-109    | GEP/G<br>MP | 45   | 1000              | 3888000  | 3888             | 7776    | 388800     | 233280     | 155520     |

| E12-09-018    | SIDIS       | 64   | 1000              | 5529600  | 5529.6           | 11059.2 | 552960     | 331776     | 221184     |

|               |             |      |                   |          |                  |         |            |            |            |

|               | Total       | 184  |                   | 15897600 | 15897.6          | 31795.2 | 1589760    | 953856     | 635904     |

| Actual days   | Actual      |      | Time in s         |          |                  |         |            |            |            |

|               | years       |      |                   |          |                  |         |            |            |            |

| 368           | 1.01        | 184  | 15897600          |          |                  |         |            | Total      | 635 K\$    |

(backup slide)

LTO7 since 2015 : 300 MB/s per arm (up to 15) and 6.25 TB per table uncompressed

Cost was divided by a factor of 2 : 500 MB/s reasonable, 1 GB/s doable if needed for about 635 K\$ of tape split over several years and cost expected to go down

Network link upgrade to 10 Gbit/s = 1.25 GB/s possible: possibility for L3 farm in computer center